Двоичный счетчик

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в качестве базового элемента в устройствах автоматики и вычислительной техники с повышенными требованиями к достоверности функционирования и эксплуатационной отказоустойчивости. Цель изобретения - повышение надежности двоичного счетчика - достигается за счет введения в его структуру резервного разряда, содержащего триггер 5.5, элемент И-НЕ, 2И-ИЛИ 18.4, элемент И 16.4 и два элемента ИЛИ 19.1 и 19.2, а также элементов ИЛИ/ИЛИ-НЕ 15,1-15,4, И 16.1-16.3, 2И-ИЛИ 18.1-18.3 и элементов 2И-ИЛИ-НЕ 17.1-17.3 с соответствующими связями, достигается автоматическая реконфигурация работоспособной структуры устройства. Кроме того, в триггер каждого разряда введены три элемента НЕ, элемент И и триггер-селектор с соответствующими конструктивными связями, которые представляют собой встроенные средства функционального контроля. В случае отказа одного из основных триггеров 5.1-5.4 на его выходе формируется сигнал Отказ и обеспечивается автоматическая перестройка работоспособной структуры. 3 ил. to С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я) Н 03 К 23/ ;-8

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ j

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4478552/21 (22) 25,08.88 (46) 15.10.91. Бюл. М 38 (72) А.Н.Пархоменко, В. В. Голубцов, В.С.Харламов и В,А.Захаров (53) 621.374.32(088.8) (56) Справочник. Применение интегральных микросхем в электронной вычислительной технике/ Под ред. Б.Н.Файзулаееа и Б.В.Тарабрина. M. Радио и связь, 1987, с.41, рис.3.34.

Авторское свидетельство СССР

N 1599988,,кл. Н 03 К 23/58, 1988. (54) ДВОИЧНЫЙ СЧЕТЧИК (57) Изобретение относится к импульсной технике и может быть использовано в качестве базового элемента в устройствах автоматики и вычислительной, техники с повышенными требованиями к достоверности функционирования и эксплуатационной

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники в качестве базового элемента с повышенной надежностью функционирования.

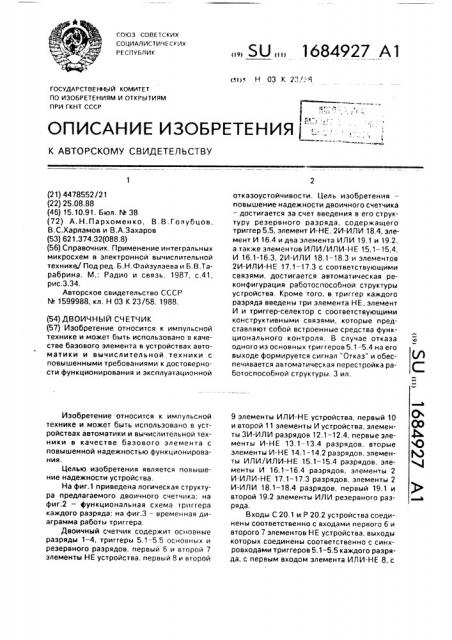

Целью изобретения является повышение надежности устройства, На фиг,1 приведена логическая структура предлагаемого двоичного счетчика; на фиг.2 — функциональная схема триггера каждого разряда; на фиг.3 — временная диаграмма работы триггера.

Двоичный счетчик содержит основные разряды 1 — 4, триггеры 5.1-5.5 основных и резервного разрядов. первый 6 и второй 7 элементы НЕ устройства, первый 8 и второй,, SU ÄÄ 1684927 А1 отказоустойчивости. Цель изобретения— повышение надежности двоичного счетчика — достигается за счет введения в его структуру резервного разряда, содержащего триггер 5.5, элемент И-НЕ, 2И-ИЛИ 18.4, элемент И 16.4 и два элемента ИЛИ 19,1 и 19.2, а также элементов ИЛИ/ИЛИ-НЕ 15,1 — 15,4, И 16.1-16.3, 2И-ИЛИ 18.1 — 18.3 и элементов

2И-ИЛИ-НЕ 17.1 — 17.3 с соответствующими связями, достигается автоматическая реконфигурация работоспособной структуры устройства. Кроме того, в триггер каждого разряда введены три элемента НЕ, элемент

И и триггер-селектор с соответствующими конструктивными связями, которые представляют собой встроенные средства функционального контроля. В случае отказа одного из основных триггеров 5.1-5.4 на его выходе формируется сигнал "Отказ" и обеспечивается автоматическая перестройка работоспособной структуры. 3 ил.

9 элементы ИЛИ-НЕ устройства, первый 10 и второй 11 элементы И устройства, элементы ЗИ-ИЛИ разрядов 12.1-12.4, первые элементы И-HE 13.1-13,4 разрядое, вторые элементы И-НЕ 14.1 — 14.2 разрядов, элементы ИЛИ/ИЛИ-НЕ 15.1 — 15.4 разрядов, элементы И 16.1-16.4 разрядов, элементы 2

И-ИЛИ-НЕ 17.1 — 17.3 разрядов, элементы 2

И-ИЛИ 18.1 — 18.4 разрядое, первый 19.1 и второй 19.2 элементы ИЛИ резервного разряда, Входы С 20.1 и Р 20.2 устройства соединены соответственно с входами первого 6 и второго 7 элементов НЕ устройства, выходы которых соединены соответственно с синхровходами триггеров 5,1 — 5.5 каждого разряда, с первым входом элемента ИЛИ-НЕ 8, с

1684927 первым входом элемента ИЛИ-НЕ 9 и с инверсным входом элемента ИЛИ-НЕ. Вход Ч

20.3 устройства соединен с вторыми входами элементов ИЛ И+1 Е 9 и И 10. Вход Р120.4 разрешения переноса устройства соединен с первым входом элемента И 11 и третьим входом элемента И 10, четвертый вход которого соединен с входом V> 20.5 управления режимом работы устройства. Информационные входы D,i-0.4 20,6-20.9 устройства соединены соответственно с вторыми входами первых групп входов соответствующих им элементов ЗИ-ИЛИ 12,1 — 12,4.

Выход элемента ИЛИ-НЕ 9 соединен с первыми входами первых групп входов элементов ЗИ-ИЛИ 12.1-12,4 каждого разряда и с вторым входом элемента ИЛ_#_-НЕ 8. выход которого соединен с вторыми входами третьих групп входов элементов ЗИ-ИЛИ каждого разряда. Выход элемента И 10 соединен с первыми входами вторых групп входов элементов ЗИ-ИЛИ 12.1 — 12,4 и элементов И-НЕ 13.1 — 13.4 каждого разряда, Выходы элементов И-НЕ 13.1 — 13.4 соединены с третьими входами третьих групп входов соответствующих элементов ЗИ-ИЛИ

12,1 — 12.4, выходы которых соединены соответственно с вторым входом элемента И-НЕ

14.1 и с первым входом первой группы входов элемента 2И-ИЛИ-НЕ 17,1, с первым входом второй группы входов элемента 2ИИЛИ-НЕ 17,1 и с перьым входом первой группы входов элемента 2И-ИЛИ-НЕ 17,2, с первым входом второй группы входов элемента 2И-ИЛИ-НЕ 17,2 и с первым входом первой группы входов элемента 2И-ИЛИНЕ 17.3, с первым входом второй группы входов элемента 2И-ИЛИ-НЕ 17,3 и с первым входом элемента И-НЕ 14.2.

Выход элемента И-НЕ 14.1 соединен с инверсным О-входом триггегра 5.1, прямой выход которого соединен с первым входом первой группы входов элемента 2И-ИЛИ

18.1. Выход F "Отказ" триггера 5.1 соединен с входами элемента ИЛИ/ИЛИ-НЕ 15.1, прямой и инверсный выходы которого соединены соответственно с первым входом второй группы входов элемента 2И-ИЛИ

18.1, с вторым входом первой группы входов элемента 2И-ИЛИ-HE 17,1 и с вторыми входами элементов И 16,1 и ИЛИ/ИЛИ-НЕ

15.2, с первым входом элемента И-НЕ 14.1 и с вторым входом первой группы входов элемента 2И-ИЛИ 18.1.

Выход элемента 2И-ИЛИ-НЕ 17,1 соединен с инверсным 0-входом триггера 5,2, прямой вход которого соединен с вторым входом второй группы входов элемента 2ИИЛИ 18.1 и с первым входом первой группы входов элемента 2И-ИЛИ 18.2. Выход F "От5

55 каз" триггера 5.2 соединен с первыми входами элементов И 16.2 и ИЛИ/ИЛИ-НЕ 15.2.

Выход элемента И 16.1 соединен с первым входом элемента ИЛИ 19.1, Прямой выход элемента ИЛИ/ИЛИ-НЕ 15.2 соединен с первым входом второй группы входов элемента 2И-ИЛИ 18.2, с вторым входом первой группы входов элемента 2И-ИЛИ-НЕ

17.2 и с вторыми входами элементов И 16.2 и ИЛИ/ИЛИ-НЕ 15.3. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 15.2 соединен с вторым входом второй группы входов элемента

2И-ИЛИ-НЕ 17.1 и с вторым входом первой группы входов элемента 2И-ИЛИ 18.2.

Выход элемента 2И-ИЛИ-НЕ 17.2 соединен с инверсным D-входом триггера 5.3, прямой выход которого соединен с вторым входом второй группы входов элемента 2ИИЛИ-НЕ 18,2 и с первым входом первой группы входов элемента 2И-ИЛИ 18.3, Выход F "Отказ" триггера 5.3 соединен с первыми входами элементов И 16.2 и

ИЛИ/ИЛИ-НЕ 15,3. Выход элемента И 16.3 соединен с вторым входом элемента

ИЛИ 19.1. Инверсный выход элемента

ИЛИ/ИЛИ-НЕ 15,3 соединен с вторым входом второй группы входов элемента 2ИИЛИ-НЕ 17.2 и с вторым входом первой группы входов элемента 2И-ИЛИ 18.3, Прямой выход элемента ИЛИ/ИЛИ-НЕ 15,3 соединен с первым входом второй группы входов элемента 2И-ИЛИ 18.3, с вторым входом первой группы входов элемента 2ИИЛИ-НЕ 17.3 и с вторыми входами элементов И 16.3 и ИЛИ/ИЛИ-НЕ 15.4, Выход элемента 2И-ИЛИ-НЕ 17,3 соединен с инверсным D-входом триггера 5,4, прямой выход которого соединен с вторым входом второй группы входов элемента 2ИИЛИ 18.3 и с первым входом первой группы входов элемента 2И-ИЛИ 18.4. Выход F ""Отказ" триггера 5.4 соединен с первыми входами элементов И 16.3 и ИЛИ/ИЛИ-НЕ 15.4, Выход элемента И 16.3 соединен с третьим входом элемента ИЛИ 19.1. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 15,4 соединен с вторым входом второй группы входов элемента 2И-ИЛИ-НЕ 17.3 и с вторым входом первой группы входов элемента 2И-ИЛИ

18.4. Прямой выход элемента ИЛИ/ИЛИ-НЕ

15.4 соединен с первым входом второй группы входов элемента 2И-ИЛИ 18.4, с вторым входом элемента И-НЕ 14,2 и с вторыми входами элементов И 16.4 и ИЛИ 19,2, Выход элемента И-НЕ 14.2 соединен с инверсным 0-входом триггера 5,5. прямой выход которого соединен с вторым входом второй группы входов элемента 2И-ИЛИ

18,4. Выход F ""Отказ" триггера 5,5 соединен с первыми входами элементов И 16.4 и ИЛИ

1684927

19.2. Выход элемента И 16.4 соединен с четвертым входом элемента ИЛИ 19.1, выход которого является выходом "Отказ устройства. Выход элемента ИЛИ 19.2 является выходом "Частичный отказ" устройства, Выход элемента 2И-ИЛИ 18.1 является первым информационным выходом Ql устройства и соединен с вторым входом элемента И 11, с инверсным входом второй и с первым входом третьей групп входов элемента ЗИ-ИЛИ 12.1, с вторыми входами вторых групп входов элементов ЗИ-ИЛИ

12,2-12,4 и с вторыми входами элементов

И-НЕ 13.2 — 13.4.

Выход элемента 2И-ИЛИ 18.2 является вторым информационным выходом Ог устройства и соединен с третьим входом элемента И 11, с инверсным входом второй и с первым входом третьей групп входов элемента ЗИ-ИЛИ 12.2, с третьими входами вторых групп входов элементов ЗИ-ИЛИ

12,3 и 12.4 и с третьими входами элементов

И-НЕ 13.3 и 13.4.

Выход элемента 2И-ИЛИ 18.3 является третьим информационным выходом Оз устройства и соединен с четвертым входом элемента И 11, с инверсным входом второй и с первым входом третьей групп входов элемента ЗИ-ИЛИ 12.3, с четвертым входом второй группы входов элемента ЗИ-ИЛИ

12 4 и с четвертым входом элемента И-НЕ

13.4, Выход элемента 2И-ИЛИ 18,4 является четвертым информационным выходом 04 устройства и соединен с пятым входом элемента И 11, с инверсным входом второй и с первым входом третьей групп входов элемента ЗИ-ИЛИ 12.4. Выход элемента И 11 является выходом Рр переноса устройства.

Триггер каждого разряда (см. фиг.2) содержит первый элемент НЕ 21, элементы

И-НЕ 22 — 29, второй 30, третий 31, четвертый 32 элементы НЕ, элемент И 33, пятый 34 элемент НЕ и триггер-селектор 35.

Вход D триггера каждого разряда соединен с входом элемента НЕ 21, выход которого соединен с входом элемента И-НЕ

22, второй и третий входы которого соединены соответственно с входами V и С триггера, которые дополнительно соединены с входом элемента И-НЕ 23 и с входом элемента И 33. с входом элемента И-НЕ 23 и с входом элемента Н Е 30.

Выход элемента НЕ 21 соединен с входом элемента НЕ 34 и с входом четвертой группы входов триггера-селектора 35. Выход элемента И-НЕ 22 соединен с входом

45 элемента И-НЕ 24 и с входом элемента l1-! 1 Е

23, выход которого соединен с входом элем,;;-:та И НЕ 25 Вы о", элемента НЕ 30 соединен с вторыми .-:к дами элементов И-HE

26 и 27, с вход-.-," первой и второй групп входов триггера- ек-ора и с входом элемента НЕ 31 вы.од которо о соединен c входом элемента И 33. Выход элемента И 33 соединен с входами третьей и четвертой групп входов триггера-селектора 35 и с входом элемента НЕ 32. выход которого соединен с входами первой и второй групп входов триггера-селекгора 35. Выход элемента НЕ

34 соединен с sxo,»;ýì третьей группы входов триггера-селе 1ора 35, первый вход пятой группы входов которого соединен с входом Р установки в исходное состояние средств функционального контроля триггера.

Выход элемента И-НЕ 24 соединен с входом элементов И-НЕ 25 и 26 и с входами второй и четвертой групп входов триггераселектора 35. Выход элемента И-НЕ 25 соединен с входом элементов И-НЕ 24 и 27 и с входами первой и третьей групп входов триггера-селектора 35. Выходы элементов

И-НЕ 26 и 27 соединены соответственно с входами элементов И-НЕ 28 и 29.

Выход элемента И-НЕ 28 является прямым выходом триггера и соединен с входом элемента И-НЕ 29 и с входом первой группы входов триггера-селектора 35. Выход элемента И-НЕ 29 является инверсным выходом триггера и соединен с входом элемента

И-НЕ 28 и с входом второй группы входов триггера-селектора 35, выход которого является выходом "Отказ" триггера и соединен с вторым входом пятой группы входов триггера-селектора 35.

Триггер-селектор может быть реализован, например, на элементе И-ИЛИ с пятью группами входов И, из которых четыре являются группами входов установки "в единицу", а первый, второй входы пятой группы входов И элемента И-ИЛИ соединены соответственно со входом установки нуля триггера-селектора и с входом элемента И-ИЛИ, выход которого является выходом триггераселектора 35.

В процессе своего функционирования триггер каждого разряда контролируется встроенными средствами функционального контроля, обеспечивая при этом более достоверную информацию на выходах каждого триггера, Рассмотрим функциональное назначение и прлнцип работы триггера каждого разр;.„з.

1684927

55

Элементы И-НЕ 22-25 образуют схему основного триггера, а элементы И-НЕ 26-29 — схему вспомогательного триггера.

Элемент НЕ 30 предназначен для организации двухтактного режима работы триггера при наличии одного синхровхода — С.

Кроме того, на выходе элемента НЕ 30 вырабатывается сигнал сравнения сигналов на противоположных плечах (выходах) основного и вспомогательного триггеров (см. фиг.2, точка А и О, точка А и О) в режиме хранения информации.

Элемент НЕ 32 формирует функции V:С через время 4Тср срабатывания элементов

НЕ 30 и 31, элемента И 33, а также самого элемента НЕ 32 с момента поступления положительного фронта синхроимпульса на Свходе триггера, который является сигналом сравнения для первой и второй групп входов триггера-селектора 35, контролирующего правильность срабатывания логических элементов второй ступени (вспомогател ьного триггера) триггера.

Элементы НЕ 21, 31 и 34 осуществляют инвертирование сигналов на С и D-входах триггера соответственно, необходимых для формирования соответствующих аргументов функционала контроля.

Элемент И 33 осущесгвляет формирование функции V С через время ЗТср срабатывания элементов НЕ 30 и 31, а также самого элемента И 33 с момента появления отрицательного фронта синхроимпульса на С-входе триггера и формирует на своем выходе сигнал сравнения для третьей и четвертой групп входов триггера-селектора 35, контролирующего в этом случае правильность срабатывания логических элементов первой ступени (основного триггера) триггера каждого разряда.

Триггер-селектор 35 осуществляет на своих группах входов контроль правильности срабатывания всех логических элементов структуры триггера. В случае нарушения логики функционирования (отказ какого-либо логического элемента структуры триггера) на выходе триггера-селектора 35 формируется сигнал "Отказ", который посредством своей обратной связи через пятую группу входов осуществляет так называемый эффект самозахвата, т.е. устанавливается в устойчивое состояние логической единицы.

В общем случае на входах триггера-селектора 35 реализуется функционал отказа, который можно представить следующим аналитическим выражением:

F = (V С) 0 А V(V С) D . А V(V Ñ)

А QV(V С) А О, (1) где V — единичное состояние сигнала на входе триггера;

С вЂ” единичное состояние сигнала на синхровходе триггера;

D — единичное состояние сигнала на 0входе триггера;

А, А — единичное и нулевое состояние сигналов сответственно в точках А и А на фиг,2;

О, Q — состояние сигнала на прямом и инверсном выходах триггера, Триггер каждого разряда работает следующим образом.

После включения питания на Rc-вход триггера (см, фиг.2) подается нулевой уровень сигнала для установки в исходное состояние средств функционального контроля, так как в силу случайного характера переходных процессов во время включения питания триггер-селектор 35 может установиться в единичное состояние, соответствующее формированию сигнала "Отказ" триггера в целом.

Далее при исправном состоянии всех логических элементов работа триггера каждого разряда подчиняется (соответствует) закону функционирования, приведенному в

coKpBlL ной табл. переходов триггера каждого разряда.

В процессе своего функционирования первая ступень триггера подчиняется закону. представленному следующим аналитическим выражением: ((V С) D A=1)V((V С) О A=1),(2) где Ч вЂ” состояние сигнала на V-входе триггера;

С вЂ” единичное состояние сигнала на синхровходе триггера; . D, D — единичное и нулевое соответственно состояния сигналов íà D-входе триггера;

А. А — единичное и нулевое соответственно состояния сигналов в точках А и А на фиг.2 триггера.

За выполнением условий выражения (2) следят третья и четвертая группы входов триггера-селектора 35.

В процессе своего функционирования вторая ступень (вспомогательный триггер) триггера каждого разряда подчиняется закону, который можно представить следующим аналитическим выражением:

16819; 7 ((V С) А а =1)Ч ((V С) А а =- Il,(3) где V С вЂ” единичное состояние сиг» л;,«э выходе элемента НЕ 32;

О, 0 — состояния сигналов на прямом V инверсном соответственно выходах триггера каждого разряда.

3а выполнением условий выражения (3)

СЛЕДЯТ ПЕРВаЯ и ВтОРаЯ ГРУППЫ ВХОДОВ тРИГгера-селектора 35.

Функционал отказа любого из логических элементов первой сэупени (основно-о триггера), реализованных в техническом решении триггера каждого разряда, можно представи ь следующим. аналитическим выражением:

F=(V С) D А V(V С) DА, (4) В случае наруше1 ия условий функцио»ирования, представленных в выраженли (2), на выходе триггера-селектора 35 уже в момент срабатывания элементов первой ступени вырабатывается сигнал "Отказ" эриггера каждого разряда, Функционал отказа люб01о из логических элементов втооой ступe«è (rlcoohlnraтельного триггера), реализова««ый в техническом решении триггера каждого разряда, можно предс авить выражением

F =(V С) А . Q V(V С) А G. (5) В случае нарушенле условий сЬункционирования, представленн .Ix в выражениl (3). на выходе триггера-селектооа 35 -,акже выра батывается сигнал "Отказ" триггера каждсго разряда.

РаССМОтРИМ rIOCnePO атЕЛЬ«ОСтЬ СРабатывания всех элементов ло ической структуры предлагаемого тоиггера в его трех основных реж>лмах функционирования: хранение, установка "1" и установка

"0".

В режиме "Установка 1" (табл,1, п.4) по

0-входу с поступлением положительного фронта синхросигнала на С-вход триггера на выходе элемента И-НЕ ?2 через впемя

T>-rI срабатывания элемента И-НЕ 22 установится сигнал логического нуля, Следовательно, через время 2Т,Л срабать1вание с момента поступления г>оложительного фронта сигнал на С-вход на выходах второго и третьего элементов И-НЕ 23 и 24 установятся сигHaflbl логической единицы и через время ЗТсг, срабатывания на выходе четвертого элемента И-HF. 25 — сигнал логического нуля, Таким образом, через время ЗТ„-1, е точке А (OM. фиг.1) будет ycTa«nef!e«o cocTor>

?0

3е

4I;

4r>

5G

55 яние ло1ическои единицы, а в Iuчке А::О ,;:пч>1. "О . ;"« ro нуля. Ко«троль пра

ЧП,;, . П "IГ-, h, НV - . ЭЛ>,"!ITÃ В !! PP.О!1 с" .:.; "; . g . :;;с:.01,э .;,Qla o.,:;åñrел-.,; -,, с;робо;-;, ah«e«vя c выхода эле лг I! r;; И „ .". кгп,, и:явл»с п.я также ч,-.påç в,.е1.1 ЗТ.-р .",-б" эа«11я af e ентов НЕ 30, 3, и . асмо>о эле та И 33. Если r! ходе кон .1ля будет вып элнено условие (2), то третья и четвестл руч-пы входов триггера селектора 35 не про-,с ят на выход его сиг«ал логичесl cé ели 1ицы При нарушении ал; 01->итма Pyl«!:I; 1ирован 1я злемен; ами первой ступени, т.. вы полнится условие (4), на выходе триггера-селектора 35 вырабатывается сиг>IafI логи1ескои ед1н1>цы,который

-Iepea пятую группу входов устанавливает гр11г1ео-селектор 35 в устойчивое состояние логической единицы, сигнализи;-уя об отказе первпи ступени триггера любого из разрядов

C приходом на С-вход Tp!11repa отрицатель«ОГОэ ф рÎнта сиHхрОимпgëьсэ сОстоf>ние первой ступени передаегся во вторую ступень, т е пятый элемент И НЕ 26 ycra«0в11тся rI состояние логическо1о нуля, а шее Ои эле,"1е»т И НЕ 27 ос а 1ется в состоя»!1и ло!11vеской ед11! ицы на своем в ы хОg"!е.

Следоват льно. через времч ЗТ-„сраб.этыван> я с моменэа поступленич отрицательного QpoIITa синхроимпульса на выходе седьмого элемента И-НЕ 23 установится сигнал ло;ической единицы, а 1срез время

4Т, л- На выходе элемента И-НЕ 29 — си нал ло I«eclloro нуля. Кон гроль правильности срабатывания логи«вских элементов в1орой с1упени произеод111ся стробом сравнения, которы11 появчяеэся на ->ыходе элемента НЕ

32 >врез воемя 41;,, срабатывания с h10MIH

1а п>оявчения Отрица гель«ого фрон>а на с1нхоовходе триггера. При выполнении условий (3) на Bhlходе триггера-селектора 35 сигнал Отказ" не сформируется В противном cny lae, т.е при выполнении условия (5), «а elo выходе будет сформ1рован сигнал

"Отказ" одного или нескольких логических

aë .менэов втс рой ступени три1гера.

Б pi ж11ме Уста«овка 0 (табл.1 п.5) по

Б входу с приходом положиTåëü«îl о фронта с11нхросигнала на выходе элеменга И-HF. 22 устэновитсч 011гнал логической ед;1ницы, а

«а выходе элеменэа I/1 ÍI:- 23 — сигнал логичес> ого нуля, который через время 2Т>.р с паба rl! г>а ния с МО 1ентд поя член ия полок11- льного фрон а синхроимпульса приведеr к форм. рован11ю на выходе элемента

И-Н Е 24 сигнала ло-.ической единиць, Через

IIpe:.1ÿ 3 г>;, «а вь1хс,:, элемента И-НЕ 24 будет

1>срм;1оэвпн с ° г»=:л огического нуля. Контроль Эра=.,;,",ьностл срабатывания логиче1684927

12 ских элементов первой ступени будет проведен на входах третьей и четвертой групп входов триггера-селектора 35 сигналом сравнения с выхода элемента И 33, который будет сформирован через время ЗТ р срабатывания элементов НЕ 30 и 31, а также самого элемента И 33. При выполнении условий (2) сигнал "Отказ" на выходе триггера-селектора 35 не появится, в противном случае он будет сформирован, сигнализируя об отказе одного или нескольких логических элементов первой ступени триггера.

Функционирование и контроль правильности срабатывания логических элементов второй ступени производится следующим образом, При появлении на синхровходе триггера отрицательного фронта синхросигнала состояние основного триггера (первой ступени) будет передано во вторую ступень по следующей логической ветви: через 2Т р на выходе элемента

И-НЕ 27 будет сформирован сигнал логического нуля. Через время ЗТср на выходе элемента И-НЕ 29 — сигнал логической единицы и через время 4Тср на выходе элемента ИНЕ 28 — сигнал логического нуля. Контроль правильности срабатывания будет произведен сигналом сравнения с выхода элемента

НЕ 32, который будет сформирован также через время 4Tср срабатывания элементов

НЕ 30, 31, И 33 и самого элемента НЕ 32.

При выполнении условий (3) сигнал "Отказ" на выходе триггера-селектора 35 сформирован не будет, В противном случае, т.е, при выполнении условий (5), сигнал "Отказ" формируется на выходе триггера-селектора

35, сигнализируя об отказе одного или нескольких логических элементов второй ступени триггера.

В режиме хранения (табл.1, п,7), т.е. при наличии нулевого потенциала на синх ровходе триггера, с выходов элементов И-НЕ 22 и

23 на входы элементов И-HE 24 и 25 поступают сигналы логической единицы, подтверждая предыдущее состояние триггера первой ступени. С выходов элементов И-НЕ

26 и 27 на входы элементов И-НЕ 28 и 29 также поступают сигналы логической единицы, подтверждая предыдущее состояние триггера второй ступени.

В этом случае контроль правильности хранения предыдущего состояния производится следующим образом. Через время Т р срабатывания элемента НЕ 30 производится сравнение состояний в точке А с состоянием сигнала на прямом выходе триггера и в точке А с состоянием сигнала на инверсном выходе триггера. Такое же сравнение производится через время 4Тср с момента появления сигнала логического нуля на син5

55 хровходе триггера стробом срэвне .ия с выхода элемента НЕ 32, Функционирование и контроль правильности срабатывания логических элементов структуры триггера каждого разряда в остальных режимах его функционирования (табл., п.п.2.3 и 7) производится аналогичным образом.

Таким образом, в процессе подсчета импульсов триггер каждого разряда непрерывно контролируется на правильностьсрабатывания и, в случае отказа формирует на своем выходе "Отказ", сигнал высокого логического уровня.

Двоичный счетчик, содержащий в каждом разряде вышеописанный триггер, работает следующим образом, Для установки двоичного счетчика в исходное состояние на вход Rp устройства подают cv ãíàë нулевого логического уровня и затем на вход R устройства подается также сигнал нулевого логического уровня, а на синхровход С устройства — импульс. При этом на выходе элемента ИЛИ-НЕ 8 вырабатывается сигнал нулевого логического уровня, который закрывает третьи группы входов элементов ЗИ-ИЛИ 12.1-12.4, первые и вторые группы входов которых также закрыты следующими сигналами: первые группы входов закрыты нулевым логическим уровнем сигнала с выхода элемента

ИЛИ-1- 9, так как на входе Ч2 устройства — сигнал логической единицы, а вторые группы входов — нулевым сигналом с выхода элемента И 10, так как на его инверсном входе присутствует сигнал логической единицы с выхода элемента НЕ 7. Таким образом, на выходах элементов ЗИ-ИЛИ

12,1-12.4 формируется сигнал логического нуля, что приводит к формированию на выходах элементов И-НЕ 14.1 и 14.2, 2И-ИЛИН Е 17.1 — 17.3 сигналов логической единицы.

Следовательно, с приходом синхроимпульса с С-входа устройства через элемент НЕ 6 триггеры 5.1-5,4 установятся в состояние логического нуля.

При исправном состоянии всех основных триггеров 5,1 — 5,4 на их F-выходах присутствует сигнал логического нуля. В этом случае сигналами с инверсных выходов элементов ИЛИ/ИЛИ-НЕ 15.1-15.4 открыты следующие логические элементы устройства: элемент И-НЕ 14,1 и первая группа входов элемента 2И-ИЛИ 18,1, вторая группа входов элемента 2И-ИЛИ-НЕ 17.1 и первая группа входов элемента 2И-ИЛИ 18.2, вторая группа входов элемента 2И-ИЛИ-НЕ

17.2 и первая группа входов элемента 2ИИЛИ 18.3, вторая группа входов элемента

2И-ИЛИ-НЕ 17,3 и первая группа входов

13 элемента 2И-ИЛИ 18.4. Одновременно с

ЭТИМ ЗаКрЫВВЮтСя СЛЕдуЮщИЕ Лоы< «С", ° элементы устройства; первая группа в: ц< в элементов 2И-ИЛИ-НЕ 17,1-17,3, в).,рые группы входов элементов 2И-ИЛИ 18 118,4, элементы И 16.1 — 18.4 и элементы

ИЛИ/ИЛИ-НЕ 15.1 — 15.4.

Рассмотрим два основных режима функционирования двоичного счетчика: установка его предварительная, отличное от нуля состояние и подгчет «олпу t,coB.

Установка двои <ног счетчика н состояние, равное информации нэ входах D.1 — 0.4, производится следующим образом На вход

V2 устройства подае-:ся сигнал логического нуля, на вход С устрс йства синхроимпульс отрицатель)<ои полярности, на вход R — сигнал логи Ie".кой единицы, на выходы Р! и Vt — сигналы логического нуля и на выходы 0,(-D,4 — «<формация о предварительной установке двоичного счетчика.

В этом случае открываются первые группы входов элеме>п ов ЗИ-ИЛИ 12.1-12,4 и на их выходах формирую<гя сигналы, идентичные сигналам на соответствущих входах D, — 0.4 устройства. Э ги сигналы через элементы И-H? (4.1. 2И-И.ЧИ-I-!Е 17,117.3 поступают на инверсные D-нходь) триггеров 5.1-5.4, которые с приходом синхроимпульса устанавливаются н состояния, равные состояниям t

Подсчет импульсов. поступэющ«х на синхровход С устройства, прог1знодится по следующей логической ветв«предлагаемого двоичного счетчикэ. На нь>ходах К, V, Р(, Vl при этом присутствуюг с«)>«аль> логической единицы, а на вход С устройства поступают синхроимпульсы.

С входа С устроиства импульсы поступают через элемент НЕ 6 на си> хронходы триггеров 5.1 — 5.4, которые с приходом каждого синхроимпульса из)лсняют свое состояние в зависимости от предыдущего своего состояния и состояния три>герон предыдущих разрядов.

Рассмотрим пр«мер подсчс)а синхроимпульсон с преднэр«тель io«установкой двоичного счетчика В состоян 1« 10г>! . т.е. перед режимом t) двоичный счет >«к были занесены единичные сосго.,н ;я в тр lrr«pci

5.1 и 5.4. В этом случае ед <»«,<ые состояния с выходов элементов 2И-(l.1(I !8.1 и 18.4

C)

55 открывают следующие элеллен)ы дно«

СЧЕтЧИКа: тРЕтЬИ ГРУППЬ< ВХОДОН ЭЛЕмен)ов

31! И. II1 12.1 и 12.4 (н)орые r руп> ы > . ;;

Э).1) . C ЭЛЕМЕНТОВ ЗВKÐI,>тt Эт«к< 1 КС . > г лами I >их инверсным нход1)л, . В>оры > пы xr,,1oâ элементов ЗИ-ИЛИ 12 2 «12 ( втор,)м входам.

i риггеры разряд н изменят свои сг L

ЯНИЯ (ИЛИ СОХРаНЯт ПРЕДЫДУЩИЕ СОСто>: ".:: следующим образом.

С приходом синхроимпульсэ тр«гге; установится в состояние "0, так как всг )pll группы элемента ЗИ-ИЛИ 12,1 будут за ° >»ь > ты (первач группа входов закрыта нулг, „.1 сигналом с выхода элемента ИЛИ-НЕ 9 амтв рая группа входон «диничнл>м с«гна; «.1 с выхода элемента?И (И !Я.! нэ сс «: нср сный входи третья группа гхо,"> н >Iy» ьн л

ctlrt

С приходом с инхро«м >) ул ь- О; «>,-. р 5 2

УСтаНОВ«тСЯ В ЕДИНИЧОГ- ГОСто)>.,lli г:. ° В> r, элементе ЗИ-ИЛИ 12.2 откр.»н > )(-.;-ч rp) i; па входов с выхода элемен)а И (О. с ;„.c t элемента 2И-ИЛИ 18.1 и ну»свым п.,т«->.,;1 алом с выхода элеменга 2И,1 (И !8 . н;) инверсный вход. С»«донате»»-<п ный уровень сигнала чсг>с з ), >;.т..г пу входов элем«>.тэ 3I1-(1, I(4 12 I°, r О

rpynny ВХОДОВ элемс« <а 2 I;", 1 1 где он иннерт«руется, пог yr);-):) > «>< оо:ный D-Вход триггера 5 2, кг)- pt>, «r pi.,одом синхроим>)ульгэ yciвн iil»i ва -..) в единичное состояние

Триггер 5.3 с приходОл1 с)1><х )o« l „,сз остается в своем np«;;>I>1 >.у )е. >1 )гточ нии по следу>ощим nr)«<«II,."1 >) > . p«руппы элемента ЗИ ИЛ(! " 3 l;!> р> ты первая группа входов нулевым,.«>c> ;I)ot. г . ь>хода элемента ИЛИ-НЕ 9, р.гор;.ч I „ > ) > t ;

-нулевым с«гнало>л .- в >ход.< ° » ч" >-г 2ИИЛИ 18.2 «третья i py! Ii); „r>«p.. сигналом с выхода зг —.)лс>!a " . 1, .." 1 .3

Следовательно, нэ вы.. ;, з,с .;> та ЗИИЛИ 12.3 будет сфор>л«(.ot); >i гc-.: нзл лг„-« рского нуля, ко)орый через PT>),. ч.) r>)y"Ililó входов элемента 2И-ИЛИ (Е: 2 rl;) дит прежнее нулевое сог;Оч >с )p«ri, I,з

5,3.

Триггер 5.4 с np«x!!äoì . 1» ° го> лг ульса остается н своем г рсжн«м ед>1 I«

ЗИ-ИЛИ 12.4 в этом с»у вс oi I)i>ro TI)«T-Я

rpynna входов с t c! o) Он эл>..r «<тон 2>ЧИ)1И 18.4, ИЛИ-НЕ 8 «И-НГ 1 4 Б,:, во et1y триггер 5«4 с пр«..одо>л c«<õpr Il, . .I)y I".cа

Останется В прсжн "-< «д«I<« »<О>л Г > )» <« 1

Таким образом, с пр«ход.-л и:рно о синхро«мпульса дно«чный сче- «ê примет госточнис "10,0", т.е. «3!"cc<«т сВОВ со-,тоя

1684927 дующих элементов ИЛИ/ИЛИ-НЕ, что, в свою 40

55 ние на "-1". С приходом второго синхроимпульса прецла>аел1ый двоичный счетчик примет состояние "1011" по следущему алгоритму работы.

Триггер 5.1 установится в единичное состояние, так как открыта вторая группа входов элемента ЗИ-ИЛИ 12,1 сигналами с выхода элемента И 10 и с выхода элемента

2И-ИЛИ 18.1 (нулевой сигнал на инверсный вход), Триггер 5.2 остается в единичном состоянии, так как в этом случае открыта третья группа входов элемента ЗИ-ИЛИ 12.2 сигналами с выходов элементов 2И-ИЛИ 18.2, ИЛИ-ME 8 и И-ME 13.2 соответственно, Триггер 5.3 остается в нулевое состоянии, так как все три группы входов элементов ЗИ-ИЛИ 12.3 закрыты сигналами с выходов элементов ИЛИ-НЕ 9, 2И-ИЛИ 18,1 и 18.3 соответственHo.

Триггер 5,4 остается в единичном состоянии, так как открыта третья группа входов элемента ЗИ-ИЛИ 12,4 сигналами с выходов элементов 2И-ИЛИ 18.4, ИЛИ-НЕ 8 и И-HE

13.4 соответственно.

Подсчет третьего, четвертого и т.п, импульсов производится аналоги >ным образом. При достижении двоичным счетчиком состояния, равного "1111", на его выходе Pz формируется единица переноса, что позволяет образовать из нескольких предлагаемых двоичных счетчиков двоичный счетчик большей разряднос ги.

При отказе каксго-либо одного из основных триггеров 5,1-5.4 íà его выходе F появляется си> íàë lloгической единицы, который, поступая на сответствующий элемент ИЛ И /ИЛ И-Н Е 15. 1 — 15.4, приводит к смене сигналое на выходах данного и послеочередь, приводит к перестройке (автоматической рекс>нфигурации) работоспособной структуры предлагаемого счетчика, При отказе одного из основных три герое на выходе элемента ИЛИ 19,2 также формируется сигнал логической единицы, что приводит к формированию сигнала "Частичный отказ" на соответствующем выходе двоичного счетчика.

Рассмотрим пример, когда отказал триггер 5.2 второго разряда. В этом случае на выходе F триггера 5.2 формируется сигнал логической единицы, что приводит к формированию на инверсных выходах элементов ИЛИ/ИЛИ-НЕ 15.2-15,4 сигналов логического нуля и сигналов логической единицы на их прямых выходах. Так как на прямом выходе элемента ИЛИ/ИЛИ-НЕ

15.4 также сформирован сигнал логической единицы. то на выходе элемен1а ИЛИ 19.2

35 появляется сигнал " 1астичный с: > 13 В результате смены сигналов на выхсдах элементов ИЛИ/ИЛИ-It Е «ткрывак>тся следующие логические элемеHòì д ои,ного счетчика: первые группы входов элементов

2И-ИЛИ-НЕ 17.2 и 17.3, элемент И НЕ 14.2 и вторые группы входов элемснтов 2И-ИЛИ

18.2-18.4. Одновременно с этим закрываютс.я следующие логические элементы двоичного счетчика: элемент 2И-ИЛИ-НЕ 17.1 по двум группал4 входов (г с;. а" я группа входов сигналом с прямого вь хода элемента

ИЛИ/ИЛИ-НЕ 15.1. а вторая — сигналом с инверсного выхода алел ента ИЛИ/ИЛИ-НЕ 5.2), вторые группы входов элементов 2ИИЛИ-НЕ 17,2 и 17,3 и первые группы входов элементов 2И-ИЛИ 18,2-18.4.

В режиме занесения параллельного кода информации пр".äóñòeíoâà с входов

0,1 D.4 устройства дгоичный счетчик в этом случае работает следующим образом.

Сигнал с входа D. > устройства через открытую первую группу входов элемента ЗИИЛИ 12.1, элемента И-НЕ 14.1 поступает на инверсный 0-вход триггера 5.1. Сигнал с входа D.2 устройства через открытые первую группу входов ле лентэ ЗИ-ИЛИ 12.1 и первую группу входов элемента 2И-ИЛИ-НЕ 17.2 поступает на инверсный 0-вход триггера 5.3. Сигнал с входа 0.з устройства через открытые первую > руппу входов элемента

ЗИ-ИЛ1" 12.3 и перву>о группу входов элемента 2И-ИЛИ-НЕ 17.3 поступает на инверсный D-вход триггера 5.4. Сигнал с входа 0.4 устройства через открытую первую группу входов элемента ЗИ-ИЛИ 12.4 и элемент

И-НЕ 14.2 поступает на инверсный 0-вход триггера 5.5, С приходом на вход С устройсТВВ синхроимпульса отрицательной полярности триггеры 5.1, 5,3-5,5 устанавливаЮтся в состояния, соогветствуюгцие со=тояниям на входах 0.1-D,4 устройства.

Сигнал с прямого выхода триггера 5.1 через открытую первую группу входов элемента

2И-Nfl VI 18, поступает на разрядный выход

0.1 устройства. Сигнал с прямого выхода триггера 5.3 через открытую вторую группу входов элемента 2И-ИЛИ 18.2 поступает на разрядный выход G,2 устройства. Сигналы с прямых выходов триггеров 2И-ИЛИ 18.3 и

18.4 на разрядные выходы О.з и 0.4 устройства соответственно. Выход триггера 5.2 заблокирован закрытой второй группой входов элемента 2И-ИЛИ 18.1 и первой группой входов элемен гэ 2И-ИЛИ 18,2, Таким образом, н роз > ь>ате формирования сигнала на выходе тригi ера 5.2

"Отказ" происходит ггоматическая перестройка работоспособной с>руктурьл двоич17

1634927 ного счетчика по принципу вытес«ен;1я иэ нее триггера 5.2.

Подсчет импульсов в случае отказа триггера 5.2 производится следующим образом.

При нулевом состоянии триггера каждого разряда, кроме 5.2, и единичном состоянии триггеров предшествующих разрядов этот триггер 5. J при помощи открытого состояния второй группы входов соответствующего элемента ЗИ-ИЛИ 12 устанавливается в единичное состояние с поступлением очередного синхроимпульса. При предыдущем единичном состоянии триггера соответствующего разряда и при единичном состоянии триггеров предыдущих разрядов даный триггер 5. J с приходом очередного синхроимпульса устанавливается в нулевое состояние, В остальных случаях триггеры разрядов сохраняют свое прежнее состояние. Обход отказавшего триггера 5,2 также осуществляется закрытым состоянием элемента 2И-ИЛИ-НЕ 17.1 по обеим группам входов и закрытым состояниям элемента

2И-ИЛИ-НЕ 17.1 по обеим группам входов и закрытым состоянием первой группы входов элемента 2И-ИЛИ 18,2 и второй группы входов элемента 2И-ИЛИ 18.1.

Переход на работоспособную структуру двоичного счетчика при отказе zðèããåðà первого, третьего и чертвертого разрядов производится аналогичным способом, При отказе двух и более основных разрядов на выходе элемента ИЛИ 19 формируется сигнал "Отказ" устройства в целом, который, сигнализирует о TOM, что необходима замена счетчика в целом,.так как имеющийся резерв в структуре устройства недостаточен для покрытия возн