Патент ссср 168536

Иллюстрации

Показать всеРеферат

l68536

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 09.VIII.1962 (№ 790201/26-24) с присоединением заявки №

Приоритет

Опубликовано 18.11.1965. Бюллетень № 4

Дата опубликовашгя описания 8.III.1965

Кл. 42m, 1404

МПК G 064

УДК 681 142(088 8) Государственный комитет по делам изобретений и открытий СССР

ЦИФРОВАЯ УНИВЕРСАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА

Подписная гругггга Л3 174

Известны цифровые универсальные машины, содержащие логические устройства, запоминающие устройства, регистры.

Предлагаемая цифровая универсальная машина отличается тем, что в ней устройство запоминания — суммирования подсоединено к буферному регистру с ключами для временного хранения числа и сдвига, подключенному к дешифратору кода операции, подсоединенному к устройству запоминания — суммирования, дешифратору адресов и схеме микропрограмм, которая подсоединена к буферному ðoгистру и к дешифратору адресов.

Это позволяет уменьшить оборудование цифровой вычислительной машины. Производительность машины сохраняется, так как арифметические операции выполняются в запоминающем устройстве, за счет чего уменьшается количество пересылочных операций и возрастает одновременная загрузка отдельных узлов вычислительной машины.

Предлагаемая универсальная цифровая вычислительная машина также отличается тем, что для выполнения операции суммирования каждый разряд устройства запоминания— суммирования содержит ключи считывания, подсоединенные к обмотке считывания основного ферромагнитного сердечника запоминающего устройства. Средняя точка обмотки считывания подключена к выходу формирователя, один из входов которого подсоединен к источнику сигнала второго слагаемого, подсоединенному также к обмотке записи логического ферритового сердечника, выходная оомотка которого подсоединена ко второму входу формирователя. Одна из обмоток опроса логического сердечника подсоединена к источнику сигнала опроса, обмотка считки основного сердечника запоминающего устройства

10 первого слагаемого, промежуточной и полной суммы подключена к усилителю чтения, выход которого подсоединен ко второй обмотке опроса логического сердечника.

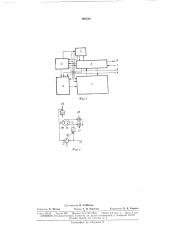

На фиг. 1 изображена блок-схема предла15 гаемой универсальной цифровой вычислительной машины; на фиг. 2 — принципиальная схема разряда устройства запоминания — суммирования.

Устройство 1 запоминания — суммирования

2Î содержит ферритовую матрицу, формирователи записи и считывания с клапанами, усилители чтения и дополнительные логические сердечники. Оно подсоединено к буферному регистру 2 с четырьмя ключами на каждый раз25 ряд, который используется для временного хранения числа и сдвига при суммировании частных сумм и переносов, а также осуществления программируемых сдвигов.

Схема 8 микрокоманд содержит одну QKcHз0 феровую линейку (типа линейки ПЗУ) с одним

168536

1О

15 гс

60 распределителем импульсов и вырабатывает последовательность синхронизирующих импульсов для реализации командных и арифметических операций.

Предлагаемая вычислительная машина также содержит координатный дешифратор 4 адресов и дешифратор 5 кода операций.

Вывод информации осуществляется по шине 6 из буферного регистра 2.

Ввод информации осуществляется по шине

7, шина 8 ввода команд приема информации подключена к схеме микропрограмм, а шина

9 ввода адресов подключена к дешифратору адресов.

В предлагаемой машине отсутствует арифметическое устройство, функции его выполняет устройство 1 суммирования — запоминания совместно с регистром 2 благодаря логическому совмещению функций суммирования и запоминания.

Операции умножения, деления, извлечения квадратного корня выполняются путем последовательного алгебраического сложения и сдвига, осуществляемого переписями через регистр 2. Командные операции безусловных и условных переходов выполняются также путем переписи.

Работа одного разряда устройства 1 (фиг,2) происходит следующим образом. Одно из слагаемых записано в основном сердечнике 10 устройства 1, второе слагаемое поступает на формирователь 11 и логический сердечник 12 и вызывает срабатывание усилителя чтения 18, на выходе 14 которого образуется сигнал переноса, а в основном запоминающем сердечнике

10 запоминается значение частичной суммы.

Перенос с выхода 14 поступает на буферный регистр 2 с его системой ключей и оттуда со сдвигом поступает на вход 15, по которому подавалось второе слагаемое со сдвигом на такт, в результате чего в основном сердечнике

10 получается полная сумма.

Если в запоминающем сердечнике 10 была записана «1» или «0», то при приходе импульса

«0» на вход 15 формирователь 11 и логический сердечник не срабатывают, информация в сердечнике 10 не стирается и усилитель 13 не срабатывает. Если приходит импульс «1» по входу

15 синхронно с К вЂ” 1 тактовым импульсом и сердечник 10 находится в состоянии «0», то открываются формирователь 11 и ключ 16, на вход 17 которого подан соответствующий тактовый импульс, При этом в сердечнике 10 ничего не происходит. Импульс по входу 15 записывается также в логический сердечник.

Тактовым импульсом К вЂ” 2 осуществляется onрос состояния сердечника 12, на выходе 18 возникает импульс, возбуждающий формирователь 11. Ключ 19 открыт, так как на него поступает синхронизирующий импульс по входу 20. Информация записывается в сердечник

10, и он из нулевого состояния переходит в состояние «1». Если сердечник 10 находился в состоянии «1», то его опрос происходит при возбуждении формирователя 11 и ключа 16.

Импульс, возникающий в обмотке 21, открывает усилитель 18, вследствие чего образуется импульс переноса, а также осуществляется считывание информации с логического сердечника 12 с задержкой на срабатывание схем, путем подачи импульса с выхода 14 на обмотку опроса. Импульс, возникающий на выходе

18, вызывает срабатывание формирователя

1I, но при этом никаких операций не происходит, так как ключи 16 и 19 закрыты, В сердечнике 10 образуется значение промежуточной суммы.

При суммировании частичной суммы с переносами, поступающими из буферного регистра

2, дальнейшие переносы невозможны. Таким образом, суммирование занимает четыре тактовых интервала при одной пересылочной операции, в отличие от трех пересылочных операций в известных вычислительных машинах, Одновременная работа всех блоков позволяет существенно увеличить производительность вычислительной машины.

Предмет изобретения

1. Цифровая универсальная вычислительная машина, содержащая логические устройства и запоминающие устройства, отличающаяся тем, что, с целью уменьшения оборудования цифровой вычислительной машины при сохранении высокой производительности путем выполнения арифметических операций в запоминающем устройстве, в ней устройство запоминания — суммирования подсоединено к буферному регистру с ключами для временного хранения числа и сдвига, подключенному к дешифратору кода операции, подсоединенному к устройству запоминания — суммирования, дешифратору адресов и схеме микропрограмм, которая подсоединена к буферному регистру и к дешифратору адресов.

2. Машина по п. 1, отличающаяся тем, что, с целью выполнения операции суммирования, каждый разряд устройства запоминания — суммирования содержит ключи считывания, подсоединенные к обмотке считывания основного ферромагнитного сердечника запоминающего устройства, его средняя точка подключена к выходу формирователя, один из входов которого подсоединен к источнику сигнала второго слагаемого, подсоединенному также к обмотке записи логического ферритового сердечника, выходная обмотка которого подсоединена ко второму входу формирователя, одна из обмоток опроса логического сердечника подсоединена к источнику сигнала опроса, обмотка считывания основного сердечника запоминающего устройства первого слагаемого, промежуточной и полной суммы подключена к усилителю чтения, а выход усилителя чтения подсоединен ко второй обмотке опроса логического сердечника.

168536 фиг t

Составитель В. Субботин

Редактор П. Шлаин Техред Т. П. Курилко

Корректор О. Б. Тюрина

Заказ 154)!5 Тирани 900 Формат бум. 60)(901/q Объем 0 3 нзд. л. Цена 5 коп.

ЦНИИПИ Государственного комитета по делам изобретений п открытий СССР

Москва, Центр, пр. Серена, д. 4

Типография, пр. Сапунова, 2