Устройство для деления

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в быстродействующих арифметических устройствах Изобретение позволяет увеличить быстродействие уст ройства для деления путем сокращения ступеней логических элементов в цепях анализа устройства и при формировании старших разрядов ооатка при делении операндов . Устройство содержит регистры де лимого 7 и делителя 8, три сумматора 16-18 с сохранением переносов, три коммутатора 13-15 делителя, две группы 9, 26 элементов HF, два сдвиговых регистра 28, 29 частного, регистр 32 поразрядных сумм, регистр поразрядных 31 переносов, регистр 30 управляющих сигналов, два коммутатора 34, 35 частного, коммутатор поразрядной суммы, коммутатор 12 поразрядного переноса, сумматор 37, триггер 38 коррекции, два триггера 3, 6 входных управляющих сигналов , элемент НЕ 27, элемент И 36. блок 33 управления, регистр 39 результата, один шифратор 10 первого уровня, три шифратора 19-21 второго уровня, два шифратора 22, 23 третьего уровня и два двухразрядных коммутатора 24, 25. 1 табл.. 3 ил. И

союз сОВетских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 7/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОбРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ф (21) 4776714/24

{22) 17,11.89 (46) 23.10.91, Бюл, ¹ 39 (71) Научно-производственное объединение

"Персей" (72) Ю.С. Варакин, Н,Д. Воронцова и В.Г. Моисеев (53) 681,325 (088,8) (56) Авторское свидетельство СССР

N 1141403, кл. G 06 F 7/52, 1983, Авторское свидетельство СССР № 1278837, кл. 6 06 F 7/52, 1985. (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в быстродействующих арифметических устройствах. Изобретение позволяет увеличить быстродействие устройства для деления путем сокращения ступеней логических элементов в цепях!

Ж„„1686436 А1 анализа устройства и при формировании старших разрядов ос гатка при делении операндов. Устройство содержит регистры делимого 7 и делителя 8, три сумматора 16-18 с сохранением переносов, три коммутатора

13-15 делителя, две группы 9, 26 элементов

НЕ, два сдвиговых регистра 28, 29 частного, регистр 32 поразрядных сумм, регистр поразрядных 31 переносов, регистр 30 управляющих сигналов, два коммутатора 34. 35 частного, коммутатор поразрядной суммы, коммутатор t2 поразрядного переноса, сумматор 37, триггер 38 коррекции, два триггера 3, 6 входных управляющих сигналов, элемент НЕ 27, элемент И 36, блок 33 управления, регистр 39 результата, один шифратор 10 первого уровня, три шифратора 19-21 второго уровня, два шифратора 22, 23 третьего уровня и два двухразрядных коммутатора 24, 25, 1 табл., 3 ил.

1686436

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств высокой производительности.

Цель изобретения — повышение быстродействия устройства.

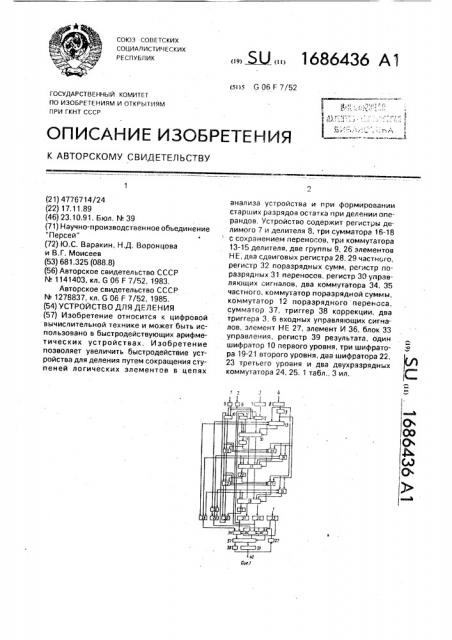

На фиг. 1 приведена структурная схема устройства для деления; на фиг, 2 — схема шифраторов первого, второго и третьего уровней и схема двухразрядного коммутатора; на фиг. 3 — схема блока управления.

Устройство для деления.(фиг. 1) содержит вход 1 прямого сигнала "Пуск", вход 2 инверсного сигнала "Пуск", вход 3 делимого устройства, вход 4 делителя устроиства, первый и второй управляющие триггеры 5 и

6, регистр 7 делимого, регистр 8 делителя, первую группу 9 элементов НЕ, шифратор

10 первого уровня, коммутатор 11 поразрядного переноса, коммутатор 12 порязрядной суммы, коммутаторы 13 15 делителя, сумматоры 16 — 18 с сохранением переносов, шифраторы 19 — 21 второго уровня, шифраторы 22 и 23 третьего уровня, двухразрядные коммутаторы 24 и 25, вторую группу 26 элементов НЕ, элемент НЕ 27, второй и первый сдвиговые регистры 28 и 29 частного, регистр 30 управляющих сигналов, регистр

31 поразрядного переноса и регистр 32 поразрядной суммы, блок 33 управления, два коммутатора 34 и 35 частного, элемент И 36, сумматор 37, триггер 38 коррекции, регистр

39 результата, выход 40 устройства.

Шифраторы 10, 19 и 22 первого, второго и третьего уровней (фиг. 2) содержит вход 41 сигнала Сз, запомненный на регистре 30, вход 42 сигнала Аз, запомненный на регистре 30, вход 43 сигнала ИПз, запомненный на регистре 30, вход 44 сигнала Вз, запомненный на регистре 30, вход 45 инверсного управляющего сигнала "Пуск", вход 46 сигнала Г)з, запомненный на регистре 30, вход 47 прямого управлякнцего сигнала

"Пуск", вход 48 сигнала ППз, запомненный на регистре 30, два элемента И-ИЛИ 49 и 50, вход 51 разрядной суммы Sn, вход 52 поразрядного переноса, вход 53 первого старшего разряда- S>, вход 54 второго старшего разряда Яг сумматора с сохранением переносов, вход 55 второго старшего разряда

Pz, вход 56 третьего старшего разряда сумматора с сохранением переносов, вход 57 сигнала ИП, управляющего инверсной передачей делителя, вход 58 сигнала ПП, управляющего прямой передачей делителя, полусумматор 59, элемент И-ИЛИ 60, элемент И-ИЛИ-НЕ 61, элемент И-НЕ 62, первый выход 63 шифратора (А) 19, второй выход 64 шифратора (В) 19, третий выход 65 шифратора (С) 19, четвертый выход 66 шифратора (0) 19, два элемента И-ИЛИ 67 и 68, два элемента И-ИЛИ 69 и 70, вход 71 (q2) третьего старшего разряда делителя, вход

72 (q2) инверсии третьего старшего разряда

5 делителя, вход 73 (q1) второго старшего разряда делителя, вход 74 (о1) инверсии второго старшего разряда делителя, выход 75 . (ИП), управляющий инверсной передачей делителя, выход 76 (ПП), управляющий

10 прямой передачей делителя, выходы 77 и

78 (Q<, 0 ) двухраэрядного коммутатора.

Блок 33 управления (фиг.3) содержит реверсивный счетчик 79. анализатор 80 нуля, прямой 81 и инверсный 82 выходы сиг15 нала конца операции с анализатором нуля.

Деление выполняется над нормализованными, положительными числами, т. е. делимое и делитель должны иметь единицу в старшем разряде мантиссы.

20 В устройстве применяется принцип деления, при котором используется избыточный код частного, т, е. каждая цифра частного может быть представлена в виде одной иэ трех цифр; -1, О, +1. Остаток фор25 мируется в виде двухразрядного кода, включающего код поразрядной суммы и код поразрядного переноса.

Устройство работает следующим образом, 30 Перед началом работы деления на триггеры 5 и 6 поступают управляющие сигналы

"Пуск" и "Пуск", в регистры 7 и 8 — значения делимого и делителя. По сигналу "Пуск" в счетчик 79 блока 32 управления заносится

35 код числа, определяющий количество тактов деления, а в шифраторе 10 первого уровня вырабатывается ИП (обратная передача делителя), по которому через коммутатор 13 на первый вход первого сумматора с сохра40 нением переноса поступает обратный код делителя, при этом знаковый разряд делителя и следующий старший разряд делителя формируются путем подачи управляющих сигналов ИП (57) и ПП (58) с шифратора 10

45 первого уровня в нулевой и старший разряды сумматора 16 с сохранением переносов, а сигнал единицы дополнительного кода— путем подачи управляющих сигналов ИП в младший разряд сумматора 16.

50 По управляющим сигналам триггеров 5 и 6 с коммутатора 11 на вход сумматора 16 с сохранением переносов выдается нулевой сигнал, а с коммутатора 12 — значение делимого. Таким образом, старшие разряды

55 сумматора 16 формируются раньше, что сокращает время формирования управляющих сигналов в шифраторе 19 второго уровня для организации следующего действия деления. Сигналы с шифратора 19 второго уровня и с шифратора 10 первого

1686436

35

50

55 уровня поступают на вход шифратора 22 третьего уровня и двухразрядного коммутатора 24, через который на вход сумматора

17 с сохранением переноса поступает второй и третий старшие разряды мантиссы делителя.

Нулевой и первый разряды делителя организуются путем подачи управляющих сигналов ИП (75) и ПП (76) с выхода шифратора третьего уровня 22 в нулевой и старший разряды сумматора 17 с сохранением переносов, а сигнал единицы дополнительного кода учитывается путем подачи управляющего сигнала ИП в младший разряд сумматора 17, остальные разряды делителя через коммутатор 14 подаются на соответствующие входы сумматора 17.

Выходы поразрядной суммы и поразрядного переноса с сумматора 16 со сдвигом соответственно на один и два разряда влево подаются на входы сумматора 17, при этом старшие разряды сумматора 17, соединенные с входом шифратора 20, формируются быстрее остальных разрядов, обеспечивая опережающую выработку сигналов А, В, С, D с выхода шифратора 20.

Формирование поразрядной суммы и поразрядного переноса с сумматора 18 происходит аналогично формированию поразрядной суммы и поразрядного переноса с сумматора 17, при этом сигналы с выхода шифратора 23третьего уровня и шифратора

21 второго уровня запоминаются на регистре управляющих сигналов 30 и используются в шифраторе 10 первого уровня для выработки управляющих сигналов ИП и ПП для управления передачей разрядов делителя через коммутатор 13 на вход сумма-. тора 16.

Сигналы поразрядной суммы и поразрядного переноса, запомненные на регистрах 32 и 31, со сдвигом соответственно на один и два разряда через коммутаторы 12 и

11 поступают на сумматор 16. Выходы шифратора 10 первого уровня и шифраторов 22 и 23 третьего уровня определяют значения цифр частного. Так как в начале деления, определяемом входным управляющим сигналом "Пуск", на выходе шифратора первого уровня формируются сигналы ИП = 1 и ПП = О, то в первый 28 и второй 29 регистры частного запишется единичное значение.

Если на выходе шифратора первого уровня или шифратора третьего. уровня сформированы сигналы ИП = О и ПП = О, то в первый регистр 28 частного запишется

"О", а во второй регистр 29 частного запишется "1".

Если на выходе шифратора первого уровня или шифратора третьего уровня сформированы сигналы ИП = О и ПП = 1, то в первый 28 и во второй 29 регистры частного запишется "О". Таким образом, в первый

28 регистр частного поступают сигналы ИП, а во второй 29 — сигнал ПП через инверторы второй группы элементов НЕ 26.

В каждый машинный такт в младшие разряды регистров 28 и 29 записываются тои цифры частного, при этом цифры частного, записанные в предыдущийтакт, переписываются в этот же регистр со сдвигом влево на три разряда.

В процессе деления для получения в конце операции знака остатка с выхода блока 33 управления поступают управляющие сигналы 81 и 82, с помощью которых через коммутаторы 34 и 35 на вход сумматора 37 поступают поразрядная сумма и поразрядный перенос с учетом веса разрядов (разряды поразрядного переноса сдвинуты относительно поразрядной суммы на один раз— ряд влево). Знаковый разряд сформированной при этом суммы является сигналом коррекции, необходимой при делении без восстановления остатка, и запоминается на триггере 38, выход которого через элемент

HF.. 27 поступает на вход элемента И 36, В момент конца операции, когда константа деления, записанная в счетчик по сигналу

"Пуск", превратится в нуль, на выходе блока управления формируются сигналы 81 и 82, под уп ра вле н ием которых через коммутаторы 34 и 35 на вход сумматора 37 поступают значения регистров 28 и 29 частного, а на вход переноса сумматора 37 — сигнал коррекции с выхода элемента И 36. Результат суммирования записывается в регистр, выход 40 которого является выходом устройства деления.

Быстродействие устройства для деления обратно пропорционально величине машинного такта устройства, который определяется максимальным числом логических уровней задержки сигналов между регистрами.

В устройстве для определения первой цифры необходимы четыре уровня (один уровень в шифраторе первого уровня, один уровень для коммутатора, один уровень в шифраторе второго уровня, один уровень в шифраторе третьего уровня). Для определения второй цифры добавляется еще два уровня (один уровень в шифраторе второго уровня, один уровень в шифраторе третьего уровня).

Для анализа старших разрядов третьего сумматора с сохранением переносов необходимо затратить еще один логический уро1686436

10 l5

25 вень в шифраторе второго уровня. Таким образом, для определения трех цифр частного в предлагаемом устройстве необходимо затратить 7 логических уровней и 3 логических уровня сумматоров с сохранением переносов, Условия формирования управляющих сигналов с шифраторов первого, второго и третьего уровней представлены в таблице.

Формула изобретения

Устройство для деления, содержащее регистры делимого и делителя, две группы элементов НЕ, три коммутатора делителя, два сдвиговых регистра частного, регистр поразрядных сумм, регистр поразрядных переносов, регистр управляющих сигналов, два коммутатора частного, коммутатор поразрядной суммы, коммутатор поразрядного переноса, сумматор, триггер коррекции, элементы НЕ, элемент И, блок управления, регистр результата, два двухразрядных KGMмутатора, два управляющих триггера и три сумматора с сохранением переносов, причем входы первого и второго управляющих триггеров соединены с входами прямого и инверсного сигналов "Пуск" устройства соответственно, информационный вход регистров делимого и делителя соединен с входами делимого и делителя устройства соответственно, выходы регистра делителя соединены с входами элементов НЕ первой группы и с первыми информационными входами первого, второго и третьего коммутаторов делителя, вторые информационные входы которых соединены с выходами злементов НЕ первой группы, выход регистра делимого соединен с первым информационным входом коммутатора поразрядной суммы, выходы первого, второго и третьего коммутаторов делителя соединены с первыми информационными входами младших разрядов первого, второго и третьего сумматоров с сохранением переносов соответственно, выход коммутатора поразрядной суммы соединен с вторым информационным входом первого сумматора с сохранением переносов, вход переноса которого соединен с выходом коммутатора поразрядного переноса, выходы поразрядной суммы и поразрядного переноса первого и второ о сумматоров с сохранением переносов соединены соответственно с вторым информационным входом и входом переносов второго и третьего сумматоров с сохранением переносов соответственно, выходы поразрядной суммы и поразрядного переноса третьего сумматора с сохранением переносов соединены с информационными входами регистров поразрядной суммы и

55 поразрядного переноса соответственно, выход регистра поразрядного переноса соединен с информационным входом коммутатора поразрядного переноса и с первым информационным входом первого коммутатора частного, выход регистра поразрядной суммы соединен с вторым информационным входом коммутатора поразрядной суммы и первым информационным входом второго коммутатора частного, выходы элементов НЕ второй группы соединены с информационными входами первого сдвигового регистра частного, выходы первого и второго сдвиговых регистров частного соединены с вторыми информационными входами второго и первого коммутаторов частного соответственно, первый выход блока управления соединен с первыми управляющими входами первого и второго коммутаторов частного, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены шифратор первого уровня, три шифратора второго уровня и два шифратора третьего уровня, причем выход первого управляющего триггера соединен с первым управляющим входом коммутатора поразрядной суммы, с первым входом шифратора первого уровня и входом запуска блока управления, выход второго управляющего триггера соединен с вторым управляющим входом коммутатора поразрядной суммы, управляющим входом коммутатора поразрядного переноса и вторым входом шифратора первого уровня, выходы старших разрядов первого, второго и третьего сумматоров с сохранением переносов соединены с входами первого, второго и третьего шифраторов второго уровня с соответственно, выход первого шифратора второго уровня соединен с первым входом первого шифратора третьего уровня и первым управляющим входом первого двухразрядного коммутатора, выход второго шифратора второго уровня соединен с первым входом второго шифратора второго уровня и первым управляющим входом второго двухразрядного коммутатора, выход третьего шифратора второго уровня соединен с информационным входом младшего разряда регистра управляющих сигналов, выход которого соединен с третьим входом шифратора первого уровня, первый выход шифратора уровня соединен с первым управляющим входом первого коммутатора делителя, с вторым входом первого гвифратора третьего уровня, с вторым управляющим входом первого двухрэзрядног0 коммутатора, с первым входом элементов

НЕ второй группы и с входом первого старшего разряда переноса первого сумматора

1686436

10 с сохранением переноса, второй выход шифратора первого уровня соединен с вторым управляющим входом первого коммутатора делителя, третьим управляющим входом первого двухразрядного коммутато- 5 ра, с третьим входом первого шифратора третьего уровня, с первым информационным входом второго сдвигового регистра частного и с входом второго старшего разряда переноса и входом логической едини- 10 цы первого сумматора с сохранением переноса, первый выход первого шифратора третьего уровня соединен с первым упавляющим входом второго коммутатора делителя, с вторым информационным вхо- 15 дом второго сдвигового регистра частного, с входом первого старшего разряда переноса и входом логической единицы второго сумматора с сохранением переноса, с вторым входом второго шифратора третьего 20 уровня и с вторым управляющим входом второго двухразрядного коммутатора, второй выход шифра ора третьего уровня соединен с вторым управляющим входом второго коммутатора делителя, с вторым 25 входом элементов НЕ второй группы, с входом второго старшего разряда переноса второго сумматора с сохранением переносов, с третьим входом второго шифратора третьего уровня и с третьим управляющим 30 входом второго двухразрядного коммутатора, первый выход второго шифратора третьего уровня соединен с первым управляющим входом третьего коммутатора делителя, с третьим информационным входом 35 второго сдвигового регистра частного, с входом логическОй единицы и с первым ин- формационным входом первого старшего разряда третьего сумматора с сохранением переносов, второй выход второго шифрато- 40 ра третьего уровня соединен с вторым управляющим входом третьего коммутатора делителя, с третьим входом элементов НЕ второй группы, с информационным входом второго разряда регистра управляющих сигналов и с входом второго старшего разряда переноса третьего сумматора с сохранением переносов, первые информационные входы первого и второго двухразрядных комму-.аторов соединены с выходами второго и третье. о старших разрядов регйстра делитег я, выходы первого и второго старшего разрядов первой группы элементов НЕ соединены с вторь:ми информационными входами первого и вторбго двухразрядных коммутаторов, выходы первого и второго двухразрядных коммутаторов соединены с первыми информационными входами третьего и четвертого старших разрядов второго и третьего сумматоров с сохранением переносов соотве ственно, второй выход блока управления соединен с вторыми управЛяющими входами первого и второго коммутаторов частного, выходы которых соединены с первым и вторым информационными входами сумматора, знаковый разряд которого соединен с входом триггера коррекции, выход которого через элемент НЕ соединен с первым входом элемента И, второй вход которого соединен с первым выходом блока управления, выход элемента И соединен с входом переноса сумматора, выход которого соединен с входом регистра результата, выход которого соединен с выходом результата устройства, выходы первого и второго двухразрядных коммутаторов соединены с третьим входом третьего и четвертого старшего разрядов второго и третьего сумматоров с сохранением переносов соответственно.

1686436 (Я

П р и м е ч а н и е,So, Si, Sz — поразрядная сумма знакового, первого и второго старших разрядов сумматора с сохранением переноса;

Р1, Р2, Рз — поразрядный переНос первого, второго и третьего старших разрядов сумматора с сохранением переноса;

АЗ, 83, С3, D3, ППз, ИПз -запомненные на регистре 30 управляющих, сигналов соответствующие сигналам А, В, С, О, ПП, ИП;

"Пуск" и "Пуск" — входные управляющие сигналы.

168б43Ь

Составитель Н.Маркелова

Техред M.Ìîðãåíòàë Корректор M. Кучерявая

Редактор Л. Гратилло

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 3598 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35; Раушская наб., 4/5