Устройство для согласования интерфейсов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для электрического и алгоритмического согласования микро- ЭВМ с периферийными устройствами ввода-вывода, в частности с дисплеем и накопителем на гибких магнитных дисках. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности увеличения числа устройств, одновременно подключаемых к интерфейсу микроЭВМ. Устройство содержит блоки усиления первого и второго интерфейсов, блок обратимого преобразования параллельного кода в последовательный, три узла переключателей, элемент И, элемент НЕ, блок канальных передатчиков , блок элементов НЕ. 1 ил. о « (Л

СОЮЗ СОВЕТСКИХ

Н

РЕСПУБЛИК рц G 06 F 13/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

Il0 ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ I —

Н АВТОРСКОМУ(СВИДЕТЕЛЬСТВУ

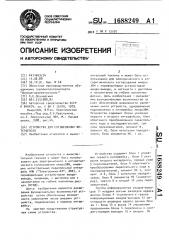

Устройство содержит блок 1 усиления первого интерфейса, блок 2 усиления второго интерфейса, первый узел

3 переключателей, блок 4 ооратимого Q(} преобразования параллельного кода в QQ последовательный, элемент НЕ 5, эле- (© чент И 6, блок 7 канальных передатликов, блок 8 элементов HE (инверторов), третий 9 и второй 10 узлы перекл юча т елей.

Группа информационных входов-выходов 11 младших восьми разрядов адреса,В данных олока 4 подключена к группе информационных входов-выходов 12 шестнадцати разрядов адреса данных блока 1. Вход 13 и выход 14 управления прерыванием олока 4 подключены к соот ветствующим выходам 15 и входам 16 (21) 4471663/24 (22) ;5.08,88 (46) 30.10.9 1. Бюл. М 40 (71) Областное производственное обьединение горэлектротранспорта

"Донецкгорэлектротранс" (72) A.E..Злачевский (53) 68 1.325(088.8) (56) Авторское свидетельство СССР

_#_ 840874, à. с 06 F 13/00, 1979.

МикроЭВМ. В 8 кн. Пра.ктическде пособие./Под ред.Л.Н.Преснухина, кн.2. Персональные ЭВМ, М ° : Высшая школа, 1988, рис.44. (54) УСТРОЙСТВО ПЛ СОГЛАСОВАНИ ИНТЕРФЕЙСОВ (57) Изобретение относится к вычисИзобретение относится к вычисли тельной технике и может быть использовано для электрического и алгоритмического согласования микроЭВМ, имеющих магистральный параллельный интерфейс МПИ (" Электроника-60", ДВК), с периферийными устройствами вводавывода, например, с дисплеем или с накопителем на гибких магнитных дисках (НГМК) .

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности увеличения числа внешних устройств, подключаемых к первому интерфейсу.

На чертеже представлена структурная схема уст ройст ва, „„SU„„1688249 A 1 лительной технике и может быть использовано для электрического и алгоритмического согласования микроЭВМ с периферийными устройствами ввода-вывода, в частности с дисплеем и накопителем на гибких магнитных .,дисках. Цель изобретения — расширениее функциональных возможностей "-a счет обеспечения возможности увеличения числа уст ройс т в, одновременно подключаемых к интерфейсу микроЭВМ.

Устройство содержит блоки усиления первого и второго интерфейсов, блок обрати мого преобразова ния па раллел ьного кода в последовательный, три узла переключат елей, зле ме нт И, элемент НЕ, блок канальных передатчиков, блок элементов HE. 1 ил.

1688249 управления прерыванием блока 1. Группа входов 17 синхронизации блока 4 подключена к соответствующим выходам группы выходов 18 блока 1. Выход 19 ответа блока 4 подключен к входу 20 сигнала ответа блока l. Группы информационных входов 21 и выходов 22 записи и считывания блока 4 подключены

J ,к группе входов-выходов 12 блока 1„10

Группа входов 23 режима блока 4 подключена к подвижным контактам 24 переключателей узла 3, Неподвижные нормально замкнутые контакты 25 переключателей узла 3 подлкючены к шине 15

"Плюс источника питания" 26 устройства, Неподвижные нормально разомкнутые контакты 27 переключателей узла

4 подключены к шине "Общий провод" 28 устройства, Информационные выход 29 и 2р вход 30 вывода и ввода последовательного кода блока 4 подключены к соответствующим входам и выходам группы входов 3 1 и выходов 32 данных вывода и ввода блока 2„ Синхронизирующие вы- 25 ход 33 и вход 34 ввода и вывода блока 4 подключены к входу 35 и выходу

36 блока 2. Вход 37 элемента HE 5 подключен к выходу синхроимпульса ад-реса группы выходов 18 синхронизации ЭО ввода -вывода блока 1. Выход 38 элемента НЕ 5 подключен к второму входу 39 элеМента И 6, первый вход 40 которого подключен к выходу )9 синхроимпульса ответа блока 4„Выход 41 элеме нта И 6 подключен к упра вля ющему входу 42 блока 7 канальных передатчиков. К информационным входам 43 блока 7 подключены подвижные контакты

44 перекпючателей узла 9. Неподвижные 40 нормально замкнутые контакты 45 переключателей узла 9 подключены к шине

26 "Плюс источника питания" ус.тройства, а неподвижные Hop JlbHG разомкнутые контакты 46 переключателей узла 9 подключены к шине 28 "Общий провод" устройства, Выходы 47 бпока 7 подключены к группе входов-выходов 12 шестнадцати разрядов адреса данных блока 1. Подвижные контакты 48 переключателей узла 10 подключены к соответствующим входам группы ацресных входов 49 блока 4. Неподвижные нормально разомкнутые контакты 50 переключателей узла 10 подключень.. к выходам 51 соответствующих инверторов блока 8, а неподвижные HopHk3flbHG замкнутые контакты 52 переключателей узла 10 соединены с входами 53 соответствующих инверторов блока 8 и подключены к соответствующим входам-выходам группы входов-выходов 12 шестнадцати разрядов адреса данных блока 1. В .качестве блока 4 может быть использована

БИС типа 1801ВП1-35.

Устройство при помощи блока 1 под— ключается к интерфейсу МПИ микроЭВМ (не показана) . К блоку 2 подключаются периферийные устройства ввода-вывода (УВВ) (не показаны). Устройство работает следующим образомм. !

Ввод данных от УВВ в микроЭВМ и вывод данных от микроЭВМ на УВВ осуществляется при помощи регистров данных (PA(и регистров состояния (PC) устройства, заключенных внутри блока

4, в циклах программного обмена интерфейса МПИ: ВВОД, ВЪ|В00„ВВОД-ПРУЗД"

BblP0jl. Эти регистры блока 4 имеют свои определенные адреса в адресном пространстве микроЭВМ, В адресной части укаэанных циклов микроЭВМ выставляет на шинах адреса данных интерфейса МГ::vl адрес того или иного регистра устройства, стробируя его фронтом синхроимпульса адреса группы выходов 18 управления обменом, а затем производит считывание данных из адресованного регистра или запись данных в адресованный регистр, стробируя вводимые данные синхроимпульсом ввода, а выводимые данные - синхроимпульсов вывода группы сигналов упра вления обменом. Если адрес, выставленный микроЭВМ на шинах адреса данных интерфейса МПИ, в адресной части указанных циклов совпадает с адресом какого-либо регистра устройства, то, приняв этот адрес на группе входов 49 и на группе входоввыходов 11, стробированный фронтом синхроимпульса адреса,и приняв синхроимпульс ввода или вывода (синхроимпульсы адреса, ввода и вывода поступают на соответствующие входы группы входов 17 блока 4 от блока 1), блок 4 вырабатывает на выходе 19 синхроимпульс ответа, который через блок 1 поступает в интерфейс МПИ микроЭВМ, сопровождая вводимые или выводимые данные. Вводимые в микроЭВМ данные иэ адресованного регистра

РС или РД с выходов 22, а также входов-выходов ll поступают на группу

168 входов-выходов 12 блока 1, а с блока

1 - на интерфейс МПИ микроЭВМ.

Данные, считываемые из РС, интерпретируются как состояния периферийного УВВ, поступающие с группы выходов 36 блока 2 на группу входов 34 блока 4, а данные, считываемые из РД, интерпретируются как информация, передаваемая периферийным УВВ и поступающая с группы выходов 32 олока 2. на группу входов 30 блока 4, Выводимые из микроЭВМ данные с группы входов-выходов 12 блока 1 поступают на группу входов 21 и на группу входоввыходов 11 блока 4, и производится запись данных в PC или РЦ.

Данные, записываемые в PC интерпретируются как команды управления периферийным УВВ. Эти команды вызывают появления определенных сигналов управления на соответствующих выходах группы выходов 33 блока 4, которые через блок 2 поступают на УВВ.

Данные, записываемые в РД, интерпретируются как информация, передаваемая в периферийное УВВ, Эта инфор мация с группы выходов 29 поступает на группу входов 31 блока 2, а оттуда — на УВВ.

Если ни оди н и э переключателей узла 10 не включен, группа адресных входов 49 подключена непосредственно к соответствующим входам-выходам

12 блока 1 через подвижные контакты

48 и неподвижные нормально замкнутые контакты 52 переключателей группы

1О, а блок 8 не оказывает влияния на работу устройства. Задание адресов регистров PC и РД устройства осуществляется подачей на группу входов 23 блока 4 высоких и низких уровней напряжения с шин 26 и 28 через пе реключатели узла 3. Максимально возможное количество групп адресов регистров устройства в адресном пространстве микроЭВМ определяется формулой

N = N 2, (2)

1 где N - -максимально возможное коли45 чество групп адресов регистров устройства в адресном пространстве микроЭВМ;

N — возмжное количество групп адресов циклов регистров устройства, задаваемое переФ ключат еля ми узла 3; р - колич ест во адрес ных входов

49 блока 4, участвующих в переадресации, 5 Таким образом работает устройство в программном режиме. т

N=2 где m — количество входов 23 режима блока 4, участвующих в переадресации регистров.

Практически возможное количество групп адресов регистров блока 4 мень .ше, чем 2, и как правило, не превы. ( шает трех-четырех групп. Это означает, что к интерфейсу МПИ микроЭВМ мо

3249.

6 жет оыть одновременно подкпючено не более трех-четырех гаких устройств.

Если включен хотя бы один переключатель узла 10> соответствующий вход, например 49 ° группы адресных входов блока 4 через подвижный КоНТВКТ ,например 481 включенного перереключателя узла 10, подключен к выходу

10 соответствующего инвертора блока 8, например 51,, через контакт 50 . Таким образом, уровень сигнала соответствующего разряда как адреса, так и данных, поступающего на вход 49 1

15 блока 4, будет иметь инверсное, по

< сра внению с предыдущим примером, зна чение, т.е. адреса группы регистров устройства в данном случае уже будут иными, они будут отличаться от адре20 сов регистров предыдущего примера инверсным значением разряда адреса, поступающего на вход 49» блока 4 с группы входов-выходов 12 блока 1 через инвертор блока 8 и замкнутые кон2 такты 50), 48 узла 10. По окончании

-адресной части циклов ВВОД, ВЫВОД или ВВОД-ПАУЗА-ВЫВОД происходит обмен данными с микроЭВМ. 8 этой части циклов разряд данных на входе 49, 30 блока 4 будет иметь также инверсное значение, однако это не искажает работу устройства, так как в этой части ци клов и нформа ция на адресных входах

49 блока 4 не анализируется и, следо35 вательно, не имеет значения. Максимально возможное количество групп адресов регистров устройства в адрес" ном пространстве микроЭВМ с учетом введенных блока 8 и группы переклю40 чателей 10 будет определяться по формуле

П режиме прерываний в соответствующий бит регистров состояний

1688249 устройства записывает:R условие разрешения г>рерыва ния и далее центральный процессор (ЦП) микроЗВМ может за нимат bcR другой задачей „не занной с обсг>уживанием данного УВВ.

По какому-либо состоянию УВВ

I (например, по готовности на соответствующем выходе группь> выходов

14 блока 4 активирует;я сигнал 1О требования прерывания, поступающий через вход 16 блока 1 через интерфейс МПИ в ЦП. Последний, получив этот сигнал, завершает выполнение текущей кс>манды и выполняет цикл 15

ВВОД АДРЕСА ВЕКТОРА ПРЕРЫВАНИЯ (ВВОД

АВП) . ЦП посылает по соо ветс гвующим шинам интерфейса МПИ синхроимпульс ввода и синхроимпульс предоста вления прерывания. Синхроим-- 2О пул ьс ввода поступает с .оот ветствующего выхода 18 блока 1 на вход

17 бRoKB 4 Синхроимпуль.-: предоставления прерывания поступает с выхода

15 блока 1 на вход 13 блока 4. Если прерывания требоваг о не данное устройство, а другое, псдключенное к интерфейсу МПИ и имеющее более низкий приоритет по сравнению с данным устройством, данное устройство рет- 30 ранслирует синхроимпульс с предоставлением прерывания „

Ретранслируемый синхроимпульс предоста вления преры вани я с выхода 14 управления прерыванием бгока 4 посту" -, пает на вход 16 бгока 1,, а оттуда на интерфейс МПИ. Есг,и прерывания тре бует данное устройст е.,п, синхроимпугп«с предоставления прерыв а и!« i4e ретрансПируется данным устройс. вом, На вы- I. соде 14 блока -> и далее -Ia входе 16 блока 1 будет пасс.ивный уровень напряжения . Получи в си нхэои мпул ьс ы в во да и предоста вления прер ыва HMR, бг!G l

4 выставляет на своих входах-выходах: 45

11 восьмираэрядный адрес вектора пре" рывания (АВП), а на выходе 19 вырабатывает синхроимпульс ствета, поступающий на вход 20 блока 1 и сопровождающий вводимый в микро ."- ;:ВМ АВП. О

B отличие от циклов г,:рограммного обмена в цикле ВВОД АВП синхроимпульс адреса не вырабатываетсR и га соответствующем вход,.:. 17 и на вхсде 37 элемента НЕ 5 будет в те-:ение всего этого цикла пассивный уровень напряжения, АВП, введенный в ми кроЗВМ, ука:зывает на я чей ку памяти ми кроЗВМ „в которой указан, ->ачал «ный адрес годпрограммы обслуживания прерывания от данного устройства. Управленйе передается этой подпрограмме, в конце которой в соответствующий бит РС устройства вновь записывается условие разрешения прерывания, и осуществляется выход из прерывания. Возобновляется выполнение прерванной программы с того места, где она была прервана. ЦП может заниматься этой.программой до прихода очередного требования прерывания от устройства и т.д.

Если ни один из переключателей узла 9 не включен, на информационных выходах блока 7 канальных передатчиков p цикле ВВОД АВП будут пассивные уровни напряжения и блок 7 не оказывает влияния на вводимый устройством АВП, Задание адресов векторов прерываний устройства осуществляется таким же образом, как и задание адресов регистров РС и РД, т.е, подачей на входы 23 блока 4 высоких и низких уровней напряжений с шин 26 и 28 через переключатели узла 3. Иными cJlQBB ми, одновременно с заданием этими переключателями определенной группы адресов регистров РС и РР, задается и определенная группа АВП устройства. Ма ксимально возможное количество групп АВП в адресном пространстве ми кроЗВМ в этом случае определяется формуггой (1), а практически возможное количество групп АВП БИС 4 не превышает трех-четырех групп, что делает невозможным одновременное подключение большего „чем три-четыре количества таких устройств, работающих в режиме прерываний, к интерфейсу МПИ микроЗВМ.

Если включен хотя бь: один из переключателей узла 9, на соответствующий информационный вход блока 7 канальных передатчиков поступает активный низкий уровень напряжения. l3 этом случае устройство работает в цикле ВВОД АВП следу ющи м обра зом. В момент поя вления на выходе 19 блока "> си чхроимпул ьса ответа на выходе 41 элемента И 6 активируется импульс разоешения „поступающий на управгяющий вход 42 блока

Зтот импульс будет активен до конца текущего цикла ВВОД АВП, Информация с входов 43 поступает на выходы

47 блока 7, т.е. на входы-выходы 12 блока 1. При этом АВП, формируемый1 на группе входов-выходов 12 бг>ока 1, является поразрядной диз ьюнкцией сигна1688249 лов группы входов-выходов 11 младших восьми разрядов адреса данных блока 4 и сигналов выходов 47 блока 7, причем ABA может быть, как и раньше, восьмиразрядным или, при неооходимости, может иметь большую разрядность, Максимально возможное количество групп АВП устройства в адресном пространстве микроЭВИ определяется фор- 1л мулой Q) . и =юг, (3)

tI где N — максимально возможное количество групп АВП устройства в аДресном пространстве микроЭВИ, N — возможное количество групп

АВП устройства, задаваемое переключателями узла 3; 2р n — количество выходов 47 ...47п блока 7 канальных передатчи ков, Формула и зобрет ения 25

Устройство для согласования интер" фейсов, содержащее блоки усиления первого и второго интерфейсов, блок обратимого преобразования параллель- . 3p ного кода в последовательный, группы информа ционных входов- выходов, входов и выходов соединены соответственно с группами информационно-адресных вхо ! дов-выходов, выходов и входов блока . усиления первого интерфейса, а информационные вход и выход и синхронизирующие вход и выход - соответственно с информационными выходом и входом и синхронизирующими выходом 40 и входом блока усиления второго ин" терфейса, и три узла переключателей, причем группы выходов первого и второго узлов переключателей подключены соответственно к группам входов режима и адреса блока обратимого преобразования параллельного кода в последовательный, вход разрешения прерывания, выход сигнала прерывания, группа входов синхронизации и выход ответа которого подключены соответственно к выходу сигнала разрешения прерывания, входу сигнала прерывания, группе выходов сигналов синхронизации ввода-вывода и входу сигнала ответа блока усиления первого интерфейса, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства путем обеспечения возможности увеличения числа внешних устройств, подключаемых к первому интерфейсу, в устройство введены блок канальных передатчиков, блок элементов НЕ, элемент И и элемент НЕ, причем группа выходов блока канальных передатчиков и группа входов блока элементов НЕ соединены с группой информационных входов-выходов блока усиления первого интерфейса, группа выходов третьего узла переключателей подключена к группе входов блока канальных передатчиков, управляющим входом соединенного с выходом элемента И, первый и второй входы которого соединены соответственно с выходом ответа блока обратимого преобразования параллельного кода в последовательный и выходу элемента НЕ, входом. подключенного к группе выходов син хронизации ввода-вывода блока усиления первого интерфейса, группа входов второго узла переключателей соединена с группой выходов блока., элементов НЕ.

1683249

Редактор С.Лисина

Производственно-издательский комбинат "Патент", r.Óæãoðoä, ул.Гагарина, 101

За каз 3709

ВНИИПИ Государственнсго

113035, Составитель В. Вертлиб

Техред л.олийнык . Корректор С.йекмар

1 H p<32K Подписное комитета по изобретениям и открытиям при ГКНТ СССР

Москва, Ж-35,, Раушская наб., д. 4/5