Устройство для решения систем линейных алгебраических уравнений

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительном технике и мокет бьггь использовано для решения систем линейных алгебраических уравнений. Цель изобретения - сокращение аппаратурных затрат за счет уменьшения количества блоков вычислений. Устройство содержит п бпоков 1 вычислении, где п - порядок решаемой системы линейных алгебраических уравнений, блок 2 суммирования , блок 5 анализа, блок 6 синхронизации , первый 7 и второй 8 элементы задержки. Данное устройство предназначено для нахождения решения СЛАУ итерационным методом Гаусса-Зейделя. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНих

РЕСПУБЛИК ($f)g С 06 F 15/324 х = Ах + Ь, х,= у. + 2,, I I 4 (2) где

K у (3) ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

И А ВТОРСИОМУ СВИДЕТЕЛЬСТВУ (21) 4663211/24-24 (22) 10.03.89 (46) 30.10.91. Бюл. И- 40 (71) Физико-механический институт им. Г.В.Карпенко (72) В.Я.Мыхальчишин (53) 681.325 (088.8) (56) Авторское свидетельство СССР

N - 1615739, кл. С 06 F 15/324, 13.02 ° 89.

Авторское свидетельство СССР

11 1566367, кл. С 06 F 15/324, 03.01.89. (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ

ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ

Изобретение относится к цифровой вычислительной технике и может быть использовано для нахождения решения систем линейных алгебраических уравнений.

Цель изобретения — сокращение аппаратурных затрат путем уменьшения количества блоков вычислений.

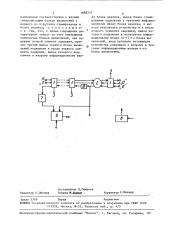

На чертеже представлена схема устройства для решения систем линейных алгебраических уравнений.

Устройство содержит и блоков вычислений 1, где n — порядок системы линейных алгебраических уравнений, блок 2 суммирования, и входов 3 коэффициентов системы линейных алгебраических уравнений устройства, вход 4 свободных членов системы линейных алгебраических уравнений устройства, блок 5 анализа, блок 6 синхронизации, первый и второй элементы 7 и 8 задержек. !

„„SU„„1688251 А 1

2 (57) Изобретение относится к цифровой вычислительной технике и может быть использовано для решения систем линейных алгебраических уравнений. Цель изобретения — сокращение аппаратурных затрат эа счет уменьшения количества блоков вычислений. Устройство содержит и блоков 1 вычислений, где ив порядок решаемой системы линейных алгебраических уравнений, блок 2 суммирования, блок 5 анализа, блок 6 синхронизации, первый 7 и второй 8 элементы задержки. Данное устройство предназначено для нахождения решения

СЛАУ итерационным методом Гаусса-Зейделя. 1 ил.

С::

Устройство предназначено для нахождения решения системы линейных ал- ф гебраических уравнений где А — nxn матрица коэффициентов, х и Ь вЂ” соответственно вектор неизвестных и вектор свободных членов раэмерности и.

Решение системы (1) находится в виде (метод Гаусса-Зейделя):

1-2 к и

К-1 а; х + a, х +Ь °, ) 1 1 j 1 )

1 i n ь-! ,0,а х ° +Ь, i= f к-

7688257

7

31 I! В

z °

y° . I а ° х

,И !1

5 где 7. — шаг итерации „

Устройство работает следующим образом, Перед началом работы устройства в блок 5 анализа через вход задания 7Q точности устройства записывается число, задающее требуемую точность решения системы линейных алгебраических уравнений, При поступлении тактовых импульсов от блока 6 синхронизации происходит считывание данных с входов 3 устройства. На каждой итерации, длительность которой равна 2п тактов, структура входных данных остается постоянной. За начальное приближение 2() компонент вектора неизвестных принимаются значения, зарегистрированные в начальный момент в регистрах-фик-. саторах соответствующих блоков 1 вычислений и блока 2 суммирования. 25

На каждом такте работы устройства в каждом блоке 1 вычислений одновременно осуществляются операция умножения значений, поступающих на входь! первого и четвертого операндов блока

1, и операция сложения значений, поступающих на входы второго и третьего операндов блока 1. В блоках 1 вычислений с первого по (n — 1)-й происходит последовательное вычисление слагаемых у, согласно (!). n-й блок вычислений, который служит для вычисления z согласно формуле (4), поэволяК

I ет использовать новую компоненту вектора неизвестных, найденную на преды40 дущем такте, при вычислении следующей компоненты вектора неизвестных.

Второй элемент задержки, осуществляющий задержку длительностью два такта, позволяет использовать новую компо45 ненту вектора неизвестных при вычислении последующих компонент, которое будет производиться в (n-1) блоках 1 вычислений, Суммирование слагаемых ,у, и z., которые вычисляются в предK K

I I шествующем такте в (и- l) ì и и-и блo- 5 ках 1 соответственно, происходит в блоке 2 суммирования одновременно с последуюшнм суммированием полученных результатов согласно (2). г

В блоке 5 анализа вычисляется раз- 15 ница (х7 — х ° ((i = 1,n) значений

К - I !

l компонент вектора неизвестных, полученных íà k-й и (k-1)-й итерациях, и сравнивается с заданным пор огом точности, Для одновременного поступления на входы блока 5 анализа значений х. с и х осуществляется задержка эначеМ-I ния х, на п тактов. При удовлетво-! ренин заданной точности на выходе признака останова устройства появляется признак получения решения и с выхода результата устройства снимаются найденные значения вектора неизвестных, Формула изобретения

Устройство для решения систем линейных алгебраических уравнений, содержащее с первого по и-й блоки вычислений (где п — порядок решаемой системы линейных алгебраических уравнений), блок суммирования, блок синхронизации, блок анализа и первый элемент задержки, причем входы с первого по и-й коэффициентов системы линейных алгебраических уравнений устройства подключены соответственно к первым информационным входам блоков вычислений с первого по п-й, первый и второй выходы 1.-FQ блока вычислений (где i. =- 1,..., n-2) подключены соответственно к второму и третьему информационным входам (i+1)-ro блока вычислений, вход свободных членов системы линейных алгебраических уравнений устройства подключен к второму информационному входу первого блока вычислений, первый и второй выходы (п-1)-ro блока вычислений подключены соответственно к входам первого и второго операндов блока суммирования, вход нулевого потенциала устройства подключен к третьему информационному входу первого блока вычислений, четвертый информационный вход i-го блока вычислении подключен к третьему информационному выходу (i+1)-ro блока вычислений, первый и второй выходы и го блока вычислений подключены соответственно к входам третьего и четвертого операндов блока суммирования, выход которого подключен к четвертому информационному входу п-го блока вычисления, вход задания точности устройства подключен к первому информационному входу блока анализа, выход которого подключен к выходу признака останова устройства, вход запуска которого подключен к тактовому входу блока синхронизации, выходы которого

168825

Составитель В.Смирнов

Техред М.Дрык

Корректор С.Иекмар

Редактор С.Лисина

Заказ 3710 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при .ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 подключены соответственно к входам синхронизации блоков вычислений с

1 первого по п-й,блока суммирования и блока анализа, о т л и ч а ю щ е ес я тем, что, с целью сокращения ап5 паратурных затрат эа счет уменьшения количества блоков вычислений, оно содержит второй элемент задержки, причем третий выход первого блока вычис- 10 лений подключен к- входу первого элемента задержки, выход которого подключен к второму информационному вхо7 6 ду блока анализа, выход блока суммирования подключен к третьему информационному входу блока анализа, к выходу результата устройства и к входу второго элемента задержки,. выход которого подключен к четвертому информационному входу (и-1)-го блока вычислений, вход нулевого потенциала устройства подключен к второму и третьему информационным входам и-го блока вычислений.