Устройство для вычисления свертки

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки радиолокационных, видео, сейсмических , гидроакустических и других сигналов . Цель изобретения - -расширение функциональных возможностей за счет вычисления автокорреляционной функции . Устройство содержит группы умножителей , регистры входных данных, инверторы , триггеры, синхронизатор, триггеры режима, четырехвходовые мультиплексоры, элементы И, регистры операндов, умножители, сумматоры первой группы, сумматоры второй группы, регистры суммы, двухвходовые мультиплексоры , регистры. 4 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (gg)g G 06 Р 15/336, 15/353

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

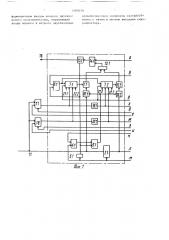

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,, Н A BTOPCHOMY СВИДЕТЕЛЬСТВУ регистры операндов 10.i (i = 1,N), информационный вход 11 группу умножителей, группу 13 сумматоров, группу 14 сумматоров, регистры сум- мы 15 i выход устройства 16 двувходовые мультиплексоры 17 и 18, СЬ группы 19 и 20 регистров, входы 21 и 22 коэффициентов импульсной характеристики.

Синхронизатор (фиг. 4), реализованный для N = 4, содержит счетчик 21 О по модулю N, дешифратор 22, элемент С©. .И-НЕ 23, элемент И 24, триггеры 25 и 26, демультиплексор 27, инвертор

28, генератор 29 тактовых импульсов.

Работа устройства при вычислении юФ корреляции входного массива. 30

Устройство вычисляет следующее выражение: й-<

R(K) = Х )n + К)„Х(п), К = 0, N-1, h=0

f1) (21) 4767052/24 (22) 06.12.89 (46) 30.10.9 1. Бюл. Р 40 (71) Киевский политехнический инсти- . тут им. 50-летия Великой Октябрьской социалистической революции (72) Ю.С.Каневский, Д.В.Корчев, H.Ê.ÊëèìåHêo и N.Ñ.Âåñåëüñêàÿ (53) 681.3 (088,8) (56) Авторское свидетельство СССР

Р 1314352, кл. G 06 F 15/353, 1985, (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СВЕРТКИ (57) Изобретение относится к вычислительной технике и может быть испольИзобретение относится к вычислительной технике, предназначено для вычисления корреляционной функции и процедуры цифровой фильтрации и может быть использовано в системах цифровой обработки различного рода .сигналов.

Целью изобретения является расширение функциональных возможностей . устройства путем вычисления на данном устройстве автокорреляционной функции.

На фиг. 1-3 изображена структурная схема устройства; на фиг.4 — пример выполнения функциональной схемы синхронизатора.

Устройство (фиг. 1-3) содержит группу 1 умножителей, регистры 2 входных данных, инверторы З.i триггеры 4.i, синхронизатор 5, триггеры

6. режима, четырехвходовые мультип:.лексоры 7,i, входы 8.1 и 8.2 задания режима устройства, элементы И 9.1

„.,30.„1688259 A 1 зовано в системах цифровой обработки радиолокационных, видео, сейсмических, гидроакустических и других сигналов. Цель изобретения — .расширение функциональных возможностей sa счет вычисления автокорреляционной функции. Устройство содержит группы умножителей, регистры входных данных, инверторы, триггеры, синхронизатор, триггеры режима, четырехвходовые мультиплексоры, элементы И, регистры операндов, умножители, сумматоры первой группы, сумматоры второй группы, регистры суммы, двухвходовые мультиплексоры, регистры. 4 ил.

1688259

Х(0),..., X(3) R(0)

R(3) (2) К(2)

Е(1) Х(3) Х(2) Х(3) Считаем, что операнды в регистры

2. х, 15 ° i 10. 1. б, i 19. i 20. i принимаются по переднему фронту синхроимпульса (для простоты синхросвязи регистров 19.i и 20.i не показаны), режиму вычисления корреляции входного массива соответствует значение 11 на входах 8,1 и 8,2 синхронизатора 5.

С целью идентичного представления 25 модулей второй вход сумматора 14.N/2 соединен с шиной логического нуля, для ограничения числа входов и сохранения работоспособности модуля, инвертор 3.1. синхросигнала введен в каждый модуль. С выхода генератора тактовых импульсов поступает синхросигнал в виде меандра.

На примере N = 4 рассмотрим работу устройства при вычислении корреляции входного массива, Зэ

Устройство для вычисления свертки, содержащее две группы по N/2 умножителей, N/2 сумматоров первой группы, N/2 сумматоров второй группы, N/2 регистров суммы, N/2 регистров входных данных, причем вход первого регистра входных данных является информационным входом устройства, вход

i-ro (i = 2, ..., N/2) регистра входных данных соединен с выходом (-1)- го регистра входных данных, выход где Х (и) — ..лемеHòû входного массива

p;lзмерности N;

С Я вЂ” где С остаток от деления а на

R(K) — 1(— и отсчет корреляционной функции, Для N = 4 выражение (1) в матричНой форме можно записать следующим образом:

Первый такт. В исходном состоянии в триггеры б.i и 4.i записаны нули, на входе 11 устройства присутствует

Операнд Х (О) . На управляющий вход 40 .мультиплексора 17 с пятого выхода синхронизатора 5 подается единичное

Эначение, а на управляющий вход мультиплексора 18 подается нулевое значеНие с шестого выхода синхронизатора 45

5. Положительным перепадом синхроим-. йульса операнд Х (0) записывается в регистр 2.1, а положительным nepenafl,ом инвертированного синхроимпульса— в регистр 19.1. На информационный 50 вход триггера 4.2 приходит единичное .значение с второго выхода синхронизатора 5, а на информационный вход триггера 6.2 — единичное значение с третьего выхода, так как передний фронт синхроимпульса приходит раньше, чем происходит изменение на информацион,ном входе триггеров, то состояние триггеров 6.2 и 4,2 не изменяется, I не изменяется состояние и триггеров

6.1 и 4,1.

Дальнейшая работа устройства осуществляется подобным образом за семь тактов.

Если требуется вычислять линейную корреляцию, то соответствующее количество входных отсчетов заполняется нулями.

При реализации процедуры цифровой фильтрации устройство вычисляет выходные отсчеты фильтра в соответствии с выражением

¹<

Х(К) = 0 а(К вЂ” и) h(n), (3)

n=o где h(n) — коэффициенты импульсной характеристики фильтра, a(n) — отсчеты выходного сигнала.

Устройство может выполнять цифровую фильтрацию с двумя различными импульсными характеристиками. Первый режим цифровой фильтрации соответствует управляющим сигналам 10 на входах 8 ° 1 и 8.2 соответственно. Коэффициенты первой импульсной характеристики поступают соответствующим образом на входы 2 1.i и не изменяются в процессе вычислений. Второй режим цифровой фильтрации соответствует коду 01 на управляющих входах 8. 1 и 8.2 управления, это обеспечивает установку триггеров 4.i в единичное состояние и тем самым обеспечивается прием исходных операндов в каждом такте в регистры 10,1 — 10.N. На первый управляющий вход коммутаторов 7.1 — 7,4 подается высокий уровень, а на второй управляющий вход — низкий, этим обеспечивается постоянное поступление на вход 22.i коэффициента h(i). Первый выходной отсчет фильтра получаем через N/2 тактов, в каждом следующем такте на выход фильтра появляется новый отсчет.

Формула изобретения

1688259

1-го 1 = l, ..., N/2 (умножителя первой группы соединен. с первым входом j-го сумматора первой группы, выход j-го умножителя второй группы

5 соединен с вторым входом j-го сумматора первой группы, выход которого соединен с первым входом j-ro сумматора второй группы, выход которого соединен с информационным входом j-ro 10 регистра суммы, выход i-го регистра суммы соединен с вторым входом (i-1)ro сумматора второй группы, выход первого регистра суммы является выхоpoM rT oHoTB, BTo oH o N/2-го 15 сумматора второй группы соединен с шиной нулевого потенциала, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет вычисления автокорреля- 20 ции, в него введены N/2 инверторов, группа из N/2 триггеров, N/2 элементов И, N регистров операндов, N/2 триггеров режима, две группы регистров, N четырехвходовых мультиплексо- - 25 ров, два двухвходовых мультиплексора и синхронизатор, первый и второй входы задания временных параметров которого являются входами задания режима устройства, первый выход синхрониза- у) тора соединен с с. инхровходами регистров входных данных и регистров первой и второй групп, с входами инверторов и с синхровходами триггеров группы, информационный вход первого регистра операнда и первые информационные входы первого и второго двухвходовых мультиплексоров подключены к информационному входу устройства, выход (i-1)-го регистра входных данных

40 соединен с информационными входами (2i-2)-ro и (2i-1)-го. регистров операндов, выход i-го регистра входных данных соединен с информационным входом N-го регистра операндов, первый 45 вход j ãî умножителя первой группы соединен с выходом (2j-1)-ro регистра операнда, первый вход j-го умножителя второй группы соединен с выходом

2j-ro регистра операнда, второй вход

j-го умножителя первой группы соединен с выходом (2j-1)-го четырехвходбвого мультиплексора, второй вход j-го умножителя второй группы соединен с выходом 2j-го четырехвходового муль55 типлексора, выход j-ro элемента И соединен с синхровходами (2 j-1) -ro и

2j-ro регистров операнда, первый вход, j-го элемента И соединен с прямым выходом j-ro триггера группы, а второй вход — с выходом j-го инвертора и синхровходами j-x триггеров режима и регистра суммы, прямой выход 1-го триггера группы соединен с информационным входом (i-1)-го триггера группы, прямой вход N/2-го триггера груп-, пы соединен с вторым выходом синхронизатора, прямой выход первого триггера режима соединен .с первыми управляющими входами первого и второго четырехвходовых мультиплексоров, прямой выход >-ro триггера режима соединен с первыми управляющими входами (2i— 1)-го и 2i.-ro четырехвходовых мультиплексоров и информационным входом (i-1)-ro триггера режима, информационный вход N/2-го триггера режима соединен с третьим выходом синхронизатора, четвертый выход которого соединен с вторыми управляющими входами четырехвходовых мультиплексоров, первые и вторые информационные входы которых являются соответственно входами задания коэффициентов первой и второй импульсных характеристик устройства, выход первого двухвходового мультиплексора соединен с третьим информационным входом первого четырехвходового мультиплексора и информационным входом первого регистра первой группы, выход (i-1)-го регистра первой группы соединен с третьими информационными входами (2i-2)-го и (2i-1)го четырехвходовых мультиплексоров и информационным входом -ro регистра первой группы, выход (i + N/2 — 1)ro регистра первой группы соединен с информационным входом (i + N/2)-го регистра первой группы, выход N-ro регистра первой группы соединен с вторым информационным входом первого двухвходового мультиплексора, выход второго двухвходового мультиплексора соединен с четвертым информационным входом первого четырехвходового мультиплексора и информационным входом первого регистра второй группы, выход (i-1)-го регистра второй группы соединен с четвертыми информационными входами (2i-2)-го и (2i-1)-го четырехвходовых мультиплексоров и информационным входом i-го регистра второй группы, выход (i + N/2 — 1)-го реги- стра второй группы соединен с информационным входом (i + N/2)-ro регистра второй группы, выход N-го регистра второй группы соединен с вторым ин1«i 82 9 формаци. нным входом второт о двухвходового мультиплексора, управляющие входы первого и второго двухвходовых мультиплексоров соединены соответственно с пятым и шестым вьгсодами синхрониаатора.

1688259

Составитель 8 ° Îðëîâ

Техред М.Дидык Корректор Л,Пилипенко

Редактор С.Лиснна

Заказ 3710 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, .Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óærîðîä, ул..Гагарина,101