Импульсно-фазовый дискриминатор

Иллюстрации

Показать всеРеферат

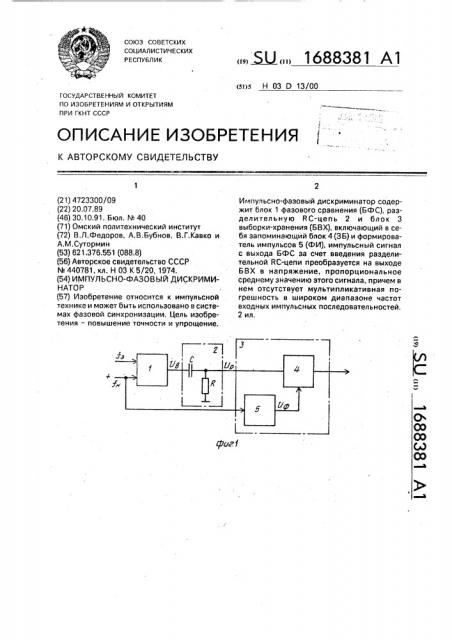

Изобретение относится к импульсной технике и может быть использовано в системах фазовой синхронизации. Цель изобретения - повышение точности и упрощение. Импульсно-фазовый дискриминатор содержит блок 1 фазового сравнения (БФС), рэзделительную RC-цепь 2 и блок 3 выборки-хранения (БВХ), включающий в себя запоминающий блок 4 (ЗБ) и формирователь импульсов 5 (ФИ), импульсный сигнал с выхода БФС за счет введения разделительной RC-цепи преобразуется на выходе БВХ в напряжение, пропорциональное среднему значению этого сигнала, причем в нем отсутствует мультипликативная погрешность в широком диапазоне частот входных импульсных последовательностей. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 0 13/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4723300/09 (22) 20.07.89 (46) 30.10.91. Бюл. N 40 (71) Омский политехнический институт (72) В.Л.Федоров, А.В.Бубнов, В.Г.Кавко и

А.М.Сутормин (53) 621.376.551 (088.8) (56) Авторское свидетельство СССР

f+ 440781, кл. Н 03 К 5/20, 19?4. (54) ИМПУЛЬСНО-ФАЗОВЫЙ ДИСКРИМИНАТОР (57) Изобретение относится к импульсной технике и может быть использовано в системах фазовой синхронизации, Цель изобретения — повышение точности и упрощение, „„5U„„1688381 А1

Импульсно-фазовый дискриминатор содержит блок 1 фазового сравнения (БФС), разделительную RC-цепь 2 и блок 3 выборки-хранения (БВХ), включающий в себя запоминающий блок 4 (ЗБ) и формирователь импульсов 5 (ФИ), импульсный сигнал с выхода БФС за счет введения разделительной RC-цепи преобразуется на выходе

6ВХ в напряжение, пропорциональное среднему значению этого сигнала, причем в нем отсутствует мультипликативная погрешность в широком диапазоне частот входных импульсных последовательностей, 2 ил.

1688381

Изобретение относится к импульсной технике и может быть использовано в системах фазовой синхронизации.

Цель изобретения — увеличение точности и упрощение, На фиг,1 приведена структурная электрическая схема импульсно-фазового дискриминатора; на фиг.2 — временные диаграммы его работы, Импульсно-фазовый дискриминатор содержит блок 1 фазового сравнения, разделительную RC-цепь 2 и блок 3 выборки-хранения. Входы блока 1 фазового сравнения подключены к источникам эталонной и контролируемой частот.

Блок 1 фазового сравнения служит для фазового сравнения импульсов эталонной и контролируемой частот и формирования последовательностии импульсов, период следования которых равен периоду эталонной частоты, а длительность пропорциональна величине фазового рссогласования сравниваемых частот. Блок t фазового сравнения может быть выполнен, например, в виде RSтриггера.

Разделительная цепь 2 служит для преобразования выходного сигнала блока 1 фазового сравнения в импульсный сигнал, в котором отсутствует постоянная составляющая, и может бьггь выполнена в виде последовательно соединенных конденсатора и резистора.

Блок 3 выборки-хранения служит для запоминания выходного сигнала разделительной RC-цепи 2 в моменты поступления импульсов контролируемой частоты. Блок. 3 выборки-хранения может быть выполнен в виде запоминающего блока 4 и формирователя импульсов 5, Выход формирователя импульсов 5 подключен к управляющему входу запоминающего блока 4, информационный вход которого является информационным входом блока 3 выборки-хранения.

Формирователь импульсов 5 служит для формирования (по переднему фронту импульсов контролируемой частоты) коротких импульсов выборки и может быть выполнен, например, в виде одновибратора, Устройство работает следующим образам, Импульсы эталонной и контролируемой частот поступают на вход блока 1 фазового сравнения (фиг.2). Блок i фазового сравнения формирует последовательность импульсов, период следования которых равен периоду Тэ эталонной частоты, а длительность пропорциональна величине фазового рассогласования сравниваемых частот, Форма выходного напряжения Ui блока фазового сравнения приведена на фиг.2в. Если параметры разделительной RC-цепи 2 выбраны так, что

4 RC то разделительная цепь не искажает форму входного сигнала. При этом постоянная составляющая в выходном сигнале Up с разде10 лительной цепи 2 (фиг.2) отсутствует и амплитуда отрицательного импульса 02 выходного сигнала равна среднему за период напряжению входного сигнала

«г1 U

02=Ucp =

Тэ т1 0 =-(Т вЂ” т1) 02 (2) 30 „ (3) U1+U2 =0

Отсюда

ri u г Щ + Uz

Т Т

Подставляя (2) в (4), 40

02Тэ <1 02 +Т1 02 0

Оcp 02

Выходной сигнал разделительной RCцепи 2 поступает на информационный вход блока 3 выборки-хранения, состоящего из запоминающего блока 4 и формирователя импульсов 5. Последний формирует короткие импульсы выборки по переднему фронту импульсов контролируемой частоты, а запоминающий блок 4 запоминает амплитуду отрицательных импульсов 02 выходного сигнала разделительной RC-цепи 2 в моменты поступления импульсов выборки. Таким образом на выходе импульсно-фазового дискриминатора формируется напряжение, пропорциональное фазовому рассогласование сравниваемых импульсных последовател ьностей (фиг.2д). где U — амплитуда выходных импульсов блока фазового сравнения;

20 t1 — длительность выходных импульсов блока фазового сравнения; т2 =- Т вЂ” г1 — длительность паузы выходных импульсов фазового сравнения;

Так как постоянная составляющая в вы25 ходном сигнале разделительной RC-цепи отсутствует, то

1688381

fý — RC — =0г

fH = f3 =

Оф д

Расчеты показывают, что коэффициент передачи такого импульсно-фазового дискриминатора остается постоя н н ым во всем диапазоне частот

Расчетная зависимость относительного коэффициента передачи предлагаемого устройства от относительной частоты где Кн — коэффициент передачи устройства на частоте

Таким образом, предлагаемое техническое решение обеспечивает увеличение точности эа счет снижения мультипликативной погрешности и является более простым, чем прототип, из-за отсутствия элемента задержки и разрядного ключа.

5 Простота реализации предлагаемого технического решения позволяет широко использовать его в устройствах автоматики.

Формула изобретения

10 Импульсно-фазовый дискриминатор, содержащий блок фазового сравнения и блок выборки-хранения, входы блока фазового сравнения подключены к источникам эталонной и контролируемой частот, о т л и15 ч а ю шийся тем, что, с целью увеличения точности и упрощения, введена разделительная RC-цепь, вход которой подключен к выходу блока фазового сравнения, выход разделительной RC-цепи подключен к ин20 формационному входу блока выборки-хранения, а управляющий вход блока выборки-хранения подключен к источнику контролируемой частоты.