Устройство цикловой синхронизации блочных кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к промышленности средств связи. Цель изобретения - уменьшение времени вхождения в синхронизм . Устройство цикловой синхронизации блочных кодов содержит блок 1 разделения сигналов, дешифратор 2, анализатор 3 кодовых комбинаций, блок 4 определения нарушения чередования инвертируемых, элемент ИЛИ-НЕ 5, распределитель 6 циклов , формирователь 7 сдвига фазы и блок 6 управления. Цель достигается путем подсчета определенного числа ошибок блоком 6 и изменения коэффициента деления распределителя , чем достигается сдвиг цикловой синхронизации на 1 такт. Процесс повторяется до установления цикловой синхронизации . 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (и)5 Н 04 L 7/08

ГОСУДАPСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1о ОО (л)

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4689333/09 (22) 20.03.89 (46) 30.10.91. Бюл. hh 40 (72) В,Ю.Васильев, Б.М,Певзнер, В.M.Ñìèðнов,В.Я.Сорин и P.È.Øóòèí (53) 621.394.662(088.8) (56) Вклад в МККР Nasse О. The ThomsonCSF 88 — 98 code for digital television serial

InterconnexIons, (приложение 3, Fig, F). (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОЧНЫХ КОДОВ (57) Изобретение относится к промышленности средств связи. Цель изобретения— уменьшение времени вхождения в синхро! Ы, 1688434 А1 низм, Устройство цикловой синхронизации блочных кодов содержит блок 1 разделения сигналов, дешифратор 2, анализатор 3 кодовых комбинаций, блок 4 определения нарушения чередования инвертируемых, элемент ИЛИ-НЕ 5, распределитель 6 циклов, формирователь 7 сдвига фазы и блок 6 управления. Цель достигается путем подсчета определенного числа ошибок блоком

6 и изменения коэффициента деления рапределителя, чем достигается сдвиг цикловой синхронизации на 1 такт. Процесс повторяется до установления цикловой синхронизации. 4 ил, 1688434

55.Изобретение относится к промышленности средств связи и может быть использовано при построении устройств цикловой синхронизации в системах передачи информации, преимущественно в системах передачи цифровой телевизионной информации.

Целью изобретения является уменьшение времени вхождения в синхрониэм.

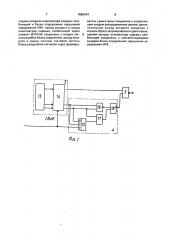

На фиг. 1 представлена структурная электрическая схема устройства цикловой синхронизации блочных кодов; на фиг. 2— анализатор кодовых комбинаций (КК) и блок определения нарушения чередования инвертируемых кодов комбинаций, варианты выполнения; на фиг. 3 — распределитель циклов, блок управления и формирователь сдвига фазы, варианты выполнения; на фиг, 4 — временные диаграммы, поясняющие работу устройства цикловой синхронизации блочных кодов.

Устройство цикловой синхронизации блочных кодов содержит блок 1 разделения сигналов, дешифратор 2, анализатор 3 (КК), блок 4 определения нарушения чередования инвертируемых КК, элемент ИЛИ-НЕ 5, распределитель 6 циклов, формирователь 7 сдвига фазы и блок 8 управления, В состав дешифратора 2 входят сдвиговый регистр 9, параллельный регистр 10, программируемый постоянный запоминающий блок (ППЗБ) 11 и параллельный регистр 12. В состав анализатора 3 КК входят ППЗБ 13 инвертируемых и запрещенных КК и блок 14 памяти. Блок 4 определения нарушения чередования ИКК содержит 1К-триггер 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 16, элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ 17 и элемент ИЛИ-НЕ

18. В состав распределителя 6 циклов входят делитель 19 и инвертор 20. Блок 8 управления содержит счетчик 21 импульсов, элемент

ИЛИ-НЕ 22, инвертор 23, элемент ИЛИНЕ/ИЛИ 24 и элемент ИЛИ-НЕ 25.

Устройство цикловой синхронизации блочных кодов работает следующим образом, При сбое цикловой синхронизации анализатор 3 КК в параллельном коде, поступающем с выходов параллельного регистра 10 дешифратора 2, выделяет факт наличия запрещенных КК или посредством блока 4 определения нарушения чередования инвертируемых КК нарушение чередования инвертируемых КК и формируют на элементе ИЛИ-НЕ 5 сигнал ошибки, который поступает s блок 8 управления. Счетчик 21 блока

8 управления считает до N ошибок. После прихода (N+ 1)-й ошибки блок 8 управления вырабатывает сигнал, по которому форми5

50 рователь 7. выполненный, например, в виде

О-триггера, сдвигает распределитель 6 циклов на один такт. Одновременно счетчик 21 блока 8 управления устанавливается в исходное состояние, Входной сигнал поступает на вход 6пока 1 разделения сигналов, усиливается и нормируется по амплитуде и поступает на вход сдвигового регистра 9 дешифратора 2.

Запись информации в сдвиговый регистр 9 происходит по положительному фронту тактовой частоты. По положительному фронту частоты, получаемой в распределителе 6 циклов путем деления делителем 19 тактовой частоты на девять и передаваемой через инвертор 20, происходит запись информации из сдвигового регистра 9 в параллельный регистр 10. Параллельный код с выхода параллельного регистра 10 поступает в

ППЗБ 11, запрограммированный так, что по входным словам пВ происходит преобразование п — mB, в параллельный регистр 12 записывается код mB.

С выходе регистра 10 дешифратора 2 параллельный код поступает на входы

ППЗБ 13 анализатора 3 КК. Причем ППЗБ 13 запрограммирован так, что по входным словам и В на выходах его вырабатываются сигналы, соответствующие признакам инвертируемых КК и признакам запрещенных

КК. В частности, для кода 8В-9В в качестве инвертируемых КК используются КК 6/3 и

3/6 (соответственно по содержанию в кодовом слове 9В шести "1" и трех "0" — 6/3, трех

"1" и шести "0" — 3/6, При безошибочной передаче информации на выходе блока 14 памяти (второй выход анализатора 3 КК) вырабатывается сигнал "0", который поступает на вход элемента ИЛИ-НЕ 5. На выходах блока 14 памяти (первый выход анализатора 3 КК) при передаче инвертируемых КК, в частности

6/3 и 3/6, вырабатываются сигналы "0" и "1" соответственно, а при передаче остальных

КК вЂ” сигналы "1", В первом случае триггер

15 устанавливается по сигналу на тактовом входе в единичное (нулевое) состояние, во втором случае — по сигналам "1" на входахЧ и К вЂ” состояние триггера 15 сохраняется, С приходом следующей инвертируемой КК, которая в соответствии с чередованием КК должна иметь уже обратное соотношение

"0" и "1" на выходах блока 14 памяти, сигнал

"0" ("1") поступает на первый вход элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 17, на втором входе которого установлен сигнал "1 "("0") с выхода триггера 15. При этом на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 17 вырабатывается сигнал "1", который через элемент ИЛИ-НЕ 18 "0" поступает на второй

1688434

55 вход элемента ИЛИ-НЕ 5, а триггер 15 по сигналу на тактовом входе устанавливается в нулевое (единичное) состояние, которое сохраняется до прихода следующей инвертируемой КК, По нулевым логическим сигналам на входах элемент ИЛИ-НЕ 5 выдает сигнал ло:1ческой единицы, что соответствует безошибочной передаче информации, При появлении запрещенной КК на выходе блока 14 пэмчти (второй выход анализатора 3 KK) вырабатывается сигнал "1", который через элемент ИЛИ-Н Е 5 поступает в виде О" на выход. При появлении ошибки д чередовании инвертируемых КК на выходах блока 14 памяти (первый выход анализатора 3 КК) вырабатываются сигналы "0" и

"1" ("1" и 0") соответственно, сигнал "1" ("0") поступает на первый вход элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 17. но при этом на втором его входе будет установлен сигнал

"1" ("0") с выхода триггера 15. По двум одинаковым логическим сигналам на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ l7 на его выходе формируется сигнал "0". Вместе с тем и на выходе элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ-НЕ 16 при передаче инвертируемь.х

КК по логическим сигналам нэ входах "0" и

"1" ("1" и "О") вырабатывается сигнал "О". В результате на выходе элемента ИЛИ-НЕ 18 формируется сигнал "1", который через элемент ИЛИ-НЕ 5 поступает на выход, что соответствует появлению ошибки в принимаемой информации, Если ошибки отсутствуют, то счетчик 21 блока 8 управления находится в исходном состоянии (на всех его выходах уровень "О"), а импульсы на С-вход не поступают благодаря запрету на элементе ИЛИ-НЕ 22 сигналом с выхода элемента ИЛИ-НЕ 5. При этом блок 8 управления не влияет на работу делителя 19 распределителя 6 циклов, который делит тактовую частоту на девять, а сам счетчик 21 блока 8 управления установлен в режим прямого счета, так как на его входах имеются соответственно уровни "1" и "0" с выходов элементов ИЛИ-НЕ/ИЛИ 24 и

ИЛИ-НЕ 25, На выходе счетчика 21 имеется уровень "О", Отрицательные импульсы ошибок разрешают прохождение импульсов частоты распределителя 6 циклов, снимаемых с инвертора 2С через элемент ИЛИ-НЕ 22 на

С-вход счетчика 21 (фиг, 4б) с некоторой задержкой т1, определяемой быстродействием интегральных микросхем, относительно импульса делителя 19 (фиг, 4а). После прихода восьмой ошибки (N = 8) счетчик 21 переходит в состояние "1" по выходу 03, при этом соответственно на первых входах

40 элементов ИЛИ-НЕ/ИЛИ 24 ИЛИ-НЕ 25 с некоторой задержкой tz относительно импульса ошибки (фиг. 4в) установится отрицательный потенциал (фиг, 4г), который разрешает прохождение отрицательных импульсов ошибок на выходе элемента ИЛИНЕ/ИЛИ 24 (фиг. 4д,е), Но эти импульсы не изменят ни работу счетчика 21, ни работу делителя 19, так как приходят с некоторой задержкой как относительно импульсов делителя 19 (фиг, 4а), так и относительно импульса нэ С-входе счетчика 21 (фиг, 4б).

Девятая ошибка в виде отрицательного импульса поступает на S-вход триггера формирователя 7 сдвига фазы (фиг, 4е) с неинверсного выхода элемента ИЛИ- Н Е/ИЛИ 24 и устанавливает на его выходе 0 положительный потенциал по фронту импульса блока 1 разделения сигналов, Этот потенциал поступает на вход DR делителя 19 расп ределителя 6 циклов и по следующему положительному фронту тактовой частоты дополнительная единица запишется на выход Q7 делителя 19, поэтому состояние "1" сохранится на выходе 00 делителя 19 не восемь, а девять тактов, что приведет к сдвигу цикловой синхронизации íà оды такl.

Одновременно приход девятой ош бки переводит счетчик 21 в режим пэраглельного приема, так как на его входах устанавливаются уровни "О". Поступающий на вход С счетчика 21 импульс переводит его в исходное состояние, одновременно в исходное состояние возвращается и формирователь

7, Сдвиг цикловой синхронизации будет продолжаться до вхождения системы в синхронизм, который произойдет максимум за

8 сдвигов (при восьмиразрядном входном слове).

Формула изобретения

Устройство цикловой синхронизации блочных кодов, содержащее последовательно соединенные блок разде .ния сигналов, дешифратор и анализатор:..;овых комбинаций, при этом выход сигнала тактовой частоты блока разделения сигналов подключен к тактовому входу дешифратора непосредственно и через распределитель циклов — к входу записи дешифратора и к управляющему входу блока управления, о тл и ч а ю щ е е с я тем, что, с целью уменьшения времени вхождения в синхронизм, введены блок определения нарушения чередования инвертируемых кодовых комбинаций (ИКК), элемент ИЛИ-НЕ и формирователь сдвига фазы, при этом выход распределителя циклов соединен с управля1688434 ющими входами анализатора кодовых комбинаций и блока определения нарушений чередования ИКК, выход которого и выход анализатора кодовых комбинаций через элемент ИЛИ-НЕ соединены с входом сигнала ошибки блока управления, выход которого и выход сигнала тактовой частоты блока разделения сигналов через формирователь сдвига фазы соединены с управляющим входом распределителя циклов, дополнительный выход которого соединен с входом сброса формирователя сдвига фазы, 5 причем выходы анализатора кодовых комбинаций соединены с соответствующими входами блока определения нарушения чередования ИКК, 1688434

1688434

Составитель В.Евдокимова

Техред М.Моргентал Корректор О.Кравцова

Редактор Э.Слиган

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

Заказ 3718 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 4/5