Устройство для контроля канала связи

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - повышение точности контроля путем выявления отдельных ошибок в реальном масштабе времени. Устройство содержит на передаче: датчик 1 испытательного текста, формирователь 2 повторяемых номеров, блок 3 управления циклами, формирователь 4 обратного чтения , на крышке, формирователь 5 повторяемых номеров, блок 6 сравнения, блок 7 регистрации, блок 8 сравнения номеров, датчик 9 контрольного текста, генератор 10 импульсов, анализатор 11, блок 12 управления циклами,формирователь 13 обратного чтения, преобразователь 14 кода, блок 15 памяти, формирователь 16 адреса, преобразователь 17 и таймер 18 Устройство позволяет выделить из суммарного потока в реальном масштабе времени отдельных событий типа вставленные и пропущенные комбинации, номера сопровождающих их испытательных и контрольных комбинаций и время их появления.1 ил. Пр1.ем со С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДЛРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Пр .ем (61) 1592953 (21) 4733509/09 (22) 29.08.89 (46) 30.10.91,Бюл ¹ 40 (71) Киевское отделение Центрального научно-исследовательского института связи (72) В.И.Шевчук, С.П.Зражевский, Н.П.Соловей, В,П.Пацук и Н.А,Соколова (53) 621.394.664(088.8) (56) Авторское свидетельство СССР №

1592953, кл. Н 04 L 12/26, Н 04 В 3/46, 1988. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАНАЛА СВЯЗИ (57) Изобретение относится к электросвязи.

Цель изобретения — повышение точности контроля путем выявления отдельных ошибок в реальном масштабе времени. Устройство содержит на передаче: датчик 1

„„SU ÄÄ 1688436 А2 (я) Н 04 (12/26 // Н 04 В 3/46 испытательного текста, формирователь 2 повторяемых номеров, блок 3 управления циклами, формирователь 4 обратного чтения, на крышке: формирователь 5 повторяемых номеров, блок 6 сравнения блок 7 регистрации, блок 8 сравнения номеров, датчик 9 контрольного текста, генератор

10 импульсов, анализатор 11, блок 12 управления циклами, формирователь 13 обратного чтения, преобразователь 14 кода, блок 15 памяти, формирователь 16 адреса, преобразователь 17 и таймер 18. Устройство позволяет выделить из суммарного потока в реальном масштабе времени отдельных событий типа вставленные и пропущенные комбинации, номера сопровождающих их испытательных и контрольных комбинаций и время их появления. 1 ил.

1688436

Изобретение относится к электросвязи и может быть использовано для оценки качества каналов передачи данных с высокими показателями надежности передачи информации при широком диапазоне длин информационных комбинаций и является дополнительным изобретением по авт.св.N.

1592953.

Цель изобретения — повышение точности контроля путем выявления ошибок в реальном масштабе времени.

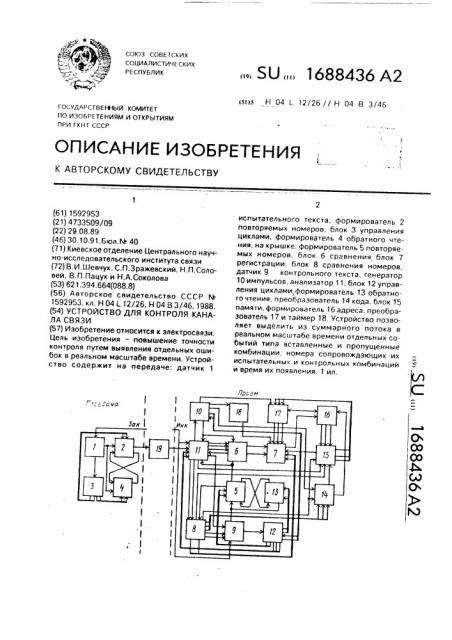

На чертеже представлена структурная электрическая схема устройства для контроля канала связи.

Устройство содержит на передаче: датчик 1 испытательного текста, формирователь 2 повторяемых номеров, блок 3 управления циклами, формирователь 4 обратного чтения; на приеме; формирователь

5 повторяемых номеров, блок 6 сравнения, блок 7 регистрации, блок 8 сравнения номеров, датчик 9 контрольного текста, генератор 10 импульсов, анализатор 11, блок 12 управления циклами, формирователь 13 обратного чтения, преобразователь,4 кода, блок 15 памяти, формирователь 16 адреса, преобразователь 17 и таймер 18. На чертеже показан также контролируемый канал 19 связи.

Устройство работает следующим образом.

Датчик испытательного текста формирует последовательность M-разрядных иклических номеров 1,2,3...,2 — 1,2 в м двоичной системе счисления, которая под управлением блока 3 управления циклами записывается в формирователь 2 повторяемых номеров и формирователь 4 обратного чтения, замкнутых по цепи обратной связи, и выдается на вход контролируемого канала связи.

На приеме датчик 9 контрольного текста, формирователь 5 повторяемых номеров контрольного текста, формирователь 13 обратного чтения и блок 12 управления циклами работают аналогично идентичным блокам на передаче (блокам 1,2,3 и 4 соответственно). При этом в качестве управляющего сигнала на входы анализатора 11 и датчика 9 иэ канала связи поступает сигнал

"Импул ьс наличия комбинации" (И Н К).

На блок б одновременно с испытательной комбинацией иэ анализатора 11 поступает контрольная комбинация иэ формирователя 5, Результат несравнения накапливается и, кроме того, в виде сигнала несравнения поступает на дешифратор анализатора 11, После подсчета 2 импульсов сигнала м от начала приема испытательной комбина55

50 ции и формирования и выдачи контрольной комбинации в анализаторе 11 и в блоке 8 сравнения номеров производят запись первых М разрядов (номер прямого чтения) соответственно в буфер анализатора 11 и в буфер блока 8 сравнения номеров. С этого момента с выходов указанных буферов анализатора 11 и блока 8 сравнения номеров постоянно выдаются М-разрядные сигналы соответственно "Номер испытательной комбинации" (НИК) и "Номер контрольной комбинации" (НКК), которые поступают на соответствующие входы блока 15. Перезапись новых (последующих) номеров испытательной и контрольной комбинаций пооизводят в новом цикле после приема 2 разряда следующей испытательной комбинации.

С момента включения питания с выхода генератор" 10 импульсов на вход преобразователя 14 кода и преобразователя 17 поступают непрерывные последовательности импульсов в виде сигнала "Тактовая частота" (ТЧ), которые поддерживают распределитель преобразователя 14 кода и счетчики преобразователя 17 в исходном положении, когда на их выходах сигналы отсутствуют.

В случае выявления на приеме вставленной или пропущенной комбинации производят обычную выдачу сигнала о количестве вставленных или пропущенных комбинаций блоком 8 сравнения номеров на блок 7 регистрации для получения усредненных показателей качества канала.

Кроме обычного выявления и регистрации сигналов о вставленных и пропущенных комбинациях из выхода сумматора блока 8 сравнения номеров на вход преобразователя 14 кода выдают в обратном коде СМ-1— разрядный сигнал "Сигнал разницы номеров" (CPH), а с M-го разряда сумматора укаэанного блока выдают на объединенные входы преобразователя 14 кода и блока 15 сигнал о знаке разницы номеров "Знак разницы номеров" (3PH). После окончания установления сигналов CPH и 3РН с выхода блока 8 сравнения номеров на вход преобразователя 14 кода выдают сигнал о наличии вставленной или пропущенной комбинаций "Импульс вставленной комбинации или импульс пропущенной комбинации" (ИВ К Ч ИПК).

Если разница номеров положительная, то в цепи сигнала ЗРН устанавливают положительный потенциал, который обеспечивает формирование M-1 — разрядного двоичного кода единицы (истинное число вставленных 6noKDB) на выходе преобразователя 14 кода (сигнал СРН) независимо от состояния сигнала СРН на входе указанного преобразователя. Затем сигнал ИВК V

1688436

ИПК злдерживлют тактами сигнала ТЧ в распределителе по--Образовэтеля 14 кода и выдают (01осле второй ступени 3:3с;.ря.KI1) на вход фОрмиоoнл3егя 16 э«реса с: н "Де сигнала Зл 1ись числа" (Зп -I)

По сигналу,,.1Ч счетчиKî 1 адреcОн 3,3 пиги фор лирон".ТС,», 16 адреса усглнлн" 1вают М-рлзрядны адрес и нида с11 нэлл

"Адрес" (Ад).

Кроме этого. по г.игнэлу 3 Ч н, ор" 1ировлтеле 16 адреса формируют;3 г,-.л.; Бьlборки режима" (БР) и "3; в1.:ь: ОЗУ" (ЗпОЗУ), которые сонмест «,:игнэлоië Ад выдают нэ входы блока 1. .

По управляющим си,1зл;=. м Б Р 13п ОЗУ информацию, содер.к,: „y ося н сигналах

НИК, НКK и ЗPН, :3пfсынлю; н т: ячейки

ОЗУ блока 15, адг»Рс которь,х содержигся в сигнале Ад.

Если разница номеров отр.1цл::..:ьнля, то в цепи с;- нала ЗРН, которы.. л::к т из блока 8 с лннения номеров, уста;:-"- л iнэют отрица »ьный потенциал, к01»ры 1 с: rfMc3 ют I3pf удительную у тэнон1у д;.о. Ii ого кода Р:.иницы Но выходю прспбрл..,вл3гля

14 кодл (сигнал СРН) M -1 — рлзрядныи с 1гнэл C! H, когорый выдают из 6f30I 1 8 cp3I3нения номеров н обратно1л кпд, преобрлзу1от инверсией fi fip 060 330 : ле

14 кодл в прямой код и по с. — у" Ь " .1:| К злписывлк т н счетчик . рю01брлзоi !-;: в кода. При этом е ли нэ нхпдю fipi;

ТЮЛЯ 14 Кода OTC 3!TCT f;r703 СИГIIЛЛ ВЗ -:С 3 Е ния коррекции" Р;„Кр), <0 fnjH;. .,- ., " и.. блока 8 сравнения номеров, то чист p: ri1 цы номеров, записанное н прсобрhç..,,. юле

1 4 КОДЛ вЂ” ИСТИН НОС. 1: СЛИ НЭ il ri "ОД:; 1., ., 1Л тора блока 8 сформирован сигнал 1. р-, н,»сэ, тО ЧИСЛО, ЗаПИСаННОЕ Н СЧЕТЧИК ПРЕО" РЛЗОвателя 14 кода -- ложное. Для преобразования его в истинное число нл -.,д преобразователя 14 кода из блока 8 ;рлгнюния номеров выдают разрешак3щий ".. и 1лл

PI!I Кр, по ко горОMó сигналfl ИР КУИ7 lK K<адюржанный после первой ступени з»держк1 распределителем, произноди3 преобразование ложного числа н истинною методом вычитания единицы. Затем с нь1ходл преобразователя 14 кода нэ гход блок-3 15 ныдл<» сигнал СРН, содержащий инф073 л-Зци о пб истинном числе пропущенн, х I r.,»16; нэц;";..

Режим работы формирователя 6 адреса и блока 15 по записи информации " п730пу щЕННЫХ КОМбИНацИяХ Н ОЗУ НЕ 03лялЧЭЮ3 я оТ режима работы укаэанных блоков пс 3;3писи информации 0 вставленных комбинац x ° O3V.

После включения питания и исг1раюности блока 7 регистрации с его выхода на вход счетчика адресов тения Фор -иронэт ".— ля 1! 6 адрюг л i flj)t piII3HO поступл10т и 1 г1ульсь игнл: - 3 f от . нности гэлокэ 7 регистрации н виде сиг11лла Готовность" (Г3). Если при эком на нхгд сч -тчикл адресов записи

5 сигнала ЗпЧ 1е по тупают, то содержимое обоих счетчиков сонпадэРТ и вход счетчика адресов чтения блокируют, Поэтому импульсы с:л нэлл 7, как в сче чиках адресов чтения, тлк и на выход формирователя 16

10 адресов не -or:туплют.

При поступлении импульсов сигнала

ЗпЧ на вход счетчика адресов записи его содержимое из,"1еняется и становится отличным от содержимого счетчика чтения, а

15 это приводит к разблокированию входа счетчика адре-.он чтения, при этом импульс сигнала Г, пос: упэет с выхода формирователя 16 адреса на вход блока 15 в виде

;.игнллэ БР и, кроме того, н виде сигнала

20 "Ч1ение с ОЗУ р(т ОЗУ) с выхода формиронэгеля 76 л,,реr:.-1 пас3уг1эют на вход преобрэзонэ3 —:л 1!, I также поступает на вход

" гГ Т ИК:3 Лдi): r.ое Ч1ЕНИЯ, ИЗМЕНЯЯ РГО СО д:j!ж11;1:!0:;,I Inrf.цн, «ТО приводит к раг-.г;HcT 3 лдр "i,он Обоих:четчи кон. При этОм

i3 код-. -и на.1л д ус3анлнливлют адрес чтения . I.1PIIHO r! .". информации, которая была н н. го злпислнл по предшествующему имг, льсу сп нлл.- ":3Ч

3.. j1,", ..! 1: к гцему сигналу Чт ОЗУ и гр01ьli .... Мпульсам сигнала ТЧ информ:-вн1", р ю читают из блока 15 в ни.,". сi1f H - " -". 1 1 разрядного НИК, Мрлэрядногг Hi.К .1 М-1 разрядного СРН, по35 ступлпT ..-р .., ."1р 30бразонатель 17 на входы блока 7 ог.f:.Ii.òp, Iè.1 н виде соответствующ .;,. »,Юл I1r f.yffьсон сигналов "Импульс номера испыTërnëüной комбинации" (ИНИК)..Л 1пул,с номера контрольной ком40 6 1r«,,1 " fi. -:;-., и "И;1пульс разницы номерсг; (ИР71!. Kp;Irле этого на вход блока 7

73егисT,)эции гз блока 15 ныдакэт сигнал 3Hак" ..Оложи-.ельный потенциал которого указывает нл то, что информация, содержа45 щллся:::::игнэл= l1РН. гредстлвляет число вставлен if I >, комбинаций, а отрицательный потен17иал уклзынэРт на ТО, что информэ ция, содержащаяся н сигнале VlPH, представляет чис 30 пропущенных комбинаций, Все

50 пере,ислю ныю сигналы регистрируются блоком 7 рюг,1стр; ции совместно с метками

Нр 3МЕни, Поет;ПЭЮщИМИ ИЗ таймвра 18, работающего:-о непрерывному тактовому сигнат:, . .-с уп- юшюму от генератора 10

Г;" !

5 икл11 д! -00,3.

Таким образом, отдельно возникающие н контролируемом канале 19 связи вставленн. Р и f000 øåHHLIC комбинации. номера с. »ронпждаю цих их испытательных и

КОНт;»СЛ:.-НЫ КОМб«НацИй рЕГИСтрИру1ОтСя В

1688436 реальном времени отдельно и независимо

or других событий.

Составитель В.Камалягин

Техред М.Моргентал

Корректор М.Максимишинец

Редактор 3.Слиган

Заказ 3719 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Формула изобретения

Устроиство для контроля канала связи по эвт.св.N. 1592953, о т л и ч а ю щ е е с я тем, что, с целью повышения точности контроля путем выявления ошибок в реальном масштабе времени. введены на приеме таймер, вход которо о соединен с третьим выходом генератора импульсов, а выход меток времени подключен к пятому входу блока регистрации и последовательно соединенные преобразователь кода, формирователь адреса, блок памяти и преобразователь, выходы которо о подключены к соответствующим шестым входам блока регистрации, выход которого подключен к входу сигнала конца регистрации формирователя адреса, второй выход которого подключен к второму входу преобразователя. вход тактовой частоты которого соединен с четвертым выходом генератора импульсов, пятый выход которого подключен к первому входу преобразователя кода, второй вход, вход пропущенной комбинации, вход разрешения коррекции и вход сигнала разницы номеров соединены соответственно с пятым, шестым, седьмым и восьмым выходами блока сравнения номеров, девятый выход кото10 рого подключен к входу номера контрольной комбинации блока питания, второй, третий входы и вход номера испытательной комбинации которого соединены соответственно с вторым выходом преобра15 зователя кода, с пятым выходом блока сравнения номеров и с четвертым выходом анализатора, а выход подключен к седьмому входу блока регистрации, пятые входы анализатора и датчика контрольного текста

20 объединены и являются входом наличия комбинации приема.