Устройство синхронизации несущей

Иллюстрации

Показать всеРеферат

COI03 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (yi)g Н 04 1 27/22

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4619101/09 (22) 13.12.88 (46) 30.10.91.Бюл.N. 40 (71) Одесский электротехнический институт связи им.А,С,Попова (72) А.М.Мельник, В.В.Шишкин и П.В,Иващенко (53) 621.396.662(088.8) (56) Патент США М 4546322, кл. 329/50, 8.10.85. (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ НЕСУЩЕЙ (57) Устройство относится к связи и может использоваться в демодуляторах систем данных сигналами фазовой и амплитуднофазовой модуляции при произвольной степени кратности модуляции. Цель

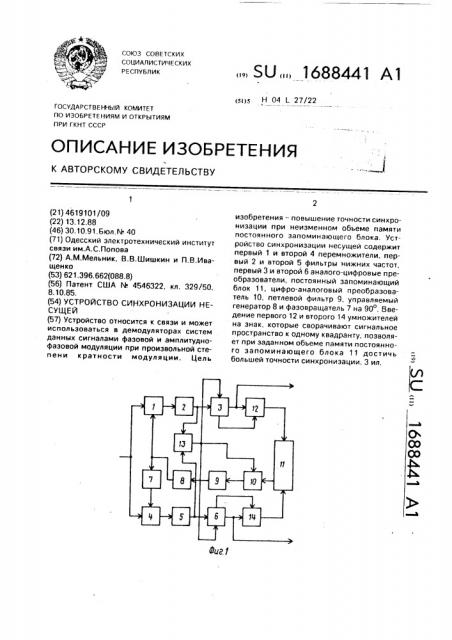

„„SU„„1688441 А1 изобретения — повышение точности синхронизации при неизменном объеме памяти постоянного запоминающего блока. Устройство синхронизации несущей содержит первый 1 и второй 4 перемножители, первый 2 и второй 5 фильтры нижних частот, первый 3 и второй 6 аналого-цифровые преобразователи, постоянный запоминающий блок 11, цифро-аналоговый преобразователь 10, петлевой фильтр 9, управляемый генератор 8 и фаэовращатель 7 на 900. Введение первого 12 и второго 14 умножителей на знак, которые сворачивают сигнальное пространство к одному квадранту, позволяет при заданном обьеме памяти постоянного запоминающего блока 11 достичь большей точности синхронизации. 3 ил, 16)18 j11

15

25

35

Усl с)с)й)с<(1() oTII()(;l11<:÷ v с))».)и l1 мс)жет испс)ль:)овэ<ьсч в де<лодулчгорэх систем Ileрсдачи данных c(1<налэMи флaoaс)и и амплитудно-фазовой модуляции при прс)извольнои стег)ени кратности модуля) iÈL1.

lIenB изобретения - повышение точности синхронизации при неизменном обьеме памяти постоянно<о запоминэк)щего блока (ИЗБ).

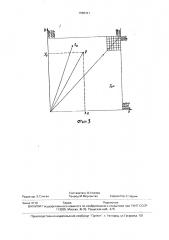

На фиг. 1 представлена структурная электрическая схема устройства синхронизации несу)цеи; на фи<.2 ансамбль сигналов с се<кои квантования, на примере которого почснче)ся работа устройства; на фи<.3 метод св<.ртки сигнала, позволяю(ции достичь цели изобретения.

Устройство синхронизации несущей содер.кит

ЧаСтО). ВтОрОй аНаЛОГО-цИфг()ВОИ ПрЕОбразовэт(ль 6, фазовращатель 7 на 90", управлчемь<й генератор 8, петлевои фильтр 9, Ilè<1)ðo энэлоговь)и преобразователь 10, ПЗ Г 11, первый умножитель 12 на знак, блок

13 Ta).TOB<))4 синхронизации и второи умно жит ел), 1 1 )la знак

Ус)рс)йство рабс)тает следующим обраЗС))Л

Входной сигнал (фазовой или квадра)урн<)и,)мплитудн<)й модуляции с произв()ль))ым <ислом позиций М) поступает одновременно нэ входbl первого 1 и второго

1 пе )ем ножи)елей, TIa BTopblP, входы КоТос)ь<х со сдви<ом фазы на 90, обеспечивае«лым фазоврэщэт<.пР<4 7, подаетсч опорное хо,)< Г)ание с подстрэиваемого сенератора 8.

Г1родегектированные сигналы выделяются первым 2 и вторым 5 фильтрами, в которых

ПОДаВЛЧ)ОГСч BЫ(OKO IàCтОтНЬIÅ ПРОДУКТЫ иерем)1оженич и квантуюгся в первом 3 и втором 6 аналого цифровых преобразователях, например на 64 уровня, Иэ шестиразрядного двоичного числа на выходах аналого-цифровых преобразователей 3 и 6 сэмыи старшии разряд поступает соответcTRpííî H< один вход первого 12 и второго

14 умножителеи на знак oooTBeTOTBPIITIo, оставшиеся пять разрядов — на другои их вход.

Умножение на знак производится следующим образом: если старший бит 0", остэвLLIèåcTI пять бит и н верт ируlo TñTI; если старший бит 1". то оставшиеся пять бит передаются без изл1ененич. Поступаюсцие с выходов умножите<)е(1 1? и 14 на знак ПЗБ

11 два двоичных пя тирэзрядных числа являются адресами ячеек ПЗБ 11 в которых записаны в двоичной форме соответствующие э<им числил значения фазовой ошибки. Далее двоичное число с выхода ПЗ Б 11 поступает на вход цифро-аналогового преобразователя

10, где формируется аналоговый сигнал фазовой ошибки, который после фильтрации петлевым фильтром 9 управляет частотой и фазой подстраиваемого генератора 8. Блок 13 тактовой синхронизации формирует сигналы, управляющей работой первого 3 и второго 6 аналого-цифровых преобразователей, также цифроэ налогового и реоб разо вателя 10. Формирование сигнала фаэовой ошибки производится следующим образом. Проекции сигнала на две ортогональные оси X и У, вычисляемые в синфазном и квадратурном подканалах аналого-цифровом преобразователями 3 и 6, квантуется на 64 уровня. Таким образом сигнальное пространство разбивается по осям X и У, как показано на фиг.2, на 64 зоны с номерами OT 0 (000000) до "63" (111111) образуя на плоскости 64x64=4096 ячеек.

Принимаемый сигнал попадает в одну из этих ячеек, Для заданного ансамбля сигналов известно расположение сигнальных точек в сигнальном пространстве, Например, в ансамбле ФМ-8 восемь сигналов равномерно размещены на окружности радиусом, равным средней энергии сигнала (сигналы

Sn-S> на фиг.2). Пусть S4 (фиг.2) одна из сигнальных точек ансамбля. Если в сигнальном пространстве в отсутствии помех принимаемый сигнал 2 не совпадает ни с одной сигнальной точкой ансамбля, то это означает, что между несущей сигнала и опорным колебанием, генерируемым подстраиваемым генератором 8, существует рассогласование по фазе, Например, если принятый сигнал Z принадлежит сигнальной области S4, то фаэовое рассогласование (фазовая ошибка) равно р (фиг,2,3) и его можно вычислить через координаты сигнала, как

Уу у) = alctg — агс19

Xs4 Xz где Yz Xz — координаты принятого сигнала;

Ys4, Xs4 — для заданного ансамбля сигналов априорно известные координаты сигналов ансамбля.

При известном виде сигнала для ансамбля из 4096 ячеек сигнального пространства, используя алгоритм (1), можно

Btl <ислить в пределах каждой сигнальной области значение р и записать его в ПЗБ 11 под адресом, задаваемым номером ячейки.

Затем по координатам принятого сигнала. представляемым в двоичной форме на выходах аналого-цифровых преобразователей 3 и 6 из Г1ЗБ 11, считывается значение фаэовой ошибки р, которое используется в дальнейшем для подстройки частоты и фазы

168844 1

40 опорного кол»баI l1я Д»истRè» нlgг10л л сп стеме, вызывающее флуктуации значения

< около его среднего значения, усредняется петлевым фильтром 9. Для ансамблей сигналов, проекции которых в квадрантах I, II. 5

lll, IY отличаются только знаком, к которым относятся ансамбли сигналов с фазовой и квадратурной амплитудной модуляцией, для вычисления фазовой ошибки достаточно использовать информацию только об аб- 10 солютном значении проекции принимаемого сигнала, т.е. необходим ПЗБ только для одного квадранта сигнального пространства. Путем умножения на старший разряд двоичного числа на выходе ана- 15 лого-цифровых преобразователей 3 и 6 в умножителях 12 и 14 на знак сигнальное пространство, приведенное на фиг,2, сворачивается к сигнальному пространству, показанному на фиг.3. При этом, например. для 20 ансамбля сигналов ФМ-8, приведенного на фиг,2, в результате свертки, с сигналом So будут совпадать сигналы Яз, Sp и S;, а с сигналом S1 — S;>,S.Sr,. В результате такого построения системы достигается, во-пер- 25 вых, в режиме вхождения в синхронизм соответствие знака расстройки частоты изменению величины фазовой ошибки, записанной в ПЗБ 11, во-вторых, уменьшение в 4 раза объема памяти ПЗБ 11. Если же 30 зафиксировать обьем памяти ПЗБ 11, то результатом свертки сигнала является повышение точности синхронизации.

Формула изобретения 35

Устройство синхронизации несущей, содержащее соединенные последовательнп « »го«нный запоминающии блок, петле вой фильтр, управляемый генератор, фазовращатель на 90, первый перемножитель. первыи фильтр нижних частот и первый аналого-цифровой преобразователь. соединенные последовательно второй перемножитель, второй фильтр нижних частот и второй аналого-цифровой преобразователь, а также блок тактовой синхронизации, причем первый вход второго перемножителя соединен с выходом управляемого генератора, вторые входы первого и второго перемножителей являются входом устройства, первый и второй входы блока тактовой синхронизации соединены соответственно с выходами первого и второго фильтров нижних частот, а его выход присоединен к входам запуска первого и второго аналого-цифровых преобразователей, отл и ч а ю щ ее с я тем, что, с целью повышения точности синхронизации при неизменном объеме памяти постоянного запоминающего блока, в него введены первый и второй умножители на знак, выходы которых соединены с адресными входами постоянного запоминающего блока, первые входы первого и второго умножителей на знак соединены соответственно с выходами старшего разряда первого и второго аналого-цифровых преобразователей, а вторые их входы — с выходами остальных разрядов соответствующих аналого-цифровых преобразователей, а также цифро-аналоговый преобразователь, при этом постоянный запоминающий блок подключен к петлевому фильтру через цифро-аналоговый преобразователь, вход запуска которого соединен с выходом блока тактовой синхронизации.

1688441

Составитель В.Козлов

Техред М.Моргентал Корректор С.Черни

Редактор Э.Слиган

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

Заказ 3719 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5