Устройство коррекции видеосигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к телевизионной технике. Цель изобретения - повышение быстродействия. Устройство содержит счетчик 1 адреса, первый и второй блоки 2 и 3 памяти, регистр 4 адреса, ЦАП 5. АЦП 6, блок 7 фотоэлектронного преобразователя и блок 8 развертки и фиксации уровня В начальный момент работы устройства осуществляется режим записи информации от белого поля в блок 3, при этом создается таблица коэффициентов коррекции для каждого значения видеосигнала от белого поля, после чего устройство переводится в режим считывания текущей информации с осуществлением коррекции считываемого видеосигнала на выходе АЦП 6 по определенному закону, определяемому содержимым блока 2. 2 ил

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

«»

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4704936/09 (22) 14.06.89 (46) 30.10:91.Бюл.М 40 (72) И.С.Горсюков, В.Н,Бессмертный и

В. М, Найштут (53) 621.397.6(088.8) (56) Патент ФРГ М 2714777, кл. Н 04 N

3/14, 1982. (54) УСТРОЙСТВО КОРРЕКЦИИ ВИДЕОСИГНАЛА (57) Изобретение относится к телевизионной технике. Цель изобретения — повышение быстродействия. Устройство содержит счетчик 1 адреса, первый и второй блоки 2 и

Изобретение относится к области телевизионной техники и может быть использовано при передаче фототелеграфных изображений для преобразования в цифровую форму сигналов фотоэлектронного преобразователя (ФЭП) изображения.

Цель изобретения — повышение быстродействия.

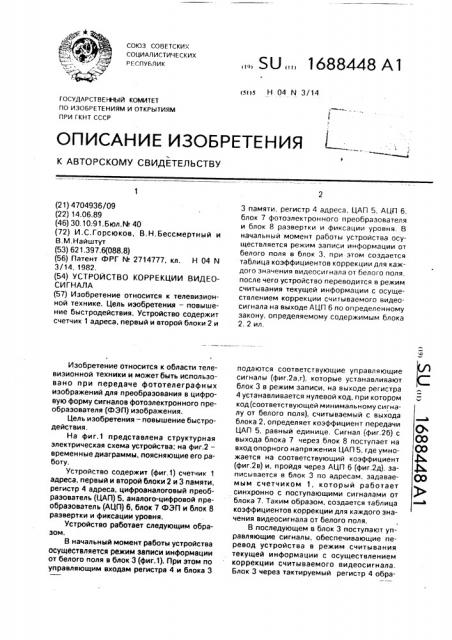

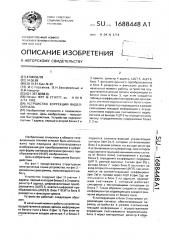

На фиг.1 представлена структурная электрическая схема устройства; на фиг.2— временные диаграммы, поясняющие его работу.

Устройство содержит (фиг.1) счетчик 1 адреса, первый и второй блоки 2 и 3 памяти, регистр 4 адреса, цифроаналоговый преобразователь (ЦАП) 5, аналого-цифровой преобразователь (АЦП) 6, блок 7 ФЭП и блок 8 развертки и фиксации уровня.

Устройство работает следующим образом.

В начальный момент работы устройства осуществляется режим записи информации от белого поля в блок 3 (фиг.1). При этом по управляющим входам регистра 4 и блока 3

„„SU „„1688448 А1

s Н 04 N 3/14

3 памяти, регистр 4 адреса, ЦАП 5, АЦП б, блок 7 фотоэлектронного преобразователя и блок 8 развертки и фиксации уровня. В начальный момент работы устройства осуществляется режим записи информации от белого поля в блок 3, при этом создается таблица коэффициентов коррекции для каждого значения видеосигнала от белого поля, после чего устройство переводится в режим считывания текущей информации с осуществлением коррекции считываемого видеосигнала на выходе АЦП 6 по определенному закону, определяемому содержимым блока

2. 2 ил. подаются соответствующие управляющие сигналы (фиг.2а,г), которые устанавливают блок 3 в режим записи, на выходе регистра

4 устанавливается нулевой код, при котором код(соответствующей минимальному сигналу от белого поля), считываемый с выхода блока 2, определяет коэффициент передачи

ЦАП 5, равный единице. Сигнал (фиг.2б) с выхода блока 7 через блок 8 поступает на вход опорного напряжения ЦАП 5, где умножается на соответствующий коэффициент (фиг,2в) и, пройдя через АЦП б (фиг,2д), записывается в блок 3 по адресам. задаваемым счетчиком 1, который работает синхронно с поступающими сигналами от блока 7. Таким образом, создается таблица коэффициентов коррекции для каждого значения видеосигнала от белого поля.

В последующем в блок 3 поступают управляющие сигналы, обеспечивающие перевод устройства в режим считывания текущей информации с осуществлением коррекции считываемого видеосигнала.

Блок 3 через тактируемый регистр 4 обра16ОЛ11Ц щаегся к адресному полю памяти блока 2 синхронно с поступающим видеосигналом от блока 7. При этом на выходе АЦП 6 осуществляетг,я кпррек1 ия считываемого видеосигнала по определенному закону. 5 определяемому содержимым блока 2, Формула изобретения

Устройство коррекции видеосигнала, содержащее аналого-цифровой преобразователь (АЦП), первый блок памяти, а также 10 последовательно соединенные блок фотоэлектронного преобразователя и блок развертки и фиксации уровня, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия, введены последовательно соеди- 15 ненные счетчик адреса, второй блок памяти и регистр адреса, а также цифроаналоговый преобразователь (ЦАП), сигнальный вход которого соединен с выходом первого блока памяти, адресный вход которого соединен с выходом регистра адреса. выход блока развертки и фиксации уровня соединен с входом ollOpHolo напряжения ЦАП, выход которого соединен с сигнальным входом

АЦП, выход которого является выходом устройства, на вход опорного напряжения АЦП подано фиксированное напряжение, при этом выход АЦП соединен с вторым входом второго блока памяти, управляющие входы регистра адреса и второго блока памяти являются входами сигналов управления "Запись-считывание", счетный вход счетчика адреса является входом тактовых импульсов.

Составитель В.Землянухина

Техред М.Моргентал Корректор М.Максимишинец

Редактор Н.Коляда

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 3719 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5