Сумматор последовательного действия

Иллюстрации

Показать всеРеферат

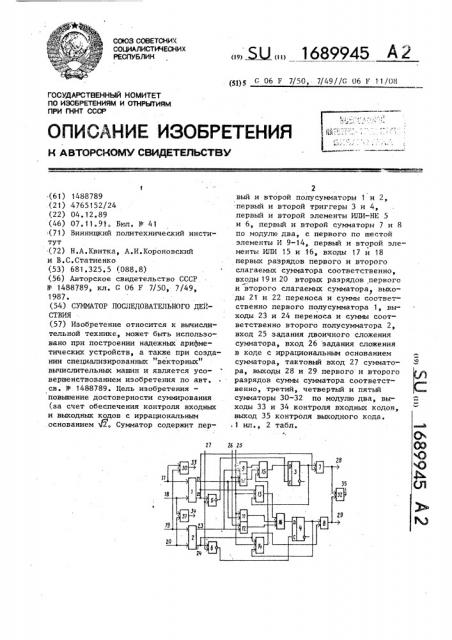

Изобретение относится к вычислительной технике, может быть использовано при построении надежных арифметических устройств, а также при создании специализированных векторных вычислительных машин и является усовершенствованием изобретения по авт. св. № 1488789. Цель изобретения - повышение достоверности суммирования (за счет обеспечения контроля входных и выходных кодов с иррациональным основанием vZ0 Сумматор содержит первый и второй полусумматоры 1 и 2, первый и второй триггеры 3 и 4, первый и второй элементы ИЛИ-НЕ 5 и 6, первый и второй сумматоры 7 и 8 по модулю два, с первого по шестой элементы И 9-14, первый и второй элементы ИЛИ 15 и 16, входы 17 и 18 первых разрядов первого и второго слагаемых сумматора соответственно, входы 19 и 20 вторых разрядов первого и второго слагаемых сумматора выходы 21 и 22 переноса и суммы соответственно первого полусумматора 1, выходы 23 и 24 переноса и суммы соответственно второго полусумматора 2, вход 25 задания двоичного сложения сумматора, вход 26 задания сложения в коде с иррациональным основанием сумматора, тактовый вход 27 сумматора , выходы 28 и 29 первого и второго разрядов суммы сумматора соответственно , третий, четвертый и пятый сумматоры 30-32 по модулю два, выходы 33 и 34 контроля входных кодов, выход 35 контроля выходного кода. .1 ил., 2 табл. а

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИ(АНИЕ ИЗОБРЕТЕНИЯ

Н A BTGPCHGMV СВИДЕТЕЛЬСТВУ

27 26 25

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

-(61) 1488789 (21) 4765152/24 (22) 04.12.89 (46) 07.11.91. Бюл. № 41

:(71) Винницкий политехнический институт (72) Н.А.Квитка, А.И.Короновский и В.С.Статиенко (53) 681.325.5 (088.8) (56) Авторское свидетельство СССР № 1488789, кл. G 06 F 7/50, 7/49, 1987. (54) СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ (57) Изобретение относится к вычислительной технике, может быть использовано при построении надежных арифметических устройств, а также при создании специализированных 1Фвекторных" вычислительных машин и является усовершенствованием изобретения по авт. св. № 1488789. Цель изобретения— повышение достоверности суммирования (за счет обеспечения контроля входных и выходных коров с иррациональным .основанием 2. Сумматор содержит пер Ы » 1б89945 А2 (51)S С 06 F 7/50, 7/49//С 06 F 11/08

2 вый и второй полусумматоры 1 и 2, первый и второй триггеры 3 и 4, первый и второй элементы ИЛИ-НЕ 5 и 6, первый и второй сумматоры 7 и 8 по модулю два, с первого по шестой элементы И 9-14, первый и второй элементы ИЛИ 15 и 16, входы 17 и 18 первых разрядов первого и второго слагаемых сумматора соответственно, входы 19и 20 вторых разрядов первого и второго слагаемых сумматора выходы 21 и 22 переноса и суммы соответственно первого полусумматора 1, выходы 23 и 24 переноса и суммы соответственно второго полусумматора 2, вход 25 задания двоичного сложения сумматора, вход 26 задания сложения в коде с иррациональным основанием сумматора, тактовый вход 27 сумматора, выходы 28 и 29 первого и второго разрядов суммы сумматора соответственно, третий, четвертый и пятый сумматоры 30-32 по модулю два, выходы 33 и 34 контроля входных кодов, выход 35 контроля выходного кода. .1 ил., 2 табл. м

1689945

Изобретение относится к вычислительной технике, может быть использовано прк построении надежных ариАметических устройств, а также при создании специализированных "векторных" вычислительных машин и является усовершенствованием известного сумматора последовательного действия IIQ авт. св. И"- 1488789. 10

Цель изобретения — повышение дос- товерности суммирования за счет обеспечения контроля входных и выходных кодов с иррациональным основанием (2.

На чертеже представлена схема сум- 15 матора последовательного действия.

Сумматор содержит первый 1 и второй 2 полусумматори, первый 3 и второй 4 триггеры, первый 5 и второй 6 элементы ИЛИ-НЕ, первык 7 и второй 8 20 суьяатсры по модулю два, элементы

И 9-14, первый 15 и второй 16 элемен:--. ты ИЛИ., входы первых разрядов первого

17 к в îðîãî f8 слагаемых сумматора„ входы вторых разрядов первого 19 и 2 второго 20 слагаемых сумматора выхо = ды переноса 21 и cyma r 22 первого гслусумматора 1, выходы переноса 23 к суммы 24 второго полусумматора 2, вход 25 задания двоичного сложения сумматора,, вход 26 задания сложения в коде с иррациональным основанием сумматора,, тактовый вход 27 сумматора,, выходы первого 28 и второго 29 разрядов суммы сумматора, третий 30, четвертый 31 и пятый 32 сумматоры па модулю два, выходы 33 и 4 контро:=ля входных кодов. выход 35 контроля выходного кода.

Первые входы первого 1 и второго 2 полусумматоров соединены. " "входами

17 к 19 параллельного приема двух .младших разрядов первого операнда„ а вторые входы — с входами 18 и 20 параллельного приема двух младших разрядов второго операнда, выход 22 суммы полусумматора 1 соединен с пер=вым входом первого сумматора 7 по модулю два, вторым входом пятого элемента И 13 и вторим входом первого,0

У У элемента ИЛИ-НЕ 5, выход которого поступает на вход разрешения приема первого триггера 3, ьыход суммы 24 полусумматора 2 соединен с первым входом второго сумматора 8 по модулю два, вторым входом шестого элемента

И 14 и вторым входом второго элемента

IdII1-НЕ 6„. выход которого поступает на вход разрешения приема второго триггера 4, первые входы пефь- о 5 к второго 6 элементов ИЛИ-"!1K ïîTrêëþчаются к тактовому входу 27 сумматора, выходы элементов И 9,10 и 14 подключены через первый элемент ИЛИ

15 к кн ьормационнаму входу первого триггера 3, выход которого поступает на второй вход первого сумматора 7 по модулю два, чей выход соединен с выходом 28 сумматора, а выходы элементов И 11-13 через второй элемент ИЛИ 16 подключень; к информацион- ному входу второго триггера 4, выход которого поступает на второй вход второго < умматора 8 по модулю два, чей выход соединен с выходом 29 сумматора, первые входы элементов 9,11, 13 и 14 подключены к входу 20 задания двоичногс сложения сумматора, вторые входы элементов 9, 11, 13 и 14 подклю= чены соответственно к выходу 23 переноса второго полусумматора 2 и второму входу четвертого элемента

И 12, к выходу ?1 переноса первого полусумма. тора 1 к второму входу второго элемента И 10,, третьи входы пятсгс 13 и шестогс 14 элементов подключены соответственно к выходам первого 3 к второго 4 триггеров, первые входы второго 10 к четвертога

12 элементов И вЂ” к входу 26 задания сложения в коде с иррациональным основа -:кем„

1 роме того, первые и вторые входы третьего 30 и четвертого 31 сумматоров па модулю два подсоединены соответственна к входам 17 и 19 первых к вторых разрядов первого слагаемого сумматора и входам 18 и 20 первых и вторых разрядов второго слагаемого сумматора, а первый и второй входы пятого сумматора 32 по модулю два соединены с выходами 28 к 29 первого к второго разрядов суммь сумматсра соответственно.

В системе счисления с основанием

"I

2 слагаемые числа А и В кзабражаютc;-, следуюшим образом;

-ьа (2) +ао(2) +а<(12) +а,,Я2) +

В=Ьд;,(.ф) +Ьд. (ъ2) 4 ...+Ь1("Г2) +bo(12) +Ь (2) +Ь (1/Г) -6 ... +

"Ь „(gI2) .. (2)

Веса разрядов кода с основанием

Я саставпяют последовательность

::тепеней основания

1489945 ь

В = (2+I) » Ь; 2

5

1 ...16 2,16,8 f2,8,4 2ь4,2 ф,2, (- 1(2 1 2 1 1 2 1 (2 2 4 4 8 8

Из выражения (3) следует, что чет- ные степени являются весами разрядов двоичного кода, а нечетные — весами двоичного кода, умноженными на 012.

С учетом этого выражения (1) и (2) можно записать

10 п-4, п-ß

i/а

А =I(2 l а 2 + a;2 (4)

Ч ., 1

4=222 и-й !

В 12 2Ь12 +1 Ь;2, (Ь) ,1=-в»

1- -Ф где а,а„,Ь;,Ъ„Ь j0,1) и являются цифрами двоично-кодированной системы счисления с основанием 2, à i, j

20 для n+m разрядних чисел принимают значения

j<(+1, та+3, .3 1 1 3 5 п-1 ;

iE (-ю,m+2, .;4,-2,0;2,4,: .. n-22 .

Первые члены формул (4) и (5) составляют суммы печатных разрядов кода, а вторые члены — суммы четных разрядов кода с основанием 2. Несмотря на то, что члены выражений 30 (4) и (5) объединены общим основанием, они независимы одно от другого, а это позволяет осуществить одновременную независимую параллельную техническую реализацию операции сложе- 35 ния четных и нечетных разрядов операндов, представленных в кодах с основанием 12, и таким образом увеличить быстродействие сумматора. В основу работы сумматора последова- 40 тельного действия положено сложение двух младших (первого и второго) одноименных разрядов в двоичной системе счисления с иррациональным основанием 2, которое выполняется сог- 45 ласно табл.1 и 2.

Если в качестве разрешенных кодовых комбинаций в двоично-кодированной системе:счисления с основанием f2 .для кодирования чисел использовать лишь те, которые содержат четное количество единиц, при этом единицы в разрешенной кодовой комбинации расположены парами, то слагаемые (4) и (5) при имают вид

-4

А = ((2+1) а„ 2; (6)

1. в- Й

1=-

Предлагаемое кодирование позволяет довольно просто осуществить контроль на нечетность как входных кодов, так и производить текущий контроль выполнения операции суммирования.

Признаком искажения кодовой комбинации является нечетность единиц в паре разрядов комбинации. Код позволяет обнаружить все однократные ошибки.

Сумматор может работать в двух режимах: в режиме сложения операндов, п едставленных в коде с основанием

2, и в режиме суммирования при двоичном представлении операндов. Первий режим обеспечивается подачей единичного сигнала на вход 26 режима работы, а второй — подачей единичного сигнала на вход 25 режима работы.

Последовательный сумматор в режиме сложения чисел в коде с иррациональным основанием 2 работает следующим образом.

Триггеры 3 и 4 перед началом работы устанавливаются в состояние "0".

В каждом такте суммирования на входы

17 и 19 сумматора подаются два разряда (начиная с мпадшего и следующего за младшим) первого операнда, а на входы 18 и 20 — соответствующие разряды второго операнда, причем на входы 17 и .19 сумматора поступают одноименные разряды четних весов с иррациональным основанием 2, а на входы 18 и ?0 — одноименные разряды нечетных весов кода с иррациональным основанием +2. При этом достоверной информацией, присутствующеи на входах

17, 19 и 18, 20, является информация

11, 00, 00, 11,. 11, 11, 00, 00. В случае, если на входах 17, 19 или/и l8, 20 присутствуют комбинации 10, 01, 01; 01, 10; 10, Ul ° 10, то на ю выходах 33 и/или 34 сумматоров 30 и/или 31 по модулю два возникают единичные потенциалы, сигнализирующие о прекращении операции сложения. Так -и образом, осуществляется контроль входных кодов.

Сложение одноименных достоверных разрядов происходит одновременно и для четных разрядов осуществляется по табл.1, а для нечетных — но табл.2. На вход 26 выбора режима работы поступает единичный сигнал.

Параллельно с выхода 21 переноса поФ

1689945 лусумматора 1 через элементы И 10 и ИЦИ 15 и с выхода 23 переноса полу сумматора 2 через элементы И 12 и

KIN 16 поступают соответственно на информационный вход триггера 3 сигнал переноса в следующий разряд четного

:веса кода, на информационный вход триггера 4 сигнал переноса в следуюцртй разряд нечетного веса кода. Ксли на входы сумматора поданы одинаковые значения разрядов слагаемых <00 или

11), то сигнап на выходе суммы полусумматоров 1 и 2 разрешит прохождение, тактового импульса соответственно через элемент ИХИ-НК 5 на тактовый вход триггера 3, который осуществит запись значения переноса в триггер 3, и через элемент ИЛИ-НК 6 на тактовый вход триггера 4. который осуществит запись значения переноса в триггер 4.

Если значения разрядов слагаемых различны, то триггеры 3 и 4 сохраняют предыд ущие состояния. На вьгсоды 28 и 29 сумматора поступает сумма по модулю два, значение поразрядной суммы и переноса, полученного в предыдущем разряде. Ксли и+в число разрядов кодов слагаемых, то -в,последнем и+ш ЗО (--- + 1). такте работы сумматора на

Его информационные входы поступают нулевые коды, а на выходе сумматора— сигналы, соответствующие состоянию триггера. Кспи сумматор,. при сложении 35 работает без сбоев, то при любом такте на выходах 28 и 29 первого и

Второго разрядов суммы сумматора

Всегда должны присутствовать сигналы, 11 или ОО.

40 . Появление на выходах 28 и 29 сигналов 01 или .10 свидетельствует о нарушении работы сумматора. Такое состояние подтверждается наличием единичного сигнала на выходе 35 сум- матора 32 по модулю два. Дальнейшее

Сужярование прекращается. В этом состоит контроль выходных кодов при ложении операндов, представленных в коде с основанием 2.

Особенности работы сумматора в режиме суммирования при двоичном представлении операндов в .следующем .

Режим обеспечивается подачей единич. ного сигнала на вход 25. Два одноразрядных сумматора объединены в схему параллельного двоичного двухразрядно,о сумматора с последовательным пере.=носом в отличие от режима сложения операндов, представленных с. основанием (2, где два одноразрядных сумм,"гара объединялись в схему параллельного двоичного двухразрядного сумматора с параллельным переносом. а

Запоминанием переноса с выхода 21 при сложении младшего из двух разрядов, поступающих на соответствующие входы 17 и 18 первого полусумматора

1, осуществляется не на триггере 3, входящем в первый одноразрядный сумматор, как в режиме сложения операндов„ представленных в коде с основанием Г2, а на триггере 4 второго одноразрядного сумматора, и запоминание переноса с выхода 23 при сложении старшего из двух разрядов, поступающих на соответствующие входы 19 и 20 вто-. рого полусумматора 2, осуществляется на триггере 3 первого одноразрядного сумматора.

Значение одноразрядной суммы в каждом такте снимается поочередно с выходов сумматора, во всех нечетных тактах работы первом, третьим и т.д. т..д.) — с выхода 28, во всех четных тактах работы †. с выхода 29.

" р и м е р;.Реализация операции сложения при двоичном представлении операндов. Пусть

A=01101

3=0001 1

Ha ..рвом такте сложения на входах

19 и 20 отсутствует информация, на входы 17 и 18 поступают два единичных сигнала.- Так как первоначально триггеры 3 и 4 установлены в нулевые состояния, то значение одноразрядной суммы на выходе 28 нулевое, образованный в результате сложения перенос на выходе 21 поступает через элементы

И 11 и ИЛИ 16 на информационный вход триггера 4 и, поскольку на выходе 24 полусумматора 2 присутствует нулевой сигнал, разрешающий прохождение такто=-. вого импульса на синхровыход триггера

4, единица переноса записывается в триггер 4.

На втором такте сложения на входы

19 и 20 поступают соответственно

"О" и "1", на входах 17 и 18 информация отсутствует. Учитывая перенос, записанный в триггере 4, на выходе 29 получают нулевое значение суммы. На этом такте суммирования единичные сигналы с выхода триггера 4 и выхода

24 суммы полусумматора 2 совместно с единичным значением сигнала на вы=Ю

1о89945 раза меньше) то это позволяет повы— нт сить быстродействие сумматора н данном режиме почти в два раза.

Формула и з обретения

Т а б л и ц а 1

0

0 0

1 1

0 1

1 1 0 О.

Таблица2

0

1

0 0

1 1

0 1

1 1 0 0

50 ходе 25 поступают на входы э. емента

И 14, с выхода которого через элеме

ИЛИ 15 поступают на информационный вход триггера 3, и данным тактовым импульсом, поступающим на тактовый вход триггера 3, запоминаются в нем.

На третьем такте сложения на входах 19 и 20 информация отсутствует, на входы 17 и 18 подаются соответственно "1" и "0", значение суммы на выходе 22 полусумматора 1 — "1", 1! ft значение пер =:носа на выходе 21 — 0

Учитывая единицу, записанную на предыдущем такте работы в триггере 3, на входах первого 7 сумматора по модулю два присутствует две единицы, что обеспечивает голучение на выходе

28 нулевого значения суммы и запись

"1" через элемент И 13 и ИЛИ 1б в триггер 4.

На четвертом такте сложения на входах 19 и 20 присутствуют сигналы соответственно "0" и "1", на входах

17 и 18 информация отсутствует, значение суммы на выходе 21 — "0", на выходе 22 — 1", которая совместно с "1", записанной в триггере 4 на предыдущем такте,, поступает на вход сумматора 8 по модулю два и обеспечивает появление нулевого значения суммы на выходе 29, а также запись единицы аналогично процессу, указанному на предыдущем такте, в триггер 3.

На пятом такте сложения на входе

17 — "0", на входе 18 — "0", на входах 19 и 20 информация отсутствует, На выходе суммы 22 — "О", на выходе

21 — "0", на первый вход сумматора 7 по модулю два поступает с выхода триггера 3 единица, записанная на предыдущем такте суммирования, что ведет к формированию "1" на выходе 28.

В связи стем, что при сложении

n+m-разрядных двоичных чисел выпол.няется (n+m + 1)(п+1) суммирований, а при сложении

12 — — +1) суммирований т. е. в два

Сумматор последовательного действия по авт.св. и 1488789, о т л и— ч а ю шийся тем, что, с целью повышения достоверности суммирования, в него дополнительно введены третий, четвертый, пятый сумматоры по модулю два, причем первые входы третьего и четвертого сумматоров по модулю два подсоединены к входам первых разрядов первого и второго слагаемых сумматора соответственно, вторые входы третьего и четвертого сумматоров по модулю два соединены с входами

20 вторых разрядов первого и второго слагаемых сумматора соответственно, выходы первого и второго разрядов суммы сумматора подсоединены соответ,ственно к первому и второму входам пятого сумматора по модулю два, выходы третьего и четвертого сумматоров по модулю два являются выходами контроля входных кодов сумматора, а выход пятого сумматора по модулю два — вы30 ходом контроля выходного кода сумматора. ао Ьо П4(- 8Н а а1 П S