Устройство для вычитания по модулю

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и мсжет быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит первый и второй дешифраторы 3 и 6, первьй и второй элементы И 7 и 8, первый и второй элементы НЕ 9 и 10, элемент ИЛИ-НЕ 11, с первой по третью группы элементов ИЛИ 12, 13 и 18, коммутатор 14, с первой по тр-етью группы элементов И 15-17, шифратор 22 со связям. Сущность изобретения состоит в уменьшении каждого операнда в два раза и, после нахождения результата, увеличение его в два раза с изменением на единицу, в зависимости от соотношения четности обоих операндов, ввиду чего происходит уменьшение логических элементов, необходимых для реализации таблицы вычитания. 2 табл., 1 ил„ (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК ($))5 С Об Р 7/72

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРСИОМ,К СВИДЕТЕЛЬСТВУ (21) 4754342/24 (22) 31. 10. 89 (46) 07.11.91. Бюл. ¹ 41. (72) О.Н.Фоменко, В.А.Краснобаев, В.II.Èðõèí, A.À.Æóðaâëåâ, С.И.Куцый, С.В.Иванов и С.О.Гладченко . (53) 681.325.5 (088.8) (56) Авторское свидетельство СССР № 1107122, кл. G 06 I 7/72, 1983, Авторское свидетельство СССР

М - 1012242, кл. G 06 Р 7/49, 1981. (54) УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ ПО

Моа"лю (57) Изобретение относится к автоматике и вычислительной технике и мсжет быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов.

Цель изобретения — сокращение ап— паратурных затрат.

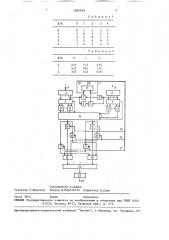

На чертеже представлена схема устройства для вычитания по модулю (для нечетного значения модуля).

Устройство содержит вход 1 умень-, шаемого, первый входной регистр -2, первый дешифратор 3, вход 4 вычитавмого, второй входной регистр 5, второй дешифратор 6, первый элемент И 7, второй .элемент И 8, первый элемент

„„SU„„1689949 А) 2 классов. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит первый и второй дешифраторы 3 и 6, первый и второй элементы И 7 и 8, первый и второй элементы НЕ 9 и 10, элемент ИЛИ-НЕ

11, с первой по третью группы элементов ИЛИ 12, 13 и 18, коммутатор 14; с первой по третью группы элементов

И 15-17, шифратор 22 со связями.

Сущность изобретения состоит в уменьшении каждого операнда в два раза и, после нахождения результата, увеличение его в два раза с изменением на единицу, в зависимости от соотношения четности обоих операндов, ввиду чего происходит уменьшение логических элементов, необходимых для реализации таблицы вычитания. 2 табл., 1 ил.

НЕ 9, второй элемент НЕ 10, элемент О

KIN-HE 11, первую группу элементов 00

ИЛИ t2, вторую группу элементов ИЛИ . К,)

13, коммутатор 14, первую группу эле- СО ментов И 15, вторую группу элементов ф

И 16, третью группу элементов И t7, сО третью группу элементов ИЛИ 18, вы ход 19 элемента ИЛИ-HF. 11, выход 20 первого элемента И 7, выход 21 второгс элемента И 8, шифратор 22, выходной ааюй регистр 23, выход 24 устройства.

Сущность изобретения состоит в следующем. Рассмотрим алгоритм определения результата операции (A-H)modm при различных соотношениях четности операндов А и В. Отметим также, что

1689949 вычисление любой функции остатка в уннтарном коде сводится к соответствующей перенумерации шин.

Пусть А и  — четные. Тогда

А В А-3

2"(- — -) = 2 --- = А †:В. 2 2 2

Если А нечетное, а В четное, то А-1 В, А-В 1

" (— — — -) = 2 (— — — -)=-(А-3)-1

2 2 2 2

При А четном,  — нечетном

А 31 АВ 1

2 (- — — — -) =-2 (-— -— - + -) =(А-В)+1., 2 2 2 2 ,А-1 1-".;

Если А и  — нечетные. то 2 (---- .—

3-1 4.-3 — — -) =2 — -=А-В

2 2

Следовательно, если учитывать характеристики четности операндов А и

В H их соотношения 9 появляется ВОэ можность уменьшить примерно в два раза нходные операндов, если в необхо=" димых случаях прибавить к полученному „..

2з результату или вычесть из него едиьпщу.

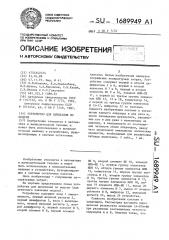

Рассмотрим в качестве примера табл. 1, отражающую операцию (А-В)

moa 5. . (1

Обозначим через А и В соответст-

А А 1 В 3 1 венно значения — — — и — ††. Тогда

2 2 2 2

А/3/ 0

А /В/ 1 0 0

0 1 2

Отметим, что у последнего значения отсутствует пара, т.к. m=5 (не- 10 четное число). Составим табл„2, в ко-. торой отобразим в клетке таблицы для операчдов А и 31 над чертой значение (А-В) mod 5, а под чертой 2(А-3)mod. 5, Сравнивая табл.1 и 2, замечаем, 15 что для огерандон А и В одинаковой четности последняя реализует табл.1, но для разной четности операндов А и В необходимо изменить результат на единицу. Табл.1 составлена для 50 пяти значений Операндов А и В, а табл.2 — только для трех значений, что позволяет существенно уменьшить самую громоздкую часть подобных табличных устройств.

Рассмотрим работу устройства (см. чертеж) н трех режимах. Первый режим соответствует случаю, когда операнды

А и В одновременно либо четные, либо нечетные. 3 этом случае о: е..ан,<ь. А и В поступают по соответстцующым в:о-= дам 1 и 4 во входные регнс ры 2 и 5 соответственно в двоичном коде„ Если числа четные, на выходах младших.. разрядов регистров 2 и 5 — пули, в противном случае — единицы, С выходов входных регистров 2 и 5 операнды поступают на входы соответственно первого

3 и второго 6 дешифраторов, выходы которых попарно соединены (четные с нечетными) и являются входами элементов ИЛИ 12 и 13 соответственно первой и второй групп„ Следовательно, сигналы, соответствующие первому и второму операндам, поступают соответ= стненно на один из и:.формационных и управляющих входов коммутатора l4„

Так как операнды А и В имеют одинако-. вый порядок четности, то на выходах первого и второго элементов И 7 и 8 сигналов нет. Поэтому с выхода 19 элемента ИПИ-HЕ 11 сигнал поступает на первые входы элементов И 15 первой группы, Сигнал с выхода, соответствующего унитарному коду результата опе.— рации модульного вычитания коммутато-ра 14, поступает на второй вход одно-го из открытых элементов И 15 первой группы,, с выхода которого оН поступает через соответстнующий элемент

ИПИ 18 третьей группы на вход шифратора 22, который преобразует результат операции в двоичный код. Далее результат операции по"ò-ó."ïàåò на вы- ., .одной регистр 24 и на выход устройства. Второй режим соответствует слу=-. чаю, когда А нечетное9 а В четное. В этом случае на выходе младшего разряда региатра 2 — единица, которая поступает на один вход элемента Ы 7 на другой вход которого сигнал посту-пает с элемента НЕ 10. Сигнал с выхо.да 20 первого элемента И 7 поступае" на вторые входы элементов И 16 второй группы. Операнды А и Б поступают -;o выхода коммутатора 14 аналогично пер-= вому режиму, но в данном случае сиг-: нал,соответствующий унитарному коду результата операции9 поступает на соответствующий открытый элемент И 16 второй группы и с его выхода — на соответстнующий элемент ИПИ 18 третьей группы. Соединение элементов

И 16 второй группы с элементами ИГИ

18 третьей группы обеспечивает прибавление единицы к унитарному коду результата операции. Дальнейшее про1689949

15

30

50 хождение сигналов соответствует IfBp» ному режиму.

Третий режим соответствует случаю, когда A — четное, а  — нечетное. В этом случае на выходе младшего разряда регистра 5 — единица. Сигнал поступает на первый вход второго элемента И 2, на второй вход которого поступает сигнал с первого элемента

НЕ 9. Сигнал с выхода 21 второго элемента И Я посгупает на вторые входы элементов И 17 третьей группы. Операнды А и В поступают до выхода коммутатора 14 аналогично первому режиму, нс н данном случае сигнал, соответст, вующий унитарному коду результата операции„ поступает на соответствующий открытый элемент И 17 третьей группы и с его выхода — на вход соответствующего элемента ИЛИ 18 третьей группы, Соединение элементов И 17 третьей группы с элементами ИЛИ 18 третьей группы обеспечивает вычитание единицы из унитарного кода результата операции. Дальнейшее прохождение сигналов соответствует первому режиму. формулаизобретения

Устройство для вычитания по модулю, содержащее первый и второй дешифраторы, первый и второй элементы И, элемент ИЛИ-НЕ, с первой по третью группы элементов ИЛИ, коммутатор; с первой по третью группы элементов

И, шиАратор, причем входы-разрядов входа уменьшаемого устройства соединены с входами соотнетствующих разрядов входа первого деытАратора, входы разрядов входа вычитаемого устройства соединены с входами соответствующих разрядов входа второго дешиАратора, выходы первого и второго элементов И соединены с соответствующими входами элемента ИЛИ-НЕ, выход которого соединен с первыми входами элементов И первой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ третьей группы, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, оно содержит первый и второй элементы НЕ, причем вход младшего разряда входа уменьшаемого устройства соединен с первым входом первого элемента И и входом первого элемента НЕ, вход младшего разряда входа вычитаемого устройства соединен с первым входом второго элемента И и входом второго элемента НЕ, выходы первого и второго элементов НЕ соединены соответственно с вторыми входами второго и первого элементов И, 2р-1-й и

2р-й выходы первого дешиАратора р= m/2, (m — значение модуля) соотнетстненно с первым и вторым входами p-ro элемента ИЛИ первой группы, 2р-1-й и 2р-й выходы второго дешиАратора — соответственно с первым и вторым входами р-го элемента ИЛИ второй группы, выходы элементов ИЛИ группы и m-й выход первого дешифратора при нечетном m — соответственно с информационными входами группы коммутатора, выходы элементов ИЛИ второй группы и m-й выход второго дешиАрато" ра при нечетном m соединены соответственно с управляющими входами группы коммутатора, выходы группы которого соединены с вторьпя входами соот-. ветствующих элементов И .первой группы с первыми входами соответствующих элементов И второй и третьей групп, выходы элементов ИЛИ третьей группы соединены с входами соответствующих разрядов входа информатора, выход которого является выходом устройства, выходы первого и второго элементов И соединены с вторыми входами элементов

И второй и третьей групп соответственно, выход k-ro (k=1 — m-1) элемента И второй группы соединен с вторым входом k+1-го элемента ИЛИ третьей группы, выход m-ro элемента второй группы соединен с вторым входом первого элемента ИПИ третьей группы, третий вход k-го элемента ИЛИ третьей группы соединен с выходом k+1-го элемента И третьей группы, третий вход и. ro элемента ИЛИ третьей группы соединен с выходом первого элемента И третьей группы.

1689949

Таблица1 г В/А

0 1 2 3 4

Таблица2

В/А

О/0 1/2 2/4

4/3 О/0 1/2

3/2 4/3 О/О

Составитель А.Клюев

Редактор Г.Федотов Техред И Иоргентал Корректор И.Пожо

Заказ 3814 Тираж Подписное

ВНИКЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,101

1 г

0

0 1

4 0

3 4 г 3

1 2

2 3 4

1 .2 3

0 1 2

4 0 1

3 4 0