Устройство для восстановления информации при сбоях в блоках цвм

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при разработке ЦВМ повышенной надежности. Изобретение решает задачу восстановления состояния основных регистров ЦВМ. предшествующего выполнению команды, в которой произошел сбой, с целью расширения области применения. Устройство содержит первый блок памяти, первый элемент И. шину данных и шину блокировки, блок синхронизации команды, регистр, счетчик, два мультиплексора, второй элемент И, элемент И-НЕ, второй блок памяти и блок микропрограммного управления с соответствующими связями. Работа устройства построена на принципе последовательного сохранения в ходе выполнения команды исходной информации и адресов тех регистров ЦВМ, исходное значение которых необходимо для правильного повторного выполнения команды с последующим восстановлением содержимого этих регистров ЦВМ & процедуре повторного выполнения команды. 1 з.п.ф-лы, 4 ил. Ј

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (ы)з G 06 F 11/22

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ. СВИДЕТЕЛЬСТВУ (21) 4651921/24 (22) 19.12.88 (46) 07.11.91. Бюл, Q 41 (72) В.Е.Зенин, Е,О.Поливода, А.У.Ярмухаметов, В.Б.Матвеев и О.И.Дапин (53) 681.3 (088,8) (56) Авторское свидетельство СССР

М 552608, кл. G 06 F 11/16, 1987.

Авторское свидетельство СССР

N. 1124314, кл. G.06 F 11/?2, 1984. (54) УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ ИНФОРМАЦИИ ПРИ СБОЯХ В БЛОКАХ ЦВМ .(57) Изобретение относится к вычислительной технике и может быть использовано при разработке ЦВМ повышенной надежности.

Изобретение решает задачу восстановления состояния основных регистров ЦВМ, Изобретение относится к вычислительной технике и может быть использсвано в

ЦВМ повышенной надежности.

Целью изобретения является расширение области применения за счет восстановления информации в блоках памяти.

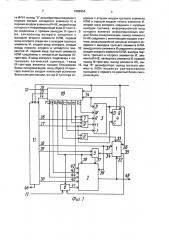

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока синхронизации; на фиг. 3 — циклограмма работы. блока синхронизации; на фиг. 4 — структурная схема второго блока памяти.

Устройство для восстановления информации при сбоях в блоках ЦВМ (фиг. 1) содержит первый 1 и второй 2 блоки памяти. счетчик 3, регистр 4, первый 5 и второй 6 мультиплексоры, первый 7 и второй 8 элементы И. элемент И-HE 9, блок 10синхрони„„. Ж„„1689954 А1 предшествующего выполнению команды, в которой произошел сбой, с целью расширения области применения..Устройство содержит первый блок памяти, первый элемент И, шину данных и шину блокировки, блок синхронизации команды, регистр. счетчик, два мультиплексора, второй элемент И, элемент

И-НЕ, второй блок памяти и блок микропрограммного управления с соответствующими связями. Работа устройства построена на принципе последовательного сохранения в ходе выполнения команды исходной информации и адресов тех регистров ЦВМ, исходное значение которых необходимо для правильного повторного выполнения команды с последующим восстановлением содержимого этих регистров

ЦВМ в процедуре повторного выполнения команды; 1 з,п.ф-лы, 4 ил. эации, блок 11 микропрограммного управления, шину 12 данных и шину 13 блокировки.

Блок 10 синхронизации (фиг. 2) имеет выходы с первого по десятый 14-23 соответственно и первый 24 и второй 25 входы. Блок

11 микропрограммного управления имеет выходы с первого по пятый соответственно

26-30.

Первый блок 1 памяти имеет первый 31 и второй 32 информационные входы, вход

33 разрешения записи, первый 34 и второй

35 выходы и адресный вход 36.

Второй блок 2 памяти имеет адресные входы записи 37 и чтения 38, вход 39 повторения, вход 40 разрешения записи, информационный вход 41, вход 42 записи в выходной регистр, вход 43 управления ре1689954

20 буется сохранять исходные данные в блоке

1 памяти, то на выходе 27 блока 11 микропрограммного управления единица. В этом 25 случае сигнал блокировки, поступающий на вход 25 блока 10 синхронизации, равен едижимом и вход 44 синхронизации при записи. На фиг. 1 показаны также выход 45 данных в блоки ЦВМ 45 и выход 46 микрокоманд в блоки ЦВМ.

Блок 10 синхронизации (фиг. 2) содержит генератор 47, сдвиговый регистр 48, дешифратор 49, счетчик 50, D-триггер 51, IK-триггер 52, элементы И 53-54 с первого по пятый соответственно, элементы ИЛИ

58-60 с первого по третий соответственно, элемент И-НЕ 61 и элемент НЕ 62, На фиг.

2 показана шина 63 единичного потенциала.

Второй блок 2 памяти (фиг, 4) содержит первый 64 и второй 65 мультиплексоры, адресуемую память 66, регистр 67, первый 68 и второй 69 элементы ИЛИ, элемент И-НЕ

70 и элемент НЕ 71.

Устройство работает следующим образом.

Рассмотрим работу устройства при безошибочном выполнении команды. Если тренице. Вследствие этого в первом полутакте на выходе 15 блока 10 вырабатывается сигнал сброса счетчика 3, а во втором полутакте на выходе 18 — сигнал записи в регистр 4.

Во втором полутакте формируется также сигнал записи в первый блок 1 памяти, поступающий на вход 33 разрешения записи.

В результате в регистр 4 переписывается нулевое значение из счетчика 3, а в первом блоке 1 памяти по нулевому адресу записываются содержимое (с входа 32) и адрес (с входа 31) регистра, хранящего адрес команды.

При считывании регистра ЦВМ, используемого для получения результата и одновременно изменяемого в ходе выполнения текущей команды, его адрес и исходное содержимое поступают соответственно на входы 31 и 32 первого блока 1 памяти. При .этом с выхода 16блока 10 выдается сигнал модификации, а с выхода 18 блока 10 — сигнал фиксации адреса и разрешения записи в первый блок 1 памяти. В результате (в первом полутакте) значение счетчика 3 увеличивается на единицу и(во втором полутакте) в регистр 4 записывается увеличенное значение счетчика 3, а в первом блоке 1 памяти по адресу, задаваемому счетчиком

3, записываются содержимое (с входа 32) и адрес (с входа 31) считанного регистра

ЦВМ. При этом сохранение содержимого регистра ЦВМ в первом блоке 1 памяти выполняется до того, как оно изменится при выполнении команды.

При выполнении такта, в котором нет необходимости сохранять исходные данные в блоке 1 памяти устройства, на выходе 27 блока 11 микропрограммного управления сигнал отсутствует, поэтому модификации счетчика 3 и записи в блок 1 памяти не происходит, а выполняется только запись в регистр 4 того же значения, которое было в нем ранее. Таким образом, во время выполнения команды блок 1 памяти заполняется адресами и исходными данными основных регистров ЦВМ, исходные значения которых необходимо использовать при повторном выполнении команды, При безошибочном выполнении команды устройство не влияет на вычислительный процесс.

Если в процессе работы ЦВМ обнаружена ошибка, то во втором полутакте текущего такта ЦВМ вырабатывается сигнал блокировки, поступающий на вход 25 блока 10 синхронизации, вследствие чего блокируются сигналы, поступающие на входы разрешения записи в блок 1 памяти и фиксации в регистр 4 новых адресов, Таким образом, в регистре 4 сохраняется адрес блока 1 памяти, по которому выполнена последняя запись во время безошибочного выполнения команды.

По сигналу неисправности ЦВМ устройство переходит к выполнению процедуры обработки сигнала неисправности. При этом сбрасывается регистр адреса блока 11 микропрограммного управления, а значение регистра 4 переписывается. в счетчики 3 и 50 (фиг, 2). На входе 33 блока .1 памяти устанавливается значение, соответствующее разрешению чтения из блока. Далее часть содержимого ячеек блока 1 памяти поступает с выхода 34 через мультиплексор

5 на адресный вход 37 записи второго блока

2 памяти (содержащего основные регистры

ЦВМ, выполненные в виде адресуемой памяти бб). а другая часть содержимого ячеек — через мультиплексор 6 на информационный вход 41 блока 2 памяти. Вход 37 используется для адресации восстанавливаемого регистра ЦВМ, а вход 41 — для занесения в выбранный регистр его исходного значения, сохраненного в олоке 1 памяти во время выполнения команды.

После восстановления регистра ЦВМ. выбранного по адресу., поступившему с выхода 34 блока 1 памяти первым, значения счетчиков 3 и 50 уменьшаются на единицу, после чего выполняется восстановление следующего основного регистра ЦВМ. Указанная процедура воостановления исходных данных основных регистров ЦВМ выполняется дотех пор, пока значение счет1689954

10

30

55 чика 50 не станет равным нулю. При этом произойдет восстановление исходных данных основного регистра ЦВМ, хранящего адрес выполняемой команды. Таким образом, во всех основных регистрах ЦВМ, исходные данные которых сохранены и возможно изменены на этапе безашибочного выполнения команды, происходит восстановление исходных данных. После этого триггер 52 блока 10 синхронизации и повторения команды изменяет состояние и осуществляется перевод ЦВМ на повторение неправильно выполненной команды.

Формула изобретения

1. Устройство для восстановления информации при сбоях в блоках ЦВМ, содержащее первый блок памяти, блок синхронизации, первый элемент И, причем вход начальной установки блока синхронизации является входом начальной установки устройства, вход блокировки блока синхронизации является входом блокировки устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области при ленения за счет восстановления информации в блоках памяти, в устройство введены блок микропрограммного управления, счетчик, регистр, второй блок памяти, два мультиплексора, второй элемент И, элемент И-НЕ, причем входы начальной установки регистра и блока микропрограммного управления подключены к входу начальной установки устройства, информационные входы блока синхронизации и счетчика соединены с выходом регистра, информационный вход которого и адресный вход первого блока памяти соединены с выходом счетчика, суммирующий вход которого соединен с выходом элемента И-НЕ, первый вход которого и первый вход второго элемента И соединены с выходом признака модификации блока микропрограммного управления, вход синхронизации которого соединен с первым выходом блока синхронизации, второй выход которого соединен с первым входом первого элемента И и синхровхадам чтения второго блока памяти, адресный вход чтения которого и первый информационный вход первого блока памяти соединены с выходом адреса чтения блока микропрограммного управления, выход адреса записи которого соединен с первым информационным входом первого мультиплексора, второй информационный вход которого соединен с первым информационным выходом первого блока памяти, второй информационный выход которого соединен с первым информационным входом второго мультиплексора, второй информационный вход которого является информационным входом устройства, третий выход блока синхронизации соединен с вторым входом элемента И вЂ” НЕ, выход первого элемента И соединен с входом сброса счетчика, вычитающий вход которого соединен с четвертым выходом блока синхронизации, пятый выход которого соединен с синхровходам регистра и с вторым входом второго элемента

_#_. выход которого соединен с входом управления записью чтения первого блока памяти, второй информационный вход которого соединен с информационным выходом второго блока памяти, вход повторения записи котарогэ, управляющие входы первого и второго мультиплексоров соединены с шестым выходом блока синхронизации, седьмой выход котарого соединен с входом управления режимом второго блока памяти, синхравхад которого соединен с восьмым выходом блока синхронизации, девятый выход которого соединен с входом управления записью счетчика и входам сброса адреса микракаманды блока микропрограммного управления, выход признака начала микрокоманды которого соединен с вторым входам первого элемента И, вход разрешения записи второго блока памяти соединен с выходом разрешения записи блока микропраграммнага управления, выход микрокоманды которого является выходом микракоманды устройства, информационный выход второго блока памяти является информационным выходом устройства, выход первого мультиплексора соединен с адресным входом записи второго блока памяти, информационный вход которого соединен с выходам второго мультиплексора.

2. Устройство пои. 1, о тл и ч а ю щеес я тем, что блок синхронизации содержит генератор импульсов, сдвиговый регистр, дешифратор, счетчик К-триггер, О-триггер, пять элементов И. элемент И-НЕ, три элемента ИЛИ, элемент НЕ, причем выход генератора импульсов соединен с синхровходам сдвигового регистра, информационный вход которого соединен с выходам первого элемента ИЛИ, первый вход которого соединен с выходом элемента НЕ, первый и второй входы дешифратора соединены соответственно с первым и вторым выходами сдвигаваго регистра, третий выход которого соединен с входом элемента

НЕ и третьим входом дешифратора, выходы

"0", "1" которого соединены с первыми входами соответственно первого и второго эле-. ментов И, первый вход третьего элемента И и синхравход 0-триггера соединены с выходом "3" дешифратора, выход "5" которого соединен с вторым входом первого элемен1689954 та ИЛИ, выход "6" дешифратора соединен с первым входом четвертого элемента И и первым входом элемента И-НЕ, второй вход которого и информационный вход 0-триггера соединены с прямым выходом IK-тригге- 5 ра, синхровход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом третьего элемента И, второй вход которого, вторые входы первого, второго и четвертого эле- 10 ментов И, первый вход третьего элемента

ИЛИ соединены с инверсным выходом IKтриггера, К-вход которого подключен к потенциалу логической единицы, I-вход

IK-триггера является входом блокировки 15 блока синхронизации, вход сброса IK-триггера является входом начальной установки блока синхронизации, выход D-триггера соединен с вторым входом третьего элемента

ИЛИ и первым входом пятого элемента И, второй вход которого соединен с нулевым выходом счетчика, информационный вход которого является информационным входом блока синхронизации, выход элемента

И-НЕ соединен с вычитающим входом счетчика, вход управления записью которого соединен с выходом третьего элемента ИЛИ, выход пятого элемента И соединен с вторым входом второго элемента ИЛИ, выходы первого, третьего и второго элементов И, элемента И-НЕ, четвертого элемента И, прямой выход IK-триггера, выход элемента НЕ, выход "6" дешифратора, выход третьего элемента ИЛИ являются соответственно выходами с первого по девятый блока синхронизации.

1689954

1689954

Редактор И.Шулла

Составитель H.Ïîñòîâîé

Техред M. Моргентал Корректор О. Кравцова

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 3815 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 415