Декодер кодов рида-соломона

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Использование его в системах передачи информации по каналам с 0-ичными сигналами позволяет повысить помехо22 liba-гч защищенность декодера, содержащего регистр 1 принятого кодового слова, регистр 2 выбранных кодовых символов, блок 3 преобразования кодов, регистр 4 надежностей кодовых символов, блок 5 определения индексов максимальных надежностей, регистр 6 выбранных индексов и регистр 10 декодированного слова. Благодаря введению регистра 7 выбранных надежностей, блока 8 поразрядного сравнения, ключа 9, регистра 11 копии, кодера 12 кода Рида-Соломона (п, к), компаратора 13, счетчика 14 нисла различий, блока 15 управления, кольцевого сдвигового регистра 16, блока 17 сравнения с единицей и элементов 18 и 19 развязки в декодере обеспечивается исправление одной или двух ошибок и n-k стираний . 1 з.п. ф-лы, 3 ил. (Л С Os о о ю о ю

СОЮЗ СОВЕ1СКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sa)s Х 03 M 13/02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Г.

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4395600/24 (22) 25.01.88 (46) 07.11.91, Бюл. М 41 (72) С.Л.Портной, С.И.Ковалев, А.Е.Тузков, А.Л.Дейч и С.Б.Жиронкин (53) 621.394.14;681.325 (088.8) (56) Авторское свидетельство СССР

3Ф 921106, кл. Н 03 M 13/02, 1980.

Авторское свидетельство СССР

N. 1401614, кл, Н 03 M 13/02, 1986.

Вопросы радиоэлектроники, Сер. ТПС, 1975 f4 11 с. 64-69. (54) ДЕКОДЕР КОДОВ РИДА-СОЛОМОНА (57) Изобретение относится к вычислительной технике. Использование его в системах передачи информации по каналам с Q-ичными сигналами позволяет повысить помехо„„SU „„1690202А1 защищенность декодера, содержащего регистр 1 принятого кодового слова, регистр 2 выбранных кодовых символов, блок 3 преобразования кодов, регистр 4 надежностей кодовых символов, блок 5 определения индексов максимальных надежностей, регистр 6 выбранных индексов и регистр 10 декодированного слова. Благодаря введению регистра 7 выбранных надежностей, блока 8 поразрядного сравнения, ключа 9, регистра 11 копии, кодера 12 кода Рида-Соломона (n, k), компаратора 13, счетчика 14 числа различий, блока 15 управления, кольцевого сдвигового регистра 16, блока 17 сравнения с единицей и элементов 18 и 19 развязки в декодере обеспечивается исправление одной или двух ошибок и и-k стираний. 1 з,п. ф-лы, 3 ил.

1690202

}Лзоб}ретение относится к ьычислительной технике и может быть!«cfIQJ!b30BBHG в сист6ма}1 116редачи информации ilo каналам с 0-ичными сигналами, а также B

ВнешнеГО декодера кас«здных кбдОВ.

Цель изобретения — повышение помаХОЗащищеННОСТИ ДЕКОДа}Ра.

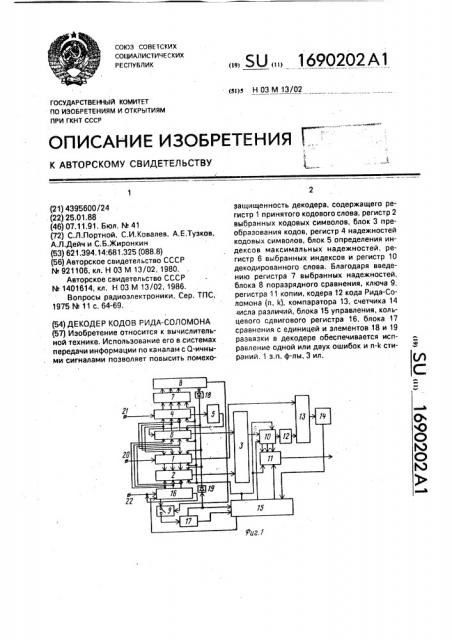

На фиг. 1 приведена функциональная схема декодер"; на фиг. 2 и 3 — Выполнение соответственно блока управления и блока п060бразования кодов.

Декодер кодов Рида-Соломона (РС) содержит р8Гистр 1 принятоГО КОДОВОГО слова, регистр 2 выбранных кодовых -имволов блок

3 преобразования кодов, регистр 4 наде>кн=:сти кодовых символе}В, блок 5 опредегlенил индексов максимальных надежностей, регистр 6 выбранных индексов, регистр 7 выбранных надежност й, блок 8 поразрядного сравнения, ключ 9, регистр 10декодированного слова, регистр 11 кс пии, кодер 12 кода

РС, компаратор 13., счетчик 14 числа различий, блок 15 управления, кольцевой сдвиговый регистр 16, бло«17 сравнения с единицей, первый N второй элементы 18 и

19 оазвязки, HB Фиг, 1 Обозначены первые и вторые информационные входы 20 и 21 и входы 22 констант, Цег1и тактирования и начальной ycTBHOBKv не показаны, Разрядность соединений обозначена возле косой чеОты, Г .ересекак)щей coo) Ветствующ}чо линию (фиг. 1), В основе работы декодера лежит следующиЙ BHQBb раЗ}}абстан IJN алто}эитм Оыст" рого декодирования кода РС (и, kji где Jl—

Длина кодового славB, k число информационных символов, Из <анаг1а связи HB входы

20 и 21 декодера пос) упа к)т O-,чsнHbыIе 6 ccNN}fir.воJib! I GPOBOf СЛОВВ И Ч-N.1ЧЫЕ а}НВЧ НИЧ HBдежности и ри ня 1 bI)! С им волов ко цов3 го слова. По величине надежности отбира}отся

1 + д н и()о,чюе н 1 f)c)у<н ы)1 символов принт

ТОГО КОДОВОГО CJIQBB. ЭТИМ СИМ ВОЛам С 3BBT

CB Э CQQTB8TCTBN8; 0" КИ ПОСЕК ГИЕ I!OIr; плоскости PG 2,C, ), где <1 + q +1 < < -+ О., д =- "1 + 1 следующИм Образом, апись прЯ" мой PG 12,q I представляет собой последовательность 0 и 1, cocT03щая N3 !: +

+ <) 3JI8M6HTQB fiPVI"l;M Нчг}ЕВЫМ =JIB ле}11.ам

СООТВ6ТСТВУВТ И Нфо РмаlЦИC H:.IЫ V Наб P.

ЦИКЛ и 1 ..С«и СДВ 1 Газ:1;>Т, Q OCJI 6 J,<)BBT8 JI Ьность !< + д ра3 относит-JtbHO списка сто бранных символов коДОВОГO сл})ва, П<)Л}слаеМ ПРОЕКТИРН C} ПЛОС}<ос Г, П ПЯМЦа. И

КОТОРОЙ ЯВЛЯЮТ-Л BC;:fj ЗОЗМОЖ;-:b!P К.-ъЛоа ЫЕ слова, Г}олучаемые п )и каждо«i сдниг8 посл довательнОсти пу пзм пp806pBÇOBBI NA из системы GcTBToчных к)1:."}сс01 - в обобщенН0-ГОЗиционную сi",OTBJJI}J и из ОбОб:ценно5

3 Фъ

<) 1 1

55 позиционной системы е Qоэиционную систему:r: последующего кодирования кодом

РС (и, k) oa3JIN«HbIx информационных наборов, поступа}ощих с выхода блока 3 преобразования кодов.

По определению проективной геометрии через гнобые две раэличнь}е точки проходит единственная ".,„}ямал. Укаэанное обстоятельство гарантирует исправление двух ошибок при переборе k + д прямых и исправление и-k стираний. Перебор д+1 прямой позволлет исправить одну ошибку.

Таким образом осуществляетсл полный или IBGTvl IHb}N f)8P650P, В зависимости GT состолнил канала связи, максимум за k+

+ д циклических сдвигов последовательности, позволяющий исправить одну или две

oUJNGKN и и-k стиранийl.

Блок 15 управ;}ения (фиг, 2) содержит формирсватель 23 импульса, первый элемент 24 задержки, регистр 25 числа различий, регистр 26 копии, компаратор 27, первый сумматор 28, перекг}ючатель 29, счетчик 30 циклов, дешифра:op 31, второй сумматор 32, втсрой элемент 33 задержки и элемент 34 ".à-çâÿçêè,,На фиг. 2 обозначеды первые, второй и третий входы 35-37 и перB bI N-H 6 T B ",т ь1 Й В и х 0 д ы 3 8-4 1 .

Блок 3 преобразования кодов служит для преобргзо;-.ания из системы остаточных

«лассов в f:.".!общенную позиционную систему, а из íсе — B позиционную систему. Блок

3 содержи-, (фиг.,3) блок 41 оперативной памяти, тактовь}й генератор 42, первый и второй арифметико-логические блоки (АЛ Б)

43 и 44 и блок 45 микрокомандного управления, выполненный на ПЗУ. Первый АЛБ 43 содержит "руппу региcTpoB 46, сумматоры

47 В I!OJ e GF(Q) и делит8ль 48 в пол8 GF(Q), Второй АЛБ 44 содержит гр" и регистров

49, умнох<итель 50 B поле GF(I) и сумматор

511 В поле GF(Q).

БЛОК 5 ОП 06J16JI BHN VriH tg6!

22 KGHOTà1т и записывается в КОльцевой сдвиговый регистр 16.

Жесткие значения символов кодового слова поступают на J16pBbf8 инфОрмационные входы 20 и записываются в регистр 1, Одновр8меннО значения надежности символов Г}ринятОГО кОдовоГО слоВа поступают HB

169020 :. . втОрые инфор! .1ацион!!ь а в,"!Оды 2 1 и записываю =я в регистр 4, с выхода которОГО значения надежност!i поступают в блОк 5, ГД8 Определяются инДексы k + д наибОлее надежных символов кодовоГО слОва.

Отобранные к + д инДексы пос-гупают и записываются в реГистр 6,,с разрядных выходов которого управля!Ощие сигналы поступают на соответствующие разрядные входы управления перезаписью регистров 1 и4,,npN 3TQ! с разрядных 8 !xQpoB регистра

4k + д значений надежности поступа!От на разрядные информационные входы регистра 7, с разрядных выходов которого выбранные значения надежности поступают на разрядные входи блока 8 порязрядного сравнения. Одновременно с разрядных выходов регистра 1 Выбраннь а символь. кодового слова поступаю. На разрядные информационные Входы регистра 2.

При невыполнении условия сравнения с выхода «Не равно" блока 8 на входы разрешения перезаписи регистров 1, 2 и 6 поступает сигнал управления, в результате происходит следующее (процедура М 1), С разрядных выходов регистра 16, содержащих нулевые эле:- 8!,ты последовательности, на разрядные Входы разрешения перезаписи в регистра", 2 и 6 поступают сигналы, при этом с последовательных выходов ре1-истров 2 и б разрешенные разряды поступают HB первь 8 В,оды (жестких эначе;!Ий) и вторые(инд .-,сн-.:8) зходы блока

3 преобразования кодов, одновременно с последовательных BL!õoqoí регистра 1 HR

Bxopb! компаратора 13 поступает кодовое слово, г! ринято8 иэ «анапа связи.

С Выходов блока 3 д8!:Одйрованный информационный набор поступает на входы регистра 10 декодирован ного слова, с выходов которого информационный набор поступает на Входы кодера 12 кода РС, с выходов которого кодовое слово поступает на другие входы компаратора 13, с выхода которого информация о посимвольном различии поступает на вход счетчика 14 числа различий.

С выхода счетчика 14 число различий поступает через первь!е входы 35 блока 15 управления на входы регистра 25 числа различий, и на первом цикле через разрядные входы поступает в регистр 26 копии, с последовательных выходов которых числа различий поступают на входи компаратора 27, с выходов которого сигнал " или "=" или g . поступает на входы сумматора 28. !(роме того, сигнал с выхода « » компаратора 27 поступает через вентиль 34 на вход разрешения считывания регистра 25 и непосред;.. :::;;,-! HQ через четвертый выход 4 ; блока 15 —:;::; вход разрешения считывания регистра !!. при этом через разрядные входы в ре. -;Стр 11 копии записывается декодирован5 лий ичформационный набор.

С выхода сумматора 28 через первый замкнутый контакт переключателя 29 сиг-! !ал поступает на вход счетчика 30 циклов.

Ыатем выполняется следующее (процедура

10 !i= ), С выходов счетчика 30 циклов сигнал пес-гупает на входы дешифратора 31 и через ,:i;Iü:матор 32 — на первый выход 38 блока 15 правления, соединенный с входом управ.15 ления сдвигом кольцевого регистра 16, при т-ом происходит циклический сдвиг послед Вательности, а с выхода старшего разряда дешифратора 31 сигнал поступает черЕз второй выход 39 блока 15 управления на

20 Вход разрешения считывания регистра 11 копии, с выхода которого на выход декодера поступает декодированное кодовое слово, а

-;-акже ", выхода старшего разряда дешифратора 31 сигнал поступает через элемент 33

25 задержки и третий выход 40 блока 15 управления на входы сброса всех регистров, кроме регистра t6.

При выполнении условия сравнения с выхода "Равно блок 8 на управляющий

30 ход кл!Оча 9 поступает сигнал, открывающн;": ключ 8. При этом содержимое первого разряда регистра 16 поступает на вход бло:.;а 17 сравнения с единицей, При Выполнении условия сравнения с

35 выхода «Равно« блока 17 сигнал поступает

-a входы разрешения перезаписи регистров 1, ", 6 и через второй вход 36 блока 15 управления на вход разрешения считывания регистра 25. Далее следует процедура

40 М1, При невыполнении условия сравнения с

Выхода «Не равно" блока 17 сигнал поступает через третий вход 37 блока 15 управления на вход формирователя 23 импульса, с вы45 хода которого импульс поступает на управляющий Вход переключателя 29, и через элемент 24 задержки через замкнутый второй контакт переключателя 29 импульс поступает на вход счетчика 30 циклов; Далее

50 следует процедура М 2.

При использовании кода РС (31, 15) в декодере обеспечивается энергетический выигрыш кодирования 1,5 дБ по сравнению с прототипом для случая, когда в канале с

55 ортогональными сигналами вероятность ошибки Рс = 10 — 10 на кодовое слово, Формула изобретения

1. Декодер кодов Рида-Соломона, содержащий регистр принятого кодового слова, информационные входы которого

1б)90202

20 являются первыми информационными входами декодера, а разрядные выходы соединены с соответствук) щими информационными входами регистра выбранных кодовых символов, выходы которого подключены к первым входам блока преобразоВания кодов, выходы которого соединены с информационными BKctäBM регистра декодированного слова, регистр надежностей кодовых символов информационные, входы

КОторого являются вторыми информационными входами декодера, а последовательные выходы соединены с входами блока определения индексов максимальных надежностей, Выходы KGTOpOl 0 подклк)чены к информационным входам регистра выбранных индексов, разрядные и последовательные выходы которого соединенысоответственно с разрядными входами управления перезаписью регистра принятого кодового слова "и вторыми входами блока преобразования КОДОВ, 0 т л и ч а ю щ и йс я тем, что, с целью повышения помехозащищенности декодера, в него введены кольцевой сдвиговый регистр, регистр выбранных надежностей, блок поразрядного сравнения, ключ, блок сравнения с единицей, элементы развязки, <одер кода РидаСоломона, компаратор счетчика числа различий, регистр копии и блок управления, первый выход которОГО с06динен с входом управления сдвигом кольцевого сдвигового регистра, информационные входы которого являются входами конста т декодера, а разрядные выходы подключены к разрядным входам управления перезаписью регистра выбранных кодовых символов и регистра выбранных индексов, последовательные выходы регистра принятого кодового слова и регистра декодированного слова подключены COOTBBTcтвенно непосредственно и через кодер кода Рида-Соломона к первым и

BTOpblM ВХОДам KOM)18pBTCpB, ВЫХОД КОТОр0го соединен с входом счетчика числа различий, выходы которого подкл)очены к первым входам блока управления, второй выход которого соединен с входам разрешения считывания регистра копии, разрядные входы управления перезаписью регистра надежностей кодовых символов подключены к соответствующим разрядным выходам регистра выбранных индексов, разрядные выходы регистра надежностей кодовых символов соединены с информационными выходами регистра выбранных надежностей, ВЫХОДЫ KOTOPO)0 ПОДКЛЮЧ8НЫ К COOTBBTCT вующим входам блока поразрядного сравнения, выходы "Не равно" и "Равно"

КОТОРОГО 008ДИН6НЫ СООТВ8ТСТВ8ННО С BXQдом первого элемента развязки и управляющим входом ключа, информационный вход которого подключен к выходу первого разряда кольцевого сдвигового регистра, выход ключа соединен с входом блока сравнения с единицей, выход "Равно" которого подключен к входу второго элемента развязки и второму Входу блока управления, третий ВыхОд котороГО с08динен с Входами обнуления регистра Выбранных надежностей, регистра надежностей кодовых символов, регистра выбранных индексов, регистра принятого кодового слова, регистра выбранных кодовых символов, регистра декодированного слова и пегистра копии, выходы элементов развязки объединены и подключены к входам разрешения перезаписи регистра выбранных индексов, регистра принятого кодового слова и регистра выбранных кодовых символов, выход "Не равно" блока сравнения с единицей соединен с третьим входом блока управления, четвертый выход которого подключен к входу разрешения считывания регистра декодированного слова, разрядные выходы которого соединены с информационными входами регистра копии, выход которого является выходом декодера.

2. Декодер по и. 1, о тл и ч а ю щи и ся тем, что блок управления содержит компаратор, сумматоры, переключатель, формирователь импульса, элементы задержки. счетчик циклов, дешифратор, элемент развязки, регистр копии и регистр числа различий, информационные входы которого являются первыми входами блока, а управляющий вход объединен с входом элемента развязки и является вторым Входом GlloKB, последовательные и разрядные выходы регистра числа различий соединены соответственно с первыми входами компаратора и входами регистра копии, выходы которого подключены к вторым входам компаратора, выходы "Больше" и "Равно" которогоаоединены с первым и вторым входами первого сумматора, выход которого подключен к первому информационному входу переключателя, вход формирователя импульса является третьим входом блока, выход формирователя импульса через первый элемент задержки и непосредственно соединен соответственно с вторым информационным и управляющим входами пераключателя, ВыхОд которОГО подключен к входу счетчика. циклов, выходы которого соединены с входами дешифратора, выходы разрядов кОторОГО, кООме старшеГО, под ключены к входам втОрОГО сумматора, ВыхОд которОГО ЯвлЯетсЯ первым ВыхОДОм блОка, выход старшего разряда дешифратора соединен " входом второго элемента задержки

1690202

Составитель Q.Ревинский

Техред М. Моргентал Корректор М.Демчик

Редактор О.Хрипта

Заказ 3827 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 и является вторым выходом блока, выход второго элемента задержки является третьим выходом блока, выход "Меньше" компаратора подключен к третьему входу первого сумматора, входу элемента развязки и является четвертым выходом блока,