Вычислительное устройство петлевой локальной сети

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для построения петлевых локальных вычислительных сетей. Целью изобретения является увеличение быстродействия за счет сокращения времени доступа через петлевой интерфейс . Поставленная цель достигается тем, что каждое вычислительное устройство локальной петлевой вычислительной сети содержит операционный блок 1, приемный сдвиговый регистр 2, передающий сдвиговый регистр 3, блок 4 управления, блок 5 сопряжения, мультиплексор 6, информационные и управляющие магистрали 7, блок 8 буферной памяти. 1 з.п. ф-лы, 3 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з G 06 F 15/16

ГосудАРственчый комитет

IlO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4638657/24 (22) 17.01.89 (46) 15.11,91. Бюл. ЛЬ 42 (71) Научно-исследовательский институт

"Квант" (72) А.С.Малахов, О.В.Медведев и Э.М.Сосин (53) 681.325(088.8) (56) Вейцман g. Распределенные системы мини- и микроЭВМ. M.: Финансы и статистика, 1983, с.69-70, рис.2,27.

Флинт Д. Локальные сети. Архитектура, принципы построения, реализация. М.: Финансы и статистика, 1986, с,164-.167, рис.14.1, 14,3. (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

ПЕТЛЕВОЙ ЛОКАЛЬНОЙ СЕТИ

„„53J 1бу184б А1 (57) Изобретение относится к вычислительной технике и может быть использовано для построения петлевых локальных вычислительных сетей. Целью изобретения является увеличение быстродействия за счет сокращения времени доступа через петлевой интерфейс. Поставленная цель достигается тем, что каждое вычислительное устройство локальной петлевой вычислительной сети содержит операционный блок 1, приемный сдвиговый регистр 2, передающий сдвиговый регистр 3, блок 4 управления. блок 5 сопряжения, мультиплексор 6, информационные и управляющие магистрали 7, блок 8 буферной памяти, 1 а.п. ф-лы, 3 ил.

1691846

Изобретение относится к вычислительной технике и может быть использовано для построения локальных петлевых вычислительных сетей.

Цель изобретения — увеличение быстродействия путем сокращения времени доступа через петлевой интерфейс.

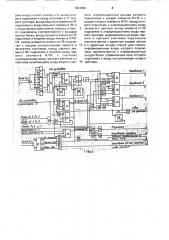

На фиг, 1 представлена ròруктурная схема петлевой локальной вычислительной сети; на фиг, 2 — схема блока управления; на

10 фиг. 3 — схема блока буферной памяти, Петлевая локальная вычи(:лительная сеть состоит из вычислительных устройств, каждое из которых содержит операционный блок 1, приемный сдвиговый регистр 2, передающий сдвиговый регистр

3, блок 4 управления, блок 5 сопряжения, мультиплексор 6, информационные и управляющие магистрали 7 и блок 8 буферной

20 памяти.

Блок управления образуют формирователь 9, дешифратор 10, элементы И 11-23, элементы ИЛИ 24.-34, элементы И-ИЛИ 35 и

36, счетчики 37 — 39 и триггеры, 40 — 46.

Блок буферной памяти включает элементы с первого по шестой элементы НЕ

47 — 52, первый элемент ИЛИ 53, седьмой элемент НЕ 54, элемент ИЛИ-НЕ 55, второй элемент ИЛИ 56, с первого по четвертый триггеры 57-60, первый и второй элементы

И 61 и 62, восьмой элемент НЕ 63, элемент

И-HE 64, первый, второй и третий счетчики

65-67 и узел 68 памяти, Петлевая локальная вычислительная сеть работает следующим образом запросное слово, Как только логика блока 4 управления обнаруживэет отсутствие транзитного сообщения на входе петлевого интерфейса вычислительного устройства, блок

5 сопряжения размыкает петлю и передающий регистр 3 подключается своим последо45 вательным выходом к выходу петлевого интерфейса. Данные, поступившие на вход разомкнувшего петлю петлевого интерфейса, накапливаются в приемном регистре 2, который в этом случае выполняет функцию буфера. Сразу после завершения передачи запросного слова последовательный выход передающего регистра 3 отключается от выхода петленого интерфейса и к последнему подключается последовательный выход приемного регистра 2. Для передачи следуКаждое вычислительное устройство

; петлевой локальной вычислительной сети имеет два режима работы — режим контрол лера петли и режим оконечного устройства.

В режиме оконечного устройства в пе- 40 редающий сдвиговый регистр 3 операционный блок 1 через мультиплексор 6, помещают слово специального формата— ющего запросного слова петлевой интерфейс должен возвратить себе вставленный в петлю приемный регистр 2. Это происходит в тот момент, когда приемный регистр 2 не содержи: передаваемых по петле транзитных сообщений, что обнаруживается блоком 4 управления, и по его команде блок

5 сопряжения замыкает петлевые вход и выход, одновременно отключая последовательный выход приемного регистра 2 от петлевого выхода.

Переданное таким образом в петлю запросное слово, пройдя по ней, попадает на вход вычислительного устройства, находящегося в режиме контроллера петли, и затем в его приемный регистр 2. Дальнейшее продвижение запросного слова по петле прекращается, так как в петлевом интерфейсе вычислительного устройства, находящемся в режиме контроллера петли, блок 5 сопряжения всегда размыкает петлю и подключает к петлевому выходу последовательный выход гередающего регистра 3, Запросные слова, поступающие в приемный регистр 2 вычислительного устройства — контроллера петли, распознаются блоком 4 управления и по его сигналу принимаются через первый порт блока 8 буферной памяти. На время приема запросного слова вход мультиплексора 6 запирается по управляющему сигналу с блока 4 управления. Таким образом в блоке 8 буферной памяти накапливаются запросные слова готовых к обмену вычислитегьных устройств, находящихся в режиме оконечного устройства. В соответствии с очередью запросных слов, анализируемых операционным блоком 1, через второй порт блока 8 буферной памяти, информационную магистраль .7 поступает сообщение для передачи его готовому к приему вычислительному устройству, Слова сообщения через мультиплексор 6 поочередно пом=,щаются в передающий сдвиговый регистр 3, а затем в последовательной форме передаются в петлю, Пройдя по петле, сообщение достигает готового к приему вычислительного устройства, находящегося в режиме оконечного устройства. В нем слова поступившего сообщения поочередно размещаются в приемном регистре 2, а затем через мультиплексор 6 поступают на информационную магистраль 7. Пройдя по петле, сообщение возвращается к передавшему его вычислительному устройству.

После того, как очередь запросных слов исчерпана, вычислительное устройство, выполнявшее функцию контроллера петли, переходит в режим оконечного устройства, а

20

30

50

55 функция контроллера передается следующему петлевому интерфейсу, находившемуся до этого в режиме оконечного устройства.

Уведомление об изменении режима работы в виде командного слова размещается в передающем регистре 3 вычислительного устройства — контроллера петли, а затем передается в петлю, Выбранное вычислительное устройство, находящееся в режиме оконечного устройства, принимает командное слово об изменении режима в приемный регистр 2 и распознает его блоком управления. Блок 4 управления изменяет режим оконечного устройства на режим контроллера петли, выдавая управляющее воздействие на блок 5 сопряжения, который размыкает петлю и подключает последовательный выход передающего регистра 3 к петлевому выходу. После этого работа петлевой локальной вычислительной сети повторяется.

Формула изобретения

1. Вычислительное устройство петлевой локальной сети, содержащее блок сопряжения, операционный блок, блок управления, блок буферной памяти, мультиплексор, приемный сдвиговый регистр и передающий сдвиговый регистр, причем информационный вход устройства (используемый для выхода в локальную сеть) подключен к первому информационному входу блока сопряжения и к информационному входу приемного сдвигового регистра. выход переполнения которого подключен к первому управляющему входу блока сопряжения, выход которого подключен к выходу устройства (используемому для выхода в локальную сеть), первый выход блока управления подключен к управляющему входу передающеro сдвигового регистра, выход переноса которого подключен к второмууправляющему входу блока сопряжения, информационные выходы приемного сдвигового регистра подключены к входам режима блока управления и к информационным входам мультиплексора, выходы которого подключены соответственно к информационным входам нередак щего сдвигового регистра, выходы первой и второй групп блока управления подключены соответственно к управляющим входам группы блока сопряжения и к управляющим входам первой группы мультиплексора, информационные входы-выходы операционного блока через информационную магистраль подключены соответственно к информационным входамвыходам блока управления и мультиплексора, управляющие входы-выходы .операционного блока через управляющую магистраль подключены соответственно к входам-выходам режима блока управления и к управляющим входам второй группы мультиплексора, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия устройства за счет уменьшения времени доступа через петлевой интерфейс, оно сбдержит блок буферной памяти, причем второй выход блока управления подключен к управляющему входу блока буферной памяти, выходы группы которого через информационную магистраль подключены к информационным входам-выходам операционного блока, блока управления и мультиплексора, управляющие входы группы и выход блока буферной памяти через управляющую магистраль подключены к управляющим входам-выходам операционного блока, к входам выходам режима блока управления и к управляющим входам второй группы мультиплексора, информационные выходы приемного сдвигового регистра подключены соответственно к информационным входам блока буферной памяти.

2. Устройство по и. 1. о т л и ч а ю щ е ес я тем, что блок буферной памяти содержит узел памяти, с первого по третий счетчики, с первого по четвертый триггеры, первый и второй элементы И, элемент И-НЕ с первого . по восьмой элементы НЕ, первый и второй элементы ИЛИ и элемент ИЛИ-НЕ, причем первый управляющий вход группы блока подключен к входу первого элемента НЕ и к входам установки в "0" всех счетчиков, выход первого триггера подключен к информационному входу второго триггера, выход которого подключен к первому входу первого элемента И, выход которого подключен к входу синхронизации второго триггера,. второй управляющий вход группы блока подключен к входу второго элемента НЕ, выход которого подключен к входу третьего элемента НЕ и к входу чтения узла памяти, третий управляющий вход группы блока подключен к входу третьего элемента НЕ и к второму входу первого элемента И, выход первого элемента НЕ подключен к первому входу второго элемента И, к входу установки в "0" третьего триггера и к первому входу первого элемента ИЛИ, выход которого подключен к входу установки в "0" четвертого триггера, выход которого подключен к выходу блока, выход третьего элемента НЕ подключен к входу пятого элемента НЕ, выход которого подключен к входу шестого элемента НЕ, выход третьего триггера подключен к информационному входу третьего триггера, к входу седьмого элемента НЕ и к первому входу элемента ИЛИ-НЕ. выход которого подключен к счетным суммирующим входам первого и второго счетчиков и к вто1691846 рому входу второго элемента И, выход которого подключен к входу установки в "О" второго триггера, выход седьмого элемента НЕ подключен к входу восьмого элемента HE u к входу записи узла памяти, выходы которого подключены соответственно к выходам группы блока, выход восьмого элемента НЕ, подключен к второму входу элемента ИЛИ, НЕ, выход четвертого элемента НЕ подклю1, чен к входам синхронизации первого и четвертого триггеров, выход шестого эле мента НЕ подключен к второму входу пер, вого элемента MflM, к счетному, суммирующему входу третьего счетчика и и счетному вычитающему входу второго счетчика, информационные выходы которого подключены к входам элемента И-НЕ и к входам второго элемента ИЛИ, выход которого подключен к информационному входу

5 четвертого триггера, выход элемента И-НЕ подключен к информационному входу перcoro триггера, информационные входы первого и третьего счетчиков подключены соответственно к адресным входам записи

10 и к адресным входам чтения узла памяти, информационные входы которого подключены соответственно к информационным входам блока, управляющий вход которого подключен к входу синхронизации второго

15 триггера.

1691846

Составитель В.Смирнов

Техред М.Моргентал КоРРеКТоР QËîí÷àêoâà

Редактор А .Огар

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Заказ 3929 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5