Систолический процессор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки данных, работающих в реальном времени. Целью изобретения является повышение производительности систолического процессора за счет обеспечения безконфликтного обмена данными между вычислительными модулями. Поставленная цель достигается тем, что в систолический процессор, содержащий К вычислительных модулей, введены К+1 устройств обмена. 1 з.п. ф-лы, 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„"„Ц„„1691847 А1 (5!)5 G 06 F 15/16

ГОСУДАРСТВЕН(ЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,,", ",-",:-.;„, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

I (21) 4746750/24 (22) 03.10.89 (46) 15.11.91. Бюл. t+ 42 (72) А.А.Мельник и И.Г.Цмоць (53) 681.325(088.8) (56) Систолические вычислительные структуры/Под ред. Я.А.Дуброва. АН УССР, ИППММ, препринт ЬВ 3-87, Львов, 1988, л.22, рис.2,3. (57) Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки данных, работающих в реальном времени, Целью изобретения является повышение производительности систолического процессора за счет обеспечения безконфликтного обмена данными между вычислительными модулями, Поставленная цель достигается тем, что в систолический процессор, содержащий К вычислительных модулей, введены К+1 устройств обмена. 1 з.п. ф-лы, 4 ил. (54) СИСТОЛИЧЕСКИЙ ПРОЦЕССОР

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки данных, работающих в реальном масштабе времени.

Цель изобретения — повышение производительности систолического процессора путем обеспечения безконфликтного обмена данными между, вычислительными модулями.

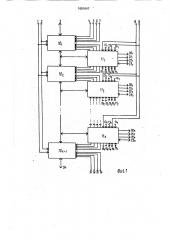

На фиг. 1 изображена блок-схема систо. лического процессора; на фиг. 2 — блок-схема устройства обмена; на фиг. 3 — схема блока управления (обменом); на фиг. 4— схема вычислительного модуля.

Систолический процессор (фиг. 1) содержит первый 1 и второй 2 тактовые вхоДы, информационный вход 3, первые входы 4- 7 соответственно признаков записи в память, считывания из памяти, записи в счетчик и считывания из счетчика. вход 8 сброса, третий тактовый вход 9 (К+1) устройств 10 об.мена, К вычислительных модулей 11, входы

12 прерывания, входы 13 управления переходом, вход 14 признака загрузки, вход 15 разрешения записи, вход 16 разрешения чтения, выход 17 разрешения обращения к памяти программ, вход/выход 18 внешней шины данных, выход 19 синхронизации, выход 20 строба чтения, выход 21 строба записи, выход 22 адреса, вход-выход 23 данных, информационный выход 24, вторые входы

25 — 28 соответственно признаков записи в память, считывания из памяти, записи в счетчик и считывания из счетчика.

Каждое устройство 10 обмена (фиг. 2) включает регистры 29 — 32, блок 33 памяти и блок 34 управления.

Блок 34 управления (фиг. 3) содержит элементы И-НЕ 35-37, буферные усилители

38 и 39 с трехстабильным выходом, коммутатор 40, счетчики 41 и 42, элемент И 43, элементы И-HE 44 и 45. элемент И 46, элемент И-НЕ 47, элемент И 48, инвертор 49, шесть узлов формирователей 50 — 506 импульсов, каждый из которых состоит из элемента И 51, триггеров 52 и 53 и элемента

И-HE 54.

1691841

Каждый вычислительный модуль 11 (фиг. 4) образуют усилители 55 и 56 с трехстабильным выходом, микропроцессор 57, усилители 58 и 59 с трехстабильным выходом, элементы ИЛИ 60 и 61, дешифраторы

62 и 63, элемент И 64, память 65 и элемент

ИЛИ 66..

Систолический процессор работает сле дующим образом.

Сначала осуществляется настройка

10 процессора на решение задачи. Настройка производится путем загрузки в память 65 каждого вычислительного модуля 11 соответствующих программ. Каждая программа, загруженная в вычислительный модуль 11, 15 является частью общей программы решения задачи; В блок 33 памяти первого устройства 10 обмена с выхода 3 загружаются первый массив входных данных и управляющая информация, сопровождающая дан20 ный массив. В управляющей информации указываются кад решаемой задачи, начальный адрес, размерность и состояние массива. Если в ячейке блока 33 памяти, определяющей состояние массива, записан 25 нуль, эта означает, что в блок 33 памяти не загружен массйв данных, а если единица, то зта означает, чта,массив данных загружен и готов к обработке. Управляющая инфарма-! ция записывается в определенн o å адреса 30 блока 33;.Объем памяти блока 3 каждого устройства 10 обмена определяется размерами обрабатываемых массивов данных и их управляющей информацией. Минимальный.абъем блока 33 памяти должен 35 обеспечивать хранение двух максимальных массивов данных с их управляющей информацией.

Перед началам работы в первую область блока 33 памяти устройства 101 абме- 40 на загружены первый массив данных и его управляющая информация, причем в ячейках, определяющих состояние двух абла" стей памяти, записаны единица и нуль, В ячейках, определяющих состояние блока 33 45 памяти устройств 10 -10к+1обмена, записаны нули..При установке на входе 8 единицы процессор из состояния астанова переходит на выполнение программ, записанных в памяти 65 вычислительных модулей 11. В 50 каждом вычислительном модуле 11 в начале работы анализируются ячейки, определяющие состояние блока 33 памяти устройств

10 обмена. Если в этих ячейках записан нуль, та саатветствующие вычислительные 55 модули 11 переходят в режим ожидания, а если единица, та на обработку массива.

В начале работы процессора первый вычислительный модуль 11 па результатам анализа переходит на обработку массива, записанного в первой области блока 33 памяти, а вычислительные модули 112-11к — режим ожидания. Первый вычислительный модуль 11 считывает код,решаемой задачи и переходит на решение первой части данной. задачи над данными, записанными в первой области блока 33 памяти. Результаты решения первой части задачи вычислительным модулем 11 записывается в первую область блока 33 памяти второго устройства

10г обмена. Результаты обработки входного массива первым вычислительным модулем

111 ÿâëÿþòñÿ входными данными для второго вычислительного модуля 112. Вместе с данными в блок 33 памяти устройства 10 обмена записывается его управляющая информация. По окончании обработки первого входного массива и загрузки результатов его обработки в первую область блока 33 памяти устройства 10 обмена в ячейки состояния данных областей блока памяти соответственна первого 10 и второго 10 устройств обмена записывается нуль и единица. Одновременно с обработкой массива с первой области блока 33 памяти устройства 101 обмена во вторую область блока 33 памяти данного устройства обмена с входа

3 загружается второй массив данных со своей управляющей информацией, Па окончании загрузки информации во вторую область блока 33 памяти устройства 10> обмена в ячейку состояния данной области блока 33 памяти записывается единица. По завершении обработки первого массива данных и загрузки результатов данной обработки в блок 33 памяти устройства 10 обмена вычислительный модуль 111 переходит в режим ожидания. В режиме ожидания вычислительные модули 11> — 11к находятся до прихода сигнала прерывания на входы

121, 122, ..., 12к. Период поступления сигналов прерывания равен или больше требуемого времени для решения любой I-й части задачи и совпадает с периодом поступления в процессор массивов данных. Процессор синхранизируется сигналами прерывания, т.е. работает в принудительном темпе с тактом, равным периоду поступления сигналов прерывания.

В начале следующего такта работы каждый вычислительный модуль 11 анализирует ячейки, определяющие состояние блока 33 памяти устройств 10 обмена, и в зависимости ат записанной в них информации переходит на обработку или на ожидание. Во втором такте первый 111 и второй 112 вычислительные модули переходят на обработку массивов данных, а вычислительные модули

11э-11к — в режим ожидания.

10

20

55

Вычислительные модули 11> и 11 считывают код решаемой задачи и переходят на решение первой и второй частей задачи.

Вычислительный модуль 11 обрабатывает данные с второй области блока 33 памяти устройства 10 обмена и результаты данной обработки загружает во вторую область блока 33 памяти устройства 10 обмена. Одновременно в первую область блока ЗЗ памяти устройства 10> обмена производится загрузка с входа 3 следующего массива. При обработке второго входного массива вычислительный модуль 11 использует вторые области блока 33 памяти устройств 10> — 10 обмена. Вычислительный модуль 11 обрабатывает данные с первой области блока 33 памяти устройства 102 обмена и результаты данной обработки загружает в первую область блока 33 памяти устройства 10э обмена. Перед третьим тактом работы процессора в первой области блока 33 памяти устройства 10 обмена находится третий входной массив с управляющей информацией, а во второй и первой областях блока 33 памяти соответственно второго 10 и третьего 10э устройств обмена записаны массивы данных с управляющей информацией для следующего такта работы. B последующих тактах работа процессора аналогична описанной. .Формула изобретения

1. Систолический процессор, содержащий К вычислительных модулей, о т л и ч аю шийся тем, что, с целью повышения производительности за счет обеспечения безконфликтного обмена, в него введены (К+1) устройств обмена, причем первый и второй тактовые входы процессора соединены соответственно с первыми и вторыми тактовыми входами .всех устройств обмена, входы признаков записи в память, считывания иэ памяти, записи в счетчик, считывания из счетчика процессора соединены с одноименными первыми входами первого устройства обмена, вход сброса процессора— с входами сброса всех вычислительных модулей, третий тактовый вход процессора соединен с входами синхронизации вычислительных модулей, информационный вход-выход процессора соединен с первым информационным входом-выходом первого устройства обмена, первые выходы признаков записи в память, считывания из памяти, записи в счетчик, считывания из счетчика 1-го вычислительного модуля (! 1, 2, ...К) соединены соответственно с одноименными вторыми входами J-го устройства обмена (J = 1, 2, „., К+1), вторые выходы признаков записи в память, считывания иэ памяти, записи в счетчик, считывания иэ счетчика l-ro вычислительного модуля соединеныы соответственно с одноименными входами (J+1)-го устройства обмена, информационный вход-выход i-го вычислительного модуля соединен с вторым информационным входом выходом !-го устройства обмена и первым информационным входомвыходом (J+1)-ro устройства обмена, 2.Процессор по и. 1, отл ича ю щийся тем, что устройство обмена содержит четыре регистра, блок памяти и блок управления, причем первый и второй тактовые входы устройства обмена соединены с одноименными входами блока управления, выходы адреса и признака запись/чтение соединены с одноименными входами блока памяти, информационный вход-выход которого соединен с одноименными входами первого и второго регистров и выходами третьего и четвертого регистров, информационный выход первого регистра соединен с одноименным входом третьего регистра, первым информационным входом блока управления и является первым информационным выходом устройства обмена, информационный выход второго регистра соединен с одноименным входом четвертого регистра, вторым информационным входом блока управления и является информационным выходом устройства обмена, первые входы признаков записи, считывания, записи в счетчик, считывания счетчика устройства соединены с одноименными первыми входами блока управления, вторые входы признаков записи, считывания, записи в счетчик, считывания счетчика устройства соединены с одноименными вторыми входами блока управления, первый и второй выходы сброса блока управления соединены с одноименными входами соответственно третьего и четвертого регистров, входы сброса первого,и второго регистров соединены соответственно с первым и вторым входами признаков считывания блока управления, первый и второй выходы синхронизации которого соединены соответственно с одноименными входами первого и второго регистров, входы синхронизации третьего и четвертого регистров соединены соответственно с первым и вторым входами признаков записи блока управления.

1691847

1691847

1691847

1691847

Вбей

Составитель Б. Резван

Техред М.Моргентал

Корректор 3.Лончакава

Редактор А .Огар

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 3929 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5