Статистический анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для определения закона распределения времени наработки на отказ и характера возникающих отказов по малому числу испытаний технических изделий. Целью изобретения является расширение функциональных возможностей анализатора за счет дополнительного оценивания характера отказов технических изделий по малому числу испытаний . Цель достигается тем, что путем анализа выборочного значения первого нормированного начального момента распределения времени наработки на отказе анализаторе осуществляется проверка гипотезы о принадлежности отказов испытуемых изделий одному из трех классов: отказы на этапе приработки, случайные отказы и отказы из-за старения изделий. Идентификация характера отказов осуществляется по наличию единичного кода на соответствующем входе блока индикации. Анализатор содержит аналого-цифровой преобразователь 1, блок 2 вычисления начальных моментов, блок 3 вычисления среднеквадратического отклонения , делители 4,10-14. вычитатели 5,21, счетчик 6, элементы 7, 25-28 сравнения, блок 8 вычисления квадратного корня, синхронизатор 9, интеграторы 15-19, регистр 20. умножитель 22, элементы НЕ 23, 24, блок 29 интерполяции, блок 30 индикации, элемент И 31. Зил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)э 6 06 F 15/336

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИ аиг.2

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4797863/24 (22) 01.03.90 (46) 15.11.91. Бюл. ЬЬ 42 (71) Уфимский авиационный. институт им.Серго Орджоникидзе (72) Ю.Е;Алыпов, В.Е.Гвоздев, С.В.Фатиков и Д.Г.Евсеев (53) 681,3(088.8) (56) Авторское свидетельство СССР

М 1024935,.кл. G 06 F 15./36, 1982.

Авторское свидетельство СССР

N. 1310842, кл. G 06 F 15/36, 1986. (54) СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР (57) Изобретение относится к вычислительной технике и может быть использовано для определения закона распределения времени наработки на отказ и характера возникающих отказов по малому числу испытаний технических иэделий. Целью изобретения является расширение функциональных возможностей анализатора за счет дополнительного оценивания характера отказов технических иэделий по малому числу испы,, Я,, 1691854 А1 таний. Цель достигается тем, что путем анализа выборочного значения первого нормированного начального момента распределения времени наработки на отказ в анализаторе осуществляется проверка гипотезы о принадлежности отказов испытуемых изделий одному из трех классов: отказы на этапе приработки, случайные отказы и отказы из-за старения изделий. Идентификация характера отказов осуществляется по наличию единичного кода на соответствующем входе блока индикации. Анализатор содержит аналого-цифровой преобразователь 1, блок 2 вычисления начальных моментов, блок 3 вычисления среднеквадратического отклонения, делители 4, 10 — 14, вычитатели 5, 21, счетчик 6, элементы 7, 25 — 28 сравнения, блок 8 вычисления квадратного корня. синхронизатор 9, интеграторы 15-19, регистр 20, умножитель 22, элементы НЕ 23, 24, блок 29 интерполяции, блок 30 индикации, элемент И

31. 3 ил.

1691854

Изобретение относится к вычислитель ной технике и может быть использовано для определения закона распределения времени наработки на отказ и характера возникающих отказов по малому числу испытаний технических изделий, Цель изобретения — расширение функциональных возможностей анализатора путем дополнительного оценивания

10 характера отказов технических изделий по малому числу испытаний.

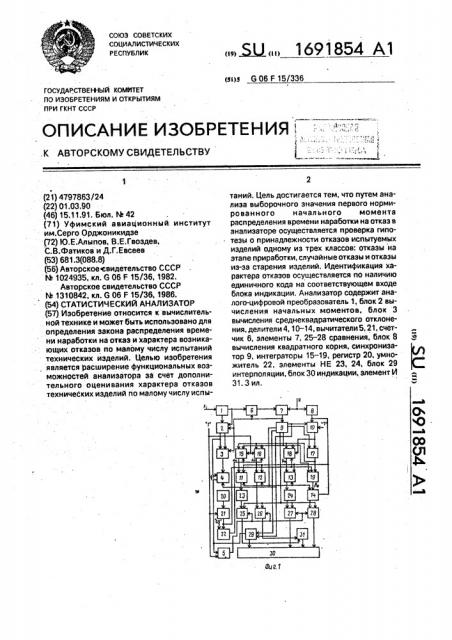

На фиг. 1 приведена функциональная схема статического анализатора; на фиг. 2— функциональная схема третьего интегратора; на фиг, 3 приведена возможная функциональная схема второго интегратора.

Анализатор содержит аналого-цифровой преобразователь 1, блок 2 вычисления начальных моментов„блок 3 вычисления

20 среднеквадратического отклонения, первый делитель 4, первый вычитатель 5, счетчик 6, первый элемент 7 сравнения, блок 8 вычисления квадратного корня, синхронизатор 9„второй — шестой делители 10--14, первый — пятый интеграторы 15-19, регистр

20, второй вычитатель 21, умножитель 22, первый и второй элементы НЕ 23 и 24, второй- пятый элементы 25-28 сравнения, блок 29 интерполяции, блок 30 индикации и элемент И 31

Интегратор 17 (фиг. 2) включает генератор 32 линейно изменяющегося напряжения, генератор 33 тактовых импульсов, накапливающий сумматор 34, аналого-цифровой преобразователь 35, блок 36 вычисления экспоненты, элемент 37 задержки, элемент 38 сравнения и регистр 39.

Интегратор 15 (фиг, 3) образуют генератор 40 линейно изменяющегося напряже40

Интеграторы 15 и 18 полностью аналогичны, Интеграторы 16 и 19 аналогичны интеграторам 15 и 18, за исключением того, .что либо вместо вычитателя используется сумматор, на вход которого подается значение нижнего предела интегрирования (ин-. 50 тегратор 16), либо вычитатель отсутствует при нулевом нижнем пределе интегрирования (интегратор 19).. В основе оценивания характера отказов испытуемых изделий лежат следующие теоретические положения.

1. Различным причинам отказов (отказы на этапе приработки, случайные отказы, отказы из-за старения иэделий) соответствуют! ния, генератор 41 тактовых импульсов, накапливающий сумматор 42, аналого-цифровой преобразователь 43, блок 44 вычисления экспоненты, элемент 45 задержки. вычитател ь 46 и регистр 47. (3) различные классы, законов распределения времени наработки отказа.

2. Класс распределения однозначно идентифицируется значением первого нормированного начального момента 4, т,е. отношением математического ожидания к среднеквадратическому отклонению:

4 =v>/и (1)

Отказам на этапе приработки соответствует 14< 1, случайным отказам (экспоненциальный закон распределения времени наработки на отказ) — 4 - 1, отказам на этапе старения —. 14 1.

3, Среднеквадратическое отклонение выборочного значения первого нормированного начального момента 4 равно 1/ (Й, Распределение при N> 10 практически можно считать нормальным.

В анализаторе осуществляется проверка гипотезы и принадлежности одному из трех классов: Й< 1 (отказы на этапе приработки); 4 - 1 (случайные отказы); Р 1 (отказы из-за с гарения изделия), Проверка гипотезы о характере отказов сводится к следующему. л

1. Значимо ли 4 меньше единицы(если значимо, то экспериментальным данным не противоречит гипотеза об отказах этапа приработки).

2. Значимо ли 4 больше единицы(если значимо, то экспериментальным данным не противоречит гипотеза от отказах из-за старения изделий). л

3. Если отклонения 4 от единицы незначимы, то экспериментальным данным не противоречит гипотеза о случайной характере отказов.

Оценка значимости отклонения 1 от единицы сводится к проверке следующих условий: в случае 1

4 — 1 < — ДНЯ . (2) в случае 2

Й-»РьМй в случае 3 — а„/ /Й (д .— 1 < а /1/й (4) где АД,ан,аь — критические области выбранных критериев проверки гипотез, причем для

fp fop(P)04 = 1 — ч (5) дл фа

Ф Ф (Й)сй = 1 — а (Ы

1691854

55 дляан

J fypp(P) = (1 — «})/2 (7) дляад

) 1унр(р()М = (1 — >>)/2 (8) где q — заранее выбранный уровень значимости критерия;

fy))p (Й) — плотность усеченного нормального распределения параметра Й .

В анализаторе используется усеченное нормальное распределение параметра Ф ЖАНР(Й = С <н-оР>1(Р(>)>, (б) где С вЂ” нормированный множитель тноР) 2 (Й) — flllOTHOCTb НоРмальНОго РаСпределения.

Это обусловлено тем, что время наработки на отказ является неотрицательной величиной. Значение С при этом определяется из условия

С = 1/. f>1op(>(()Л)(М (10) учитывая известное в теории математической статистики положение о том, что любая непрерывная случайная величина с вероятностью, близкой к единице, распределена на интервале (А, А + 7 а), где А— нижняя граница области возможных значений случайной величины (при обработке данных об отказах А принимает значение нуль); о — среднеквадратическое отклонение случайной величины, при обработке данных об отказах 0 = 1МН, выражение(9) принимает вид

1>нр(уу) (11)

f,ex»(, )»>>1

Аналогичные рассуждения позволяют без потери точности использовать в качестве верхнего предела интегрирования в формуле (5) величину 7/ V5l.

При работе анализатора возможна ситуация, когда выборочное значение М удовлетворяет следующим условиям:

8>» —.P./Ëà (12) либо

1«< 1 — ANГ (13)

Другими словами, возможна ситуацИя, когда различные гипотезы о характере отказов одновременно не противоречат опытным данным. В этом случае для отбраковки одной из конкурирующих гипотез требуется проведение дополнительных испытаний.

Анализатор работает следующим образом.

Исследуемый случайный сигнал, представляющий собой выборку значений наработки на отказ испытуемых технических изделий, поступает на вход аналого-цифрового преобразователя 1, с информационного выхода которого коды исследуемых реализаций х((} - 1, N) поступают на вход блока 2 вычисления начальных моментов.

На выходе блока 2 формируются коды выборочных оценок первых двух начальных моментов случайной величины, поступающие на входы блока 3 вычисления среднеквадратического отклонения. На выходе делителя

4 по импульсу с первого выхода синхронизатора 9 формируется код выборочной оценки первого нормированного начального

"и момента, поступающий на вход блока 29 интерполяции, управляемого импульсами с первого и второго выходов синхронизатора

9. На выходе блока 29 формируются коды ординат решетчатой функции распределения, поступающие на соответствующий вход блока 30 индикации. Таким образом, построение оценки закона распределения осуществляется так же, как и в известном анализаторе.

Характер возникающих отказов оценивается следующим образом. Импульсы окончания преобразования реализации с выхода аналого-цифрового преобразователя 1 тактируют блок 2 вычисления начальных моментов и подсчитываются счетчиком

6. По окончании преобразования выборки код на выходе счетчика 6 совпадает с заданным кодом N объема выборки анализатора.

При этом на выходе элемента 7 сравнения формируется импульс запуска синхронизатора 9, по импульсу с первого выхода которого в делителе 10 вычисляется код 7/ VN, поступающий на вход задания верхнего предела интегрирования интеграторов

17 и 18.

Процесс численного интегрирования в интеграторе 17 реализуется следующим образом. Интегратор 17 тактируется импульсом с третьего выхода синхронизатора 9, который обнуляет накапливающий сумматор 34 и запускает генератор 32 линейно изменяющегося напряжения и генератор 33 тактовых импульсов. На выходе генератора

32 формируется линейно возрастающее напряжение начиная с нулевого уровня. На выходе аналого-цифрового преобразователя 35, управляемого импульсами с выхода генератора 33, формируются коды переменной интегрирования 4, изменяющиеся с шагом Л величины интервала дискретизации и поступающие на вход блока 36 вычис1891854 зы этапа приработки и на выходе элемента

28 сравнения на отказы из-за старения. На этом работа анализатора заканчивается. - . О р м у л а и 3 О б р 8 т е н и я татистический анализатор, содержа щий аналого-цифровой преобразователь, 4Q бло,: вычисления начальных моментов, блок вы.лсления среднеквадратического отклонения, делитель, блок интерполяции и синхронизатор, причем информационный вход и вход запуска аналого-цифрового преобразователя являются входом задания реалиэа- 5Q ций и тактовым входом анализатора, выход первого момента блока вычисления начал»ных моментов соединен с одноименным входом блока вычисления среднеквадратического отклонения, с входом делимого делителя, выход второго момента блока вычисления начальных: моментов соединен с одноименным входом блока вычисления среднеквадратического отклонения, выход которого соединен с входом делителя делиЛения экспоненты. В блоке 36 последоваТ8Л ЬНО фОРМИ РУЮТСЯ КОДЫ 8ll8t48 HTBP HblX интеовалОв л р . " ф <оторые суммируются далее в накапливаю(цем сумматоре 34. При совпадении кода на

ыходе преобразователя 35 с эаданнь .м зна,нием верхнего предела интегрирования на выходе элемента 38 сравнения формируется импульс остановки генераторов 32 и

33. ПООцесс интегрирования заканчивается и в регистр 39 переписывается вычисленное г;риближенное значение интеграла пГ 15

f exp() йЛ. поступающее далее на входы задания зна,менателя подынтегральной функции интег,,раторов 15, 15, 18 и 19, где по импульсу с четвертого выхода синхронизатора 9 осуществляется flpGUGcc интегрирования соглас,О >,5,-(8). На выходах интеграторов 15, 1б, l8 «19 формируются соответственно коды, Он,%,„В|„и Д, поступающие далее на входы, дели;елей 11-14. По импульсу с пятого выхода с.; нхрониеатора,9 на выходе элемента

НЕ 23 формируется код (— а„. К) ., На выходе делителя 12 — код (а,МЙ), на выадеэлемента НЕ 24--код (— 9„ММ), на 3О выходе делителя 14 — код @ АЙ) . Логика работы элементов 25 — 28 сравнения такова, .то единичный код на их выходах формируется при выполнении неравенств(2Н4). Та, ким образом, появление единичного кода на 35, выходе элемента И 31 указывает на случай, ный характер отказов испытуемых изделий, на выходе элем8нта 27 сравн8ния — на QTKB теля, выход которого соединен с информационным входОМ блока интерполяции, тактовый вход и вход опроса которого соединены соответственно с первым и вторым выходами синхронизатора, о т л и ч а юшийся тем, что, с целью расширения функциональных воэможностей анализатора за счет оценивания характера-отказов технических изделий по малому числу испытаний, в него дбполнительно введены два вычитателя, счетчик, пять элементов сравнения, блок вычисления квадратного корня, второй — шестой делители, пять интеграторов, регистр, умножитель, два элемента НЕ, блок индикации и элемент И, причем информационный выход аналого-цифрового преобразователя соединен с информационным входом блока вычисления начальных моментов, выход первого делителя — с входом уменьшаемого первого вычитателя, вход вычитаемого которого соединен с входом уменьшаемого второго вычитателя, с входом задания верхнего предела интегрирования первого интегратора, с входом задания нижнего предела интегрирования второго интегратора и является входом задания кода "1" анализатора, выход окончания преобразования аналого-цифрового преобразователя соединен с тактовым входом блока вычисления начальных моментов и с информационным входом счетчика, выход которого соединен с первым входом первого элемента сравнения, второй вход которого соединен с входом блока вычисления квадратного корня и является входом задания Й Объема выборки анализатора

"Равно", выход первого элемента сравнения соединен с входом установки в "О" счетчика, с входом останова блока вычисления начальных моментов, с тактовым входом блока вычисления среднеквадратического отклонения и входом запуска синхронизатора, выход блока вычисления квадратного корня соединен с входами делителя с второго по шестой делителей, вход делимого второго делителя является входом задания кода "7" анализатора, тактовый вход второго делителя подключен к тактовому входу первого делителя и первому выходу синхронизатора, третий выход которого подключен к тактовому входу третьего интегратора, вход задания верхнего предела интегрирования которого соединен с одноименным входом четвертого интегратора и подключен к выходу второго делителя, выходтретьего интегратора подключен к информационным входам с первого по пятый интеграторов, тактовый вход которых соединен с четвертым выходом синхронизатора, пятый выход которого соединен с так10

1691854 б;6

Ю, М

Иэ сина.З

Составитель В.Орлов

Техред М.Моргентал

Редактор А;Огар

Корректор Э.Лончакова

:Заказ 3929 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 товыми входами с третьего по шестой делителей, выход регистра соединен с входом вычитаемого второго вычитателя, выход которого соединен с входом задания результирующей величины интеграла четвертого и пятого интеграторов и первым входом умножителя, второй вход которого является входом задания кода "0.5" анализатора, выход умножителя соединен с входом задания результирующей величины интеграла первого и второго интеграторов, выходы значения нижнего предела интегрирования первого и четвертого интеграторов соединены соответственно с входами делимого третьего и пятого делителей, выходы значения верхнего предела интегрирования второго и пятого ийтеграторов соединены соответственно с входами. делимого четвертого и шестого делителей, выход третьего делителя через первый элемент НЕ соединен с первым информационным входом второго элемента сравнения, выход четвертого делителя — с первым информационным входом третьего Иэси о.ю элемента сравнения, выход пятого делителя через второй элемент НЕ соединен с первым информационным входом четвертого элемента сравнения, выход шестого делителя — c

5 первым информационным входом пятого элемента сравнения, выход первого вычитателя — с вторыми информационными входами с второго по пятый элементов сравнения, шестой выход синхронизатора соединен с такто10 выми входами с второго по пятый элементов сравнения, выход блока интерполяции соединен с входом функции распределения блока индикации, выход "Больше" второго элемента сравнения соединен с первым входом эле15 мента И, второй вход которого соединен с выходом "Больше" третьего элемента сравнения, а выход — с входом признака случайных отказов блока индикации, выход "Больше" четвертого элемента сравнения соединен с

20 входом признака отказов приработки блока индикации, а выход "Больше" пятого элемента сравнения — с входом признака отказов старения блока индикации.