Делитель частоты с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники , в синтезаторах частот. Цель изобретения - повышение надежности работы за счет обеспечения фиксации сигналов переноса первого и второго программируемых делителей частоты - достигается путем введения в делитель триггеров 12-16, элемента ИЛИ-НЕ 17, элементов НЕ 18-20 и образования новых функциональных связей. Кроме того делитель содержит высокочастотный делитель 1 частоты, программируемые делители 3 и 4 частоты, триггеры 5 и 6, элементы И 7 и 8, элемент ИЛИ-НЕ 9, блок управления 10, входную и кодовую шины и три шины управления . 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ сОциАлистических

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЭОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОП ИСА НИ Е И ЗОБ РЕТЕ НИЯ )

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1 (21) 4716343/21 (22) 05.07,89 (46) 15.11.91. Бюл. № 42 (72) И.И.Корниенко, П.В,Сахон и В.И.Яровой (53) 62 1,374.4(088.8) (56) Авторское свидетельство СССР

¹ 502503, кп. Н 03 К 23/00, 1979, Авторское свидетельство СССР № 1354416, кл. Н 03 К 23/66, 1986, (54) ДЕЛИТЕЛЬ ЧАСТОТЫ C ПЕРЕМЕНHbIM КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ (57) Изобретение относится к импульсной технике и может быть использовано в устИзобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, в синтезаторах частот, Цель изобретения — повышение надежности работы — достигается за счет обеспечения фиксации сигналов переноса первого и второго программируемых делителей частоты.

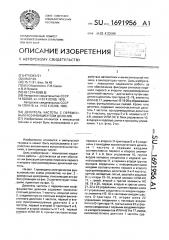

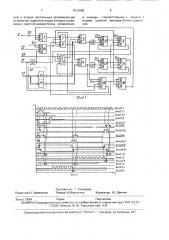

На фиг, 1 приведена электрическая функциональная схема устройства; на фиг. 2— временные диаграммы, поясняющие его работу (позиции на фиг. 2 соответствуют позициям, принятым на фиг. 1), Делитель частоты с переменным коэффициентом деления содержит высокочастотный делитель 1 частоты, входную шину

2, соединенную со счетным входом высочастотного делителя 1 частоты, первый и второй программируемые делители 3 и 4 частоты, первый и второй D-триггеры 5 и 6, первый и второй элементы И 7 и 8, первый элемент ИЛИ-НЕ 9, причем тактовые входы

5U, 1691956 А1 ройствах автоматики и вычислительной техники, в синтезаторах частот. Цель изобретения — повышение надежности работы за счет обеспечения фиксации сигналов переноса первого и второго программируемых делителей частоты — достигается путем введения в делитель триггеров 12 — 16, элемента

ИЛИ-НЕ 17, элементов НЕ18-20иобразования новых функциональных связей. Кроме того делитель содержит высокочастотный делитель 1 частоты, программируемые делители

3 и 4 частоты, триггеры 5 и 6, элементы И 7 и 8, элемент ИЛИ-НЕ 9, блок управления 10, входную и кодовую шины и три шины управления. 1 з.п. ф-лы, 2 ил. первого и второго 0-триггеров 5 и 6 соединены с выходами высокочастотного делителя 1 частоты и первыми входами. соответственно первого и второго элементов И 7 и 8, блок управления 10, группа входов которого соединена с кодовой шиной устройства 11, а первая и вторая группы выходов соединены с информационными входами соответственно первого и второго программируемых делителей 3 и 4 частоты, третий, четвертый, пятый, шестой и седьмой

D-триггеры 12 — 16, второй элемент ИЛИ-НЕ

17,,;первый, второй и третий элементы НЕ

18, 19 и 20, первую, вторую и третью шины

21, 22 и 23 управления, причем первая шина

21 управления соединена со входом перво-го элемента НЕ 18 и тактовым входом шестого D-триггера 15, вторая шина 22 управления соединена с тактовым входом пятого 0-триггера 14, третья шина 23 управления соединена с первыми входами первого и второго элементов ИЛИ-НЕ 9 и 17, выход высокочастотного делителя 1 частоты сое3 динен с тактовым В:<адам седьмого 0-триггера 16, инверсный выход которого соединен с первым и вторым управляющими входами высзкочастотнога делителя 1 частоты, Выход первого элемента НЕ 18 соединен с устанавочнь)ми =(, -входами первого, второго и пятого D-тр lrrj: ров 5, б и 14, выход пер;cro программируемого делителя 3 часTGTbi соединен с установс)чн1ым S-Входом шестога D-триггера 15 v -(epee Bта)>ай 3!18мен Г HE 19 с тактовым входом третьего }:::113ИГгера 12, ВЫХОД BTi3pof 3

ПРО РаММИРУЕМОГО Д6ЛИГЕГгв 4 ЧВСтОТЫ СоеД!г!НЕН С УСтаНОВОЧНЫМ К-}3ХОДОМ ШВСТОГО ". григгера 15 и через третий элемент 1-.Е 20 с

T3KTOBbIM Вх<3дом Чеl вер}ТОГС l3 ТГ}И(ч г)р3 l,i, инверсный выход шестого 0-тоиггера 15 c()единен са BlopbIM Входа(4 перВОГО элемен1 а

И 7. а прямой выход — с информационным входом седьмого 0--риг;ера 16 и сс, вторым входом второго элемента И 8, третий вхац которого соединен стре,тьим вхо,цом первого элемента И 7 и с прямым вь}ходом пят(на

D-Триггера 14, ВЬIХОДЬ1 llepBOf О И BTOpoil О элементов И 7 и 8 саед}и1-)ены са счетны и

Вхацами саатветств8нна пеаВОГО и BTGpo!«О программируемых Дел!4тег!ей 3 и 4 час!аты, ВХОДЫ УСтаНОВКИ (GTQPBI)(г ОЕБИНВНЫ „ ВЬ(Х 3дами coo ãâåòñòâåííî перво о и второго эле ментов ИДИ-НЕ 9 }х 17. Вторые Вха >ы

l .От арых падкл юч8 и ы к i lp5! мы м выхода }4 саС}тввтСТВЕННО ПЕРВОГО и ВТОРОГО Г:)-тг)ИГ18-!

}03 5 И 6 ИНВ 13С1-. Ые В1}ха(}Ы К 3Т001:IX .)одк.!}юч61-1ы к установочным Я-вхс)дам сас.тзетcTBBHHG третьего л:етверта:о 13"Tpf!r 8,".!ОВ l2 и 13, 3 инф013мацианны{э B)(!3gb! -- к прэ}иым выходам сООтветственHi3 таетьеГ(, и

";8 i BepòQÃ0 В триггеров 1 . и; 3, Ьлок управления 10 содержит первый и второй элементы ПЗу 24 N 25, адgecH! Ic

Вх!3ДЫ KQTQPblX СОЕДИН BНЫ С ГРУППОЙ ВХОДОВ алака управления 10, а ВыхаДы соответственна С flePBQ!i! И Втг3 )ОЙ ГP } fir!OÉ ВЫХОДОВ

Ь ака управления 10. ,Целитель работает сг!едуюшим аб!>33(.м.

Б исходном состоянии Ilcl Входн!3Й кадовсй шине 11 на первом 24 и втором 25 ПЗу формируется начальный адрес ПЗУ, П3 прих13ду на устаноВачный ВхаД 23 ус Гоайс1 Ва

KiIïóëbc3 через первый 9 и второй 17 э 1614 )HTbl ИГ!И-НЕ на раэрешaюшие Входы

rIe13ВОГо 3 и BTopol 4 lii!301 133MMируемых дгсЛ11телЕЙ ЧВСТОТЫ ПОСТУГ136"г Сиг:"13«» ro Ка foрому происходлт перепись информации лз

Г!ЗУ в первый 3 и воз„,с)Й 4 программируем.е делители частÎlb! с-}от elcTBBHHG. П

„»-(,q 2 1! устройс, ва B yI(; с цнаe -о(1 ОЯ ij ie устанавливаются перв},!Й 5, второй 0 и пя10

}i» .3

4»

50 тый 14 триггеры (через первый зле .i НЕ

18), а шестой триггер 15 устанавли =3;тся В единичное состояние, при 310М на В)арс:м входе второго трехвходового элемент". И Я

И На ИНфОРМаЦИОННОМ ВХОДЕ CÖb«40r= ТРИ« гера 16 появляется разрешающий сиг}13 ° (BbIcoI(or0 уровня), на втором B)<0-.,6 пэрзага трехвходового элемента И 7- сигнал запрещающий (нис(кого уровня), блоки ру10щий работу первого про}граммируемага делителя

»Iаст0ты 3. Гl(ЗИ flocTупгeHNll !IG BTGpoM )Iflравляющему входу 22 имг.;..ьса срабатывает пятыи Гpv!rep ",4, разг38шающий прохожденис имг)ульсов с высокочастотнаГа ДелителЯ 1 Н3 сч8тньlй ВХОД втараГО llpo

rp3MMI4pу8м0ГО делителя 4 hacTQTbI, этом пО (1) pOHT)f импульса праисхОдит сраааТЫВВНИ8 г 8ДЬМОГО Триггера 16, уСТВНавливающего максимальный коэффициент деления Высокочастотного делителя 1, пс срезу импульса проис. :одит считыванле информации вторым програм(.}ируе}»ь}м делителем 4 частатьi. В котором заплсана информа} !И}я младших разрядов коэффициента .целения, После считываниЯ информации импульсом переноса второго программируемог0

Делит8ЛЯ 4 »3CTQTbI шестой триГГBр 15 пО

ВТОРГ МУ )Гс raHGB!3 (HOIST У ВХОДУ )гстаНВВЛИВа6Tcr в нулевое состояHIle, блокируя !IG BTGрому входу второй тре:<Входавый элемент И

3 и разрешает прохождение импульссв с

ВысакачастатнОГО Д6лителЯ 1 через первыЙ трехвхолавый злемен.г 4i 7 íà счетный Вход пе13ВОГС ;. ОГраммируемОГО дели: еля (час"

ТОТЫ, ОДНОВ, 38146ННО Г}0 фг)ОНТУ ИМГ}УЛЬСВ С

ВысОкачас1отнОГО д8лит6ля i седьмой TpNI

Гер 16 перехс}дит в нулевое состояние, си«и ал ом с О брат нога 3 bI)

Вь}со кача с, 0TH GM дел ител8 1 уста на Вл и Вается минимальный коэффициент деления, при этом импульсом переноса со второго программируемого дели-:еля 4 частоты через третий элемент HE 20 пять Й триггер переВОДИТСЯ В 6ДИНИЧНОЕ СО(TG)iHü48, Раа .ешая перевод триггера 6 В единичное состояние

r1Q GH8p8jII!Ому и>4пульсу Вь}сокача(та i ного делителя 1, обеспечивая запись инф рмации через Второй элемент ИЛИ+1Е ";7 ва второй программируемый делитель 4 -;астоты со второго ПЗУ 25, В катаром после устан О В }< I4 н а -:. 3 л ь н а Г О ад р еса и 0 в х од н о и кодовой шине "=1 установился очередной адР 6» г

Па срезу импульсов с вь;=Око;астатного делителя I п130исхадит счиl ывани6 информации пеpBbIM праГ()аммлруемым делите лем 3 частать, В ка;.ором записана инфармааия ст 3рши::. 133зр>}„" )3 казффици8НТ3 ДЕЛЕНИЯ. l 691951. .

После считывания информации импульсом переноса первого программируемого делителя 3 частоты шестой триггер 15 00 первому установочному входу переводитс.-: в единичное состояние, блокируя по второму входу первый трехвходовый элемент И 7 и разрешает прохождение импульсов через второй трехвходовый элемент И 8, при этом импульсом переноса с первого программируемого де: ..ь. - 3 частоты через второй элемент Н Е 9 т;:.,етий триггер 12 пе реводится в единичное состояние, разрешая перевод г.ервого . риггеоа 5 в единичное состояние по очередному импульсу с высокочастотного делителя 1, обеспечивая запись через первый элемент ИЛИ-HF 9 в первый программируемыйделитель 3 частоты с первого ПЗУ 24 (по его очередному адресу). Далее цикл повторяется, Таким образом, работу делителя частоты с переменным коэффици8нтом дел6ния можно описать выражением

N == Г макс Йма + 1 амин Ист, ГД8 Ймакс, амин маКСИмаЛЬНЫй И МИНИмальный (фиксированные) коэффициенты пересчета высокочастотного делителя 1 частоты, соответственна;

1 ма(1ст) ЧИСЛО МЛадШИХ (СтдрШИХ) ЗНаЧЕНИй 1 1макс(Iмнн).

OT выбора конденсатора 25 зависит максимальный коэффициент деления делителя, обычно при коэффициенте деления до

200 МГц С = 1000 пФ.

Б кач8стве высокочастотного дели iеля

1 частОты может быть использована микро схема, например 193 ИЕЗ, В качестве программируемь.х делителей частоты могут быть использованы несколько соединенных последовательно счетчиков типа, например, 533ИЕ7 (ОСТ 11

340,917-84), в качестве триггеров — микросхемы 533 ТМ2 (ОСИ 11 340.917 — 8Ф, при этом неиспользованные входы микросхем подключаются к шине питания или к шине

"Общий", В качестве ПЗУ могут быть»спользованы микросхемы типа, например, М1623РТ1А, Формула изобретения

1. Делитель частоты с переменным ко- эффициеHTof4 p638HW9, содеожащий BBICGкочастотный д8лит8ль частОты, QxoöHvlo шину, соединенную со счетным входом высокочастотного делителя частоты, первый и второй программируемые делители частоты, первый и второй 0-триггеры, первый и второй элементы И, первый элемент ИЛИН Е., пРИЧем Так;Овые BXO+bl Il6pBOI 0 in BTO рого 0-триггеров соединены с выходом высокочастотного делителя часто — û и пер10

2 Г

25 гI

45 выми входами соответственно первого и второго элементов И, блок управления, руопа ВхороВ которого соединена с кодово шиной устройства, г первая и вторая гру-, пы выходов соединены с информационными входами соответственно первого и второгo программируемых делителей частоты, отличающийся тем, что, с целью повышения надежности работы, в него введены третий, четвертый, пятый, шестой и седьмой 0-триггеры, второй элемент ИЛИНЕ, первый, второй и третий элементы НЕ, первая, вторая и третья шины управления, причем первая шина управления соединена со входом первого элемента НЕ и тактовым Входом шестого 0--.ð:ããåðà, вторая шина управления соединена " тактовым входом пятого D-триггера. третья шина управления соединена с первыми входами первого и второго злеме,-.тов ИЛИ-НЕ, выход высокоЧастОтНОГО ДЕЛИтеЛЯ ЧаСтстЫ СОЕДИНЕН С тактовым входом седьмого D-триггера, инверсный выход которого соединен с первым и вторым управляющими входами высокочастотного делителp частоты. выход первого элемента HE соединен с установочными RBxozaI первого, второго и пятого 0-триггеров, выход первого программируемого делителя частоты соединен с установочным

5-входом шестого 0-триггера и через второй эломент НЕ с тактовым входом третьего

D триггера, выход второго программируемого делителя час-оты соединен с установочнь:м R-входом шестого 0-триггера и через третий элемент НЕ с тактовым входом четвертого D-триг ера, инверсный выход шестого D-триггера соедиH6H CO B70PLlM входом пер.-".Îlo элемента И, а прямой выход — с информационным входом седьмого 0-триггера v, со вторым входам второго элемента

И, третий вход которого соединен с третьим входом первого элемента И и с прямым выходом пятого D-триггера. выходы первого и второго злементо-. И соединены со счетными входами соответственно первого и второго программируемых делителей частоты, вха, ы установки которых соединены с Bblxoдам:.: -"Оответственно первого и второго элементов ИЛИ-НЕ, вторые входы которых псдключены к прямым выходам соответственно первого и второго D-триггеров, инверсные выходы которых подключены к установочным Я-входам соответственно т1зетьего и четвертого D-триггеров, а информационные входы — к прямым выходам соответственно третьего и четвертого

D-триггеров.

2. Делитель по и. 1, о т л и ч а ю щ и йс я тем, что блок управления содержит пер1691956 а выходы соответственно с первой и второй группой выходов блока управления, BblA и второй постоянные запоминающие устройства, адресные входы которых соединены с группой входов блока управления, Вьиод f

Вход 2/

Вход 2В

Вход 22

Вьиод/4

Вьиод5

Выход Q

Вйходд .

Вьиод U

Выход В

Бьиад (6

Вход V3

Вход С3

Выход 3

Вход V4

Вход С4

Выход 4

Фиг.2

Соста вител ь .Г, Кле вцова

Редактор Н. Каменская Техред M.Mîðãåíòàë Корректор M. Демчик

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 3934 Тираж Подписное ЗНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113(335, Москва, Ж-35, Раушская наб., 4/5