Устройство для приема дискретной информации

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи дискретной информации и может использоваться в синхронной и асинхронных системах передачи инфорнации. Цель изобретения - повышение помехоустойчивости. Устройство для . приема дискретной информации содержит усилитель-ограничитель 8, блок 9 автематической регулировки усиления, блок 10 фазовой автоподстройки частоты , аналого-цифровой преобразователь 11, генератор 12 поля Галуа, блок 13 быстрого преобразования Уолша, блок 14 поиска синхронизма. Цель достигается введением блоков 10 и 14. Тактовые импульсы с выхода блока 10 управляют работой преобразователя 11, генератора 12 и блока 14. Обработка информационного сигнала связана с аналого-цифровым преобразованием суммарной последовательности. Входной сигнал через блок 9 поступает на вход преобразователя 11, где преобразуется в цифровой вид. Эта операция осуществляется синхронно. Для этого коды с выходов аналого-цифрового преобразователя с тактовыми импульсами блока 10 записываются в регистр сдвига и последовательно считываются . Образованная таким образом последовательность символов обрабатывается блоком 13. 8 ил. с « (/

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19> (!1) (51)5 H 04 1. 25/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТБЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР

: И АГТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4764162/09 (22) 27 ° 11. 89 (46) 23. 11.91. Нюл. М 43 (72) В.В. Зубарев, В.П. Новиков, В.А. Светличный, Я.С. Я зловецкий и В.Д.Сысоев (53) 621. 396. 6 (088.8) (56) Авторское свидетельство СССР

N- 1501298, кл. Н 04 1. 25/0(1s 1987. (54) УСТРОИСТВО )ЦИ ПРИЕМА )g4CKPETНОЙ, ИНФОРМАЦИЦ (57) Изобретение относится к технике передачи дискретной информации и может использоваться в синхронной и асинхронных системах передачи информации. Цель изобретения - повыщение помехоустойчивости. Устройство для приема дискретной информации содержит усилитель-ограничитель 8, блок 9 автоматической регулировки усиления, блок 10 фазовой автоподстройки час2 тоты, аналого-цифровой преобразователь 11, генератор 12 поля Галуа, блок 13 быстрого преобразования Уолта блок 14 поиска синхронизма. Цель достигается введением блоков 10 и 14.

Тактовые импульсы с выхода блока 10 управляют работой преобразователя 11, генератора 12 и блока 14. Обраоотка информационного сигнала связана с аналого-цифровым преобразованием сум марной последовательности. Входной сигнал через блок 9 поступает на вход преобразователя 11; где преобразуется в цифровой вид. Эта операция осуществляется синхронно, Для этого коды с выходов аналого-цифрово го преобразователя с тактовыми импульсами блока 1() записываются в ре гистр сдвига и последовательно считываются. Образованная таким образом последовательность символов обрабатьг" вается блоком 13. 8 ил.

1693735

Изобретение относится к технике передачи дискретной информации и может использоваться в синхронной и асинхронных системах передачи инфор5 мации.

Цель изобретения — повышение помехоустойчивости.

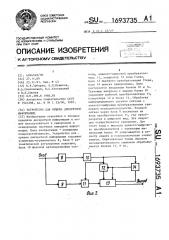

На фиг.1 изображена структурная схема передающей стороны, на фиг.2структурная электрическая схема предложенного устройства, на фиг.3 — схема блока фазовой автоподстройки частоты, на фиг.4 — схема блока аналогоцифрового преобразования; на фиг.5схема генератора поля; на фиг.6схема блока быстрого преобразования

Уолта; на фиг.7 - схема блока поиска синхронизма; на фиг.8 — временные диаграммы, поясняющие работу.

Устройство содержит на передающей стороне блок 1 памяти, блок ? записи, регистры 3 и 4 сдвига, сумматоры 5 и 6 rro модулю два, сумматор 7. УстройСтво для приема дискретной информации . содержит усилитель-ограничитель 8, блок 9 автоматической регу.пировки усиления, блок 10 фазовой автоподстройки частоты, аналого-цифровой преобразователь 11. генератор

12 поля Галуа, блок 13 быстрого пре образования Уолша, блок 14 поиска синхронизма. Блок 10 состоит из

13-триггера 15, перемножителей 16, ;17, блока 18 задержки„ реверсивного счетчика 19, сумматора 20 по модулю два, элемента H 21, задающего генера- тора 22, унравляющего элемента 23, делителя 24 и частоты, Блок 11 аналогоцифрового преобразователя состоит 40 из аналого-цифрового преобразователя

25 и регистра 26 сдвига, Генератор 12 поля Галуа состоит из триггера 27, сумматора 28 по модулю, два, регистра 29 сдвига, Блок 13 состоит<5 из счетчика 30, блока 31 элементов

ИЛИ, коммутатора 32, оперативных запоминающих устройств (ОЗУ) 33, 34 формирователя 35 управляющих сигналов, сумматора 36, коммутатора 37, решающего блока 38. Блок 14 состоит из блока 39 сравнения, делителя 40 частоты, счетчиков 41-43, КБ-тригге= ра 44, ключа 45.

Устройство работает следующим об-

55 разом.

На передающей стороне сообщение (либо разряды сообщений) записывается

4 в блок 1 памяти. Затем через блок 2 записи вводится в регистр 3 сдвига с логической обратной связью через сумматор блок 5, где преобразуется в информационную (групповую) последовательность сигналов, Информационная (групповая) последовательность (эпюра а, фиг.8) суммируется линейно (на сумматоре 7) с адресной (эпюра б, фиг.8). Соответствие фаз адресной последовательности относительно информационной устанавливается путем занесения начального кода в регистр 4 сдвига с обратной связью через сумматор..6 в момент записи- слова (разрядов слов) в регистр 3 сдвига.

На приемной стороне суммарная последовательность (эпюра в, фиг.8) поступает на вход усилителя 8 ограничителя и на вход блока 9 автоматической регулировки усиления. Клиппированный входной сигнал (эпюра д, фиг.8) с выхода усилителя-ограничителя 8 подается на входы двух перемно- жителей 16, 17. На перемножитель 17 сигнал поступает, пройдя блок 18 (эпюра е, фиг.8). На перемножителях

16, 17 происходит перемножение клиппированного входного сигнала с опор= ным. Последний формируется на ) -триггере 15 из клиппированного входного сигнала. Опорный сигнал (эпюра ж, фиг,8) имеет задержку 7 /2 относительно клиппированного входного сигнала в установившемся режиме, где 1 — дли тельность элемента входного сигнала.

Сигналы с выходов перемножителей

16 и 17 управляют режимом реверсивно го счетчика 19, на счетный вход кото рого через элемент И 21 поступает последбвательность импульсов с выхода задающего генератора 22. Разрешение на элемент И 21 подается с сумматора

20 по модулю два только в тот момент, когда на выходах перемножителей 16>

17 присутствуют сигналы разных знаков.

Эта операция тождественна операции вычитания и обеспечивает работоспособ ность реверсивного счетчика 19, который осуществляет интегрирование разности, обеспечивая таким образом формирование дискриминационной характе ристики..

В управляющем элементе 23 в зави- . симости от знака рассогласования осуществляется добавление импульсов в поступающую на вход последовательность с задающего генератора 22 или вычита1693735 ние. Тактовые импульсы <ьормируются делителем 24.

Тактовые импульсы с ныхоца блока

10 управляют работой блока 11 генератора 12 поля Галуа и блока 14 поис5 ка. Обработка информационногo (информационных) сигнала в предлагаемом устройстве связана с аналого-цифровым преобразованием суммарной последовательности. Входной сигнал (эпира в, фиг.8) через блок 9 поступает íà вход блока 11, где преобразуется в цифровой вид. Эта операция осуществляется

cHHx1 >HHo Для этОГО KopbI с Выходов анал го-цифрового преобразователя 25 с т;;товыми импульсами блока 10 записыв ются в регистр 26 сдвига и последо тельно считываются. Образованная таким образом последовательность сим- 0 волов (эпюра r, фиг,8) обрабатывается блоком 13.

Процесс выделения сообщения (сообщений) в блоке 13 заключается в приведении М-последовательности к функ- 25 ции Уолша и затем применения преобразования Уолша. Операция обеспечивается перестановками символов У-последовательности в соответствии с адресами, задаваемыми генератором 12 поля 30

Гаула, и добавлением нулевой компоненты с адресом 000, Преобразование. Уолша заключается в определении номера функции Уолша, соответствующей принятой M-последо35 вательности, из упорядоченной матрицы

Адамара. Номер функции однозначно определяет информационное содержание группового сигнала. При параллельной посимвольной передаче сообщений по 40 нескольким каналам каждый разряд номера функции несет информацию об отдельном сообщении. Если длительность

И-Последовательности (В) передаваемо-. го сигнала равна 511, то возможна передача восьми сообщений. Девятая комбинация .используется для передачи адресного сигнала. В общем виде максимальное количество и одновременно передаваемых сообщений определяется

50 из .следующих выражений и =(10@ (В+1)) -1 °

Если осуществляется передача одного сообщения скорость передачи увеличивается в и раз„

Последовательность i o слова груп

55 пового сигнала поступает на вход коммутатора 32 блока 13 ° Обработка ñëoва по алгоритму быстрого преобразования ООГ(ровожцл ется фоpMI pÎÂë)>>ГеM yп рлвляюшпх сигнллов в д>орми1>она геле 35.

Импульсbi с выхода блокл 14 устлнлвливлн>т в исходное состояние внугренний синхронизируемый генератор, чем Обеспечивается привязка вь>ходной последовательности генерлторл с частотой следования 8 Г,. (для 8=511) к фазе синхронизирующих сигналов f . На выходе формирователя 35 управляющих сигналов под воздействием синхронизированных (по словам и тактам) сигналов с выхода формирователя 35 с помощью коммутаГ ора 32 осуществляется подключение выхода блока 11 к информационному входу ОЗУ и посимвольная запись i-го слова в соответствии с адресами, задаваемыми синхронным генератором 12 поля Гаула. При поступлении i+1 слова запись осуществляется в. ОЗУ 34. В то же время производится обработка

i-ro слова, записанного в ОЗУ 33.Например, при длительности кодового слона 511 элементарных символов осуществляется девять итераций обработки, На первой итерации из ОЗУ 33 считывается символ, записанный в ячейку с адресом-000.

Адрес задается счетчиком 30. Это число хранится в коммутаторе 37. Затем считывается содержимое ячейки с адресом 256. Этот адрес формируется следующим образом. Счетчик 30 формирует число 000, которое суммируется в блоке 31 с числом 256 (с выхода блока 35), представленном в двоичном коде, Содержимое этой ячейки памяти также хранится в коммутаторе 37. С помощ>ью сумматора 36 производится операция суммирования чисел храня1 щихся в коммутаторе 37 и по сигналам формирователя 35 сумма заносится в ячейку 000 ОЗУ 33. Затем над этими же числами производится операция вычи тания и разность записывается в ячейку 256 ОЗУ 33.

На следующем такте обработки на выходе счетчика 30 формируется адрес

001. Далее повторяются описанные операции и т.д. При появлении числа 511 (в двоичном коде) нл выходе блока 31 производится установка счетчика 30 в это состояние. Установка осуществ ляется по сигналу формирователя 35.

Алгоритм обработки на первой итерацйи записывается в следующем виде: ! ооо 2 ооо осК fs7 D01 хMJ хде "Rss у щонобка счетною х х х х -x х х х х

1693735 чаще.

I 1 II l 1 II х хз8т" 256 38 51 135

-ЯО- « Х вЂ” Х Х Х .-Х Х

354 384 335

9св7.сч 317

Конец ип1ЕРаи,ии,! ц 0 сч30

00 2 ООЯ 003

Va6 001 000!

Vl!I Vlf l — Х 1

000 001 001

Одновременно с обработкой на девятой итерации решающий блок 38 де- 3р ,кодирует информацию по методу макси-! ! MàëüHîãî правдоподобия, т.е. находит

;максимальный коэффициент преобразо.вания Y è его адрес, определяющий принятый информационный символ, который поступает на информационную выходную шину блока 13., Но окойчании обработки i-го слова с помощьв коммутатора. 32 ОЗУ 33 под" ключается к выходу-блока 11 и произ- 4р водится запись i+2 слова,:а i+1 слово,. записанное в ОЗУ 34, обрабатывается по указанному алгоритму..

Приведенные операции по обработке сигналов в блоке 13 быстрого преобра 45 зования Уолша соответствуют установившемуся режиму работы заявляемого устройства. Достижение этого режима, т,.е. достижение синхронизма по тактам и словам обеспечивается блоком 14 поиска синхронизма, Коэффициент преобразования У511, соответствующий принятой адресной комбинации, но выходной адресной шине блока 13 поступает на блок 14

55 ,поиска синхронизма по слову. Коэффи циент У511а цифровом виде с выхода блока 13 б!ыстрого преобразования постулает на блок 39 сравнения (например, 1 где Х вЂ” результат обработки на пер

J вой итерации., На зторой итерации производятся аналогичные действия над символами

Х °, хранящимися в ОЗУ 33. При этом

1 формирователь 35 задает режим управления второй итерации„т.е. к адре"

О00 125 000 127 255 127 Ус!71, ->" СЧ.ЗО (I II t II

О о О 28 1 28 — 1 27 25 5 й5 5

ll где Х. — результат обработки на втод рой итерации.

На k-й итерации алгоритм управле,ния определяется следующим образом., aqpeca счетчика суммируются в блоке, К-1

l31 с числом A„=256/2 установка

1 сам, формируемым счетчиком 3О, прибавляется число 128, а установка счетчика ЗО производится в два раза

Процесс обработки на второй итерации записывается в виде: счетчика производится через ВК=512/

/2" тактов обработки.

На последней, девятой, итерации результаты БПУ (Y ) определяются д следующим образом:

y," Х"" -«У Цс!17анооиа счетчика ЗО

510 511 510

Конеи, итераи,ци

Х вЂ” Х -«!/ Конеи, оо"раоо07ки

510 511 511 микросхема 155СП1), где сравнивается с с пороговым числом, равным половине максимального значения У511. Отклики с в 1хода блока 39 сравнения воздейст вуют на счетчик 42 и при его переполнении сбрасывается счетчик 43, на который через делитель 40 частоты на 511 поступают импульсы с периодом, равным периоду адресной последова- тельности, и случайным временным положением. Наличие синхронизма определяется по состоянии RS-триггера 44.

При несовпадении временного положения адресного сигнала и импульсов синхронизации по слову, подаваемых со счетчика 43 на генератор 12 поля Гау ла и блок 13, отклики 7511 на выходе

I блока 13 либо отсутствуют, либо (при наличии прмех) имеют величину, меньшую порогового уровня, либо моменты их появления и амплитуда распределены по случайному закону. Количество импульсов (эпвра, 3, фиг.8), поступающих за фиксированный интервал времени на счетчик 42, намного меньше, чем на счетчик 43 (зпвра и, фиг.8), который, переполняясь (эпвры л, м, фиг.8), сбрасывает счетчик 42 (эпвра к, фиг.8) и устанавливает КЯ-триггер.

44 в единичное состояние. Ключ 45 открывается и разрешает поступление

1693735

Е0 импульсов с выхода счетчика 43 на вход параллельной установки делителя

40, который устанавливается в состояние, соответствующее счетчику й1. выходы которого подключены к информа5 ,ционным входам делителя 40. С приходом каждого последующего импульса состояние выходов счетчика 41 меняется на единицу и, таким образом, временное положение выходных импульсов делителя 40 и, соответственно, выходных импульсов счетчика 43, поступающих на генератор 12 поля Гаула и блок 13 быстрого преобразования, 15 сдвигается на один такт.

При совпадении временного положения адресного сигнала и импульсов синхронизации генератора 12 и блока

13 количество импульсов, поступающих на счетчик 42, увеличивается (эпюра н, фиг.8) и, так как коэффициент пересчета счетчика 42 меньше, чем у счетчика 43, то счетчик 42 сбрасывает 25 (эпюры о, п, фиг.8) счетчик 43 и устанавливает КЫ-триггер 44 .в нулевое состояние, ключ 45 закрывается и запрещает прохождение импульсов параллельной установки на делитель 40. Про3ð цесс поиска завершается.

Формула изобретения

Устройство для приема дискретной

1 информации, содержашее генератор поля

Галуа, выход которого соединен с первым входом блока быстрого преобразования Уолша, первый выход которого является выходом устройства, усилитель-ограничитель, вход которого соединен с входом блока автоматической регулировки, усиления и является; входом устройства, выход блока автоматической регулировки усиления соединен с первым входом блока аналогоцифрового преобразования, о т л и— чающее с я тем, что, с целью повышения помехоустойчивости,. введены блок фазовой автоподстройки частоты и блок поиска синхронизма, причем выход усилителя-ограничителя соединен с входом блока фазовой автоподстройки частоты, выход которого соединен с вторым входом блока аналогоцифрового преобразования и первыми входами генератора поля Галуа и блока поиска синхронизма, выход которого соединен с вторыми входами генератора поля Галуа и блока быстрого преобра-. зования Уолша, третий вход и выход - которого соединены соответственно с выходом аналого-цифрового преобразо-, вателя и вторым входом блока поиска синхронизма.

Фиг. 3

0m блока 70

0m блаха 9

От блоха 1

Om блока 1 от от

169373)

1 ао о> ьо зо >оо> ао aoai о 0>o >or оо о7 и crt

Х