Управляемый n-разрядный распределитель импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано, например, для включения цифровых индикаторов через шифратор или для формирования словесной визуальной информации на табло. Отличительной особенностью распределителя является то, что он имеет регулярную структуру с постоянным числом входов и элементов на канал. Целью изобретения является упрощение устройства. Поставленная, цель достигается за счет введения элементов И и новых связей. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (st)s G 06 F 1/10

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4378071/24 (22) 10.02.88 (46) 30;11.91. Бюл. (Ф 44 (72) Ю.Н, Цыбин и Н.В, Касперская (53) 681,3(088,8) (56) Авторское свидетельство СССР

hh 432480, кл. G 06 F 1/04, 1970.

Авторское свидетельство СССР

N. 1327084, кл. G 06 F 1/04, 1985. (54) УПРАВЛЯЕМЫЙ и-РАЗРЯДНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к вычислительной технике и может быть использовано, например, для включения сигналов цифровых индикаторов через шифратор или для формирования словесной визуальной информации на табло, Цель изобретения — упрощение распределителя.

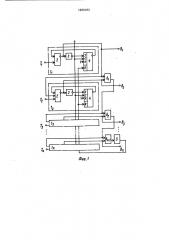

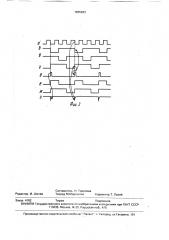

На фиг. 1 приведена структурная схема распределителя; на фиг. 2 — временные диаграммы его работы.

Устройство содержит разряды 1, каждый из которых содержит элемент И вЂ” НЕ 2, элемент Н Е 3, триггер 4, кроме того, распре. делитель содержит элемент 5 задержки, элементы И 6, входы 7 задания режима работы, выходы 8, тактовый вход 9.

Распределитель работает следующим образом.

Если на всех входах 7, задающих программу распределения, имеются сигналы логического нуля, то на выходах элементов., И вЂ” НЕ 2 каждого разряда 1i формируется потенциал логической единицы. При этом на входе элемента 5 задержки потенциал логической единицы, который, проходя через Ю 1695283 А1 (57) Изобретение относится к вычислительной технике и может быть использовано, например, для включения цифровых индикаторов через шифратор или для формирования словесной визуальной информации на табло. Отличительной особенностью распределителя является то, что он имеет регулярную структуру с постоянным числом входов и элементов на канал. Целью изобретения является упрощение устройства.

Поставленная цель достигается за счет введения элементов И и новых связей. 2 ил, элемент 5 задержки, удерживает все триггеры 4 в состоянии логической единицы по выходу.

Сигналы распределения импульсов при этом во всех каналах отсутствуют., При наличии сигнала, определяющего расширение формирования соответствующего канального импульса, на входе первого разряда 1i в виде логической единицы на информационном входе триггера 4 первого разряда 1> появляется сигнал логической единицы и соответственно на первом выходе распределителя.

При этом сигнал уровня логического нуля на выходе элемента И вЂ” НЕ 2 разряда 1> шунтирует вход элемента И-НЕ 2 последующего разряда 12 непосредственно и через . элемент И 6i положительной логики шунтирует входы всех последующих элементов И—

НЕ 2. При этом также снимается сигнал с установочных входов триггеров 4, так как на входе элемента 5 задержки сигнал принял значение уровня логического нуля. llo поступлении первого импульса по тактовому входу 9 триггер 4 первого разряда 1> срабатывает, на его выходе появляется сигнал

1695283 логического нуля, который шунтирует вход элемента И-НЕ 2 первого разряда 1 . Соответственно оканчивается формирование выходного импульса первого канала и снимается запрет со входа элемента И-НЕ 2 последующего разряда 1, При этом, если на входе второго разряда 12 имеется потенциал логической единицы, процесс включения триггера 4 второго разряда 12 повторяется аналогично и на выходе второго канала формируется импульс распределения, который через элемент И 6 шунтирует входы элементов И-НЕ 2 последующих разрядов 1з-<. И т.д, до некоторого J-го разряда 11, на входе которого имеется потенциал логического нуля, Триггер 4 этого разряда не сработает, так как на его информационном входе имеется сигнал логического нуля. Импульс в J-ом канале не появится, а сигнал с выхода элемента И вЂ” НЕ 2 заданного разряда 1 обеспечит через элемент И 6 Π— 1) разрешение для элемента И вЂ” НЕ 2 последующего разряда 1 (J + 1), И т.д, до очередного канала с потенциалом логической единицы на входе разряда 1, где процессы повторяются с фор мированием канального импульса. распре деления. После того, как срабатывают все триггеры 4 разрядов 1ь на входах которых имеется потенциал логической единицы, на выходах элементов И вЂ” НЕ 2 разрядов 1ь будет потенциал логической единицы, При этом в остальных разрядах 11 на выходе элементов И вЂ” НЕ 2 также будет потенциал логической единицы за счет наличия потенциала логического нуля на их входных шинах. Таким образом, на всех входах всех элементов И 6 будут потенциалы логической единицы, которые формируют импульс, проходящий через элемент 5 задержки и устанавливающий все триггеры 4 в исходное состояние (потенциал логической единицы по выходу). Задний. фронт этого импульса на выходе элемента И 6>-> формируется по моменту переключения в исходное состояние первого из триггеров 4 и определяется быстродействием элементной базы. Элемент 5 задержки предназ° начен для надежной установки триггеров 4 в исходное состояние из-за конечного быст5 родействия элементной базы.

Для более ясного понимания работы распределителя рассмотрим фиг, 2, где приведены для случая выполнения устройства с и = 4, логической единицей на 1, 2, 10 4-ых входах управления (вход 7) и логическом нуле на 3-ем входе управления.

Формула изобретения

)5 Управляемый и-разрядный распределитель импульсов, содержащий и IK-триггеров, и элементов И вЂ” НЕ, и элементов НЕ и элемент задержки, причем синхровходы

IK-триггеров объединены и подключены к

20 тактовому входу распределителя, первые входы элементов И-НЕ являются соответственно входами задания режима работы распределителя, выход I-го элемента И-НЕ соединен с входом I-ro элемента НЕ (l = 1, 25 ..., n) и является i-м выходом распределителя, выход 1-го элемента НЕ соединен с

1-входом I-го IK-триггера, инверсный выход которого соединен с вторым входом I-го элемента И-НЕ, входы установки в "0" всех

30 IK-триггеров объединены и подключены к выходу элемента задержки, К-входы IK-триггеров обьединены и подключены к шине нулевого потенциала распределителя, о т л ич а ю шийся тем, что, с целью упрощения, 35 в него введены и-1 элементов И, причем выход первого элемента И вЂ” НЕ соединен с первым входом первого элемента И и с третьим входом второго элемента И вЂ” НЕ. выход J-го () = 1,.... n-2) элемента И соединен с

40 первым входом (J + 1)-го элемента И и с третьим входом (J + 2)-го элемента И-НЕ„ выход (J + 1)-го элемента И-НЕ соединен с вторым входом J-го элемента И. выход и-го элемента И-НЕ соединен с вторым входом

45 (и — 1-го элемента И, выход которого соединен с входом элемента задержки, 1б95283

°

°

Фиг. f

1695283

Редактор И. Шитев

Заказ 4162 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Р д

Составитель Н, Торопова

Техред М.Моргентал Корректор Т. Палий