Пирамидальная свертка по модулю три

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и позволяет вычислять и контролировать остаток по модулю три. Цель изобретения - повышение достоверности работы устройства. Устройство содержит п ступеней свертки. Ступени с первой по (п- 1)-ю содержат сумматоры по модулю 15, обеспечивающие вычисление остатка отделения числа на 15. Этот остаток поступает на входы сумматора по модулю три n-й ступени , формирующего код остатка от деления числа на три. Элементы И и И-НЕ преобразуют код остатка к однозначному представлению. Код записывается в регистр . На втором полутакте работы устройства входной код инвертируется на сумматорах по модулю два группы и на входах регистра формируется однозначное представление кода остатка инвеосией входного кода. Узлы сравнения сравнивают значения первого и второго разрядов на входах регистра и второго и первого разрядов на его выходах. При несовпадении хотя бы одной пары сравниваемых сигналов элемент ИЛИ вырабатывает сигнал ошибки, принимаемый триггером 2 ил. w W Ј

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (э()з G 06 F 11/10

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

Il0 ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1105896 (21) 4756651/24 (22) 09,11.89 (46) 30.11.91. Бюл. М 44 (71) Одесский политехнический институт (72) А.В,Дрозд, Е.Л,Полин, О.А.Чумак и

Ю.В.Дрозд . (53) 681.3(088.8} (56) Авторское свидетельство СССР

bh 1105856, кл. G 06 Р 11/10, 1982. (54) ПИРАМИДАЛЬНАЯ СВЕРТКА ПО МОДУЛЮ ТРИ (57) Изобретение относится к вычислительной технике и позволяет вычислять и контролировать остаток по модулю три. Цель изобретения — повышение достоверности работы устройства. Устройство содержит и ступеней свертки. Ступени с первой по (и—

1)-ю содержат сумматоры по модулю 15, Изобретение относится к вычислительной технике, может быть использовано в цифровых устройствах для контроля арифметических операций и является усовершенствованием изобретения по авт. св, bk

1105896.

Известно устройство для формирования остатка по модулю три с пирамидальной сверткой, содержащее и ступеней, каждая из которых содержит "умматоры, и-я ступень свертки содержит сумматор по модулю три, информационные выходы которого являются выходами свертки, ступени свертки с первой по (и-1)-ю содержат сумматоры по модулю 15, выходы переноса каждого сумматора )-й ступени (i=1,ï) свертки соедине„„5U„„1695308 А2

i обеспечивающие вычисление остатка от деления числа на 15. Этот остаток поступает на входы сумматора по модулю три и и ступени, формирующего код остатка от деления числа на три. Элементы И и И-НЕ преобразуют код остатка к однозначному представлению. Код записывается в регистр. На втором полутакте работы устройства входной код инвертируется на сумматорах по модулю два группы и на входах регистра формируется однозначное представление кода остатка инвеосией входного кода. Узлы сравнения сравнивают значения первого и второго разрядов на входах регистра и второго и первого разрядов на его выходах. При несовпадении хотя бы одной пары сравниваемых сигналов элемент ИЛИ вырабатывает сигнал ошибки, принимаемый триггером, 2 ил. ны с входом переноса этого сумматора, входы нечетных и четных разрядов сумматоров первой ступени свертки являются входами нечетных и четных разрядов контролируе- СЭ мого числа, входы нечетных и четных раэря- Q0 дов сумматоров)-й ступени свертки (j=2,п-1) соединены соответственно с нечетными и четными входами двух смежных сумматоров (n — 1)-й ступени свертки, входы нечетных и четных разрядов сумматора по модулю три соединены соответственно с выходами нечетных и четных разрядов сумматора по модулю 15 (и-1)-й ступени.

Недостатком этого устройства является низкая достоверность его функционирования.

Целью изобретения является повыше1 ! ние достоверности функционирования уст, ройства путем обнаружения ошибок, Указанная цель достигается тем, что в устройство введены группа из Й сумматоров по модулю два (N — четное), первый и второй элементы И, элементы И вЂ” НЕ, регистр, первый и второй узлы сравнения, элемент ИЛИ и триггер, причем первые входы сумматоров по модулю два группы являются входами устройства, вторые входы объединеныы между собой, подключены к синхровходам, регистра и триггера и являются тактовым вхо, дом устройства, а выходы соединены с соот,,ветсвтующими входами сумматоров перавой ступени, входы сброса триггера и регистра объединены между собой и подключены к входу начальной установки устройства, выхо ды сумматора по модулю три подключены к первым входам первого и второго элементов И, а также к первому и второму входам элемента И вЂ” НЕ, выход которого подключен к, объединенным между собой вторым входам первого и второго элементов N, выходы которых подключены к соответствующим входам регистра, первый и второй выходы которого ! соединены соответственно с вторым и перi вым входами соответственно первого и вто,, рого узлов сравнения, первые и вторые

,входы которых подключены соответственно к выходам первого и второго элементов И, а выходы подключены к входам элемента

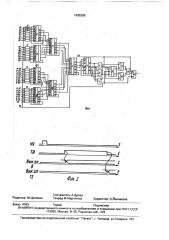

ИЛИ, выход которого соединен с информационным входом триггера, выход которого является контрольным выходом устройства, На фиг,1 приведена структурная схема устройства; на фиг.2 — временная диаграм. ма работы устройства.

Устройство содержит п ступеней, каждая из которых содержит сумматоры

13.1,13.2,...,13.N по модулю два; сумматоры

1.1, 1.2,.,1.(— — 1),1,— AQ модулю 15 flepBGA

К N ступени; сумматоры 2.1,2,2„„—. второй и ступени, сумматор 3 (п-1)-й ступени, сумматор 4-по модулю три и-й ступени, первый 5 и второй 6 элементы И, элемент И-НЕ 7, регистр 8, первый 9 и второй 1О узлы сравнения, элемент ИЛИ 11, триггер 12, причем первые входы сумматоров 13.1,132,...,(N1),13.N являются входами устройства, вторые входы объединены между собой, подключены к синхровходам регистра 8 и триггера 12 и являются тактовым входом устройства, выходы переноса каждого сумматора l-й ступени (l-1,n) свертки соединены с входом переноса сумматора первой ступени, входы нечетных и четных разрядов сумматора )=> ступени 6=2 и 1) соедин-ны

10 к соответствующим входам регистра 8, пер15 вый и второй выходы которого соединены с ние и входной N-разрядный код(И вЂ” четное), поступающий на первые входы сумматоров

35 по модулю два, группы 13 транслируются

4О

5О

55 соответственно с нечетными и четными выходами соседних сумматоров (j-1)-й ступени, входы нечетных и четНых разрядов сумматоров 4 по модулю три соединены соответственно с выходами нечетных и четных разрядов сумматора 3 (и — 1)-й ступени, а первый и второй выходы сумматора 4 по модулю три соединены с одним из входов первого 5 и второго 6 элементов И соответственно и одновременно являются входами элемента И вЂ” НЕ 7, выход которого соединен с остальными входами первого 5 и второго

6 элементов И, выходы которых подключены вторым и первым входами соответственно первого 9 и второго 10 узлов сравнения, первые и вторые входы которых подключены соответственно к выходам первого 5 и второго элементов И, а выходы подключены к входам элемента ИЛИ 11, выход которого соединен с информационным входом триггера l2, выход которого является выходом устройства.

Устройство работает следующим образом, В начале работы триггер 12 и регистр 8 устанавливаются по входу сброса в ноль сигналом, поступающим на вход начальной установки устройства. На тактовый вход устройства поступают синхроимпульсы

СИ типа "Меандр". На первом полутакте синхроимпульсы принимают нулевое значе(при нулевом значении сигнала СИ на вторых входах) и далее на входы сумматоров первой ступени без изменения, причем на входы нечетных разрядов сумматоров

1,1,1.2„...1.(— — 1 ),1,—, подаются нечетные раэN N ряды числа, на входы четных разрядов сумматоров — четные разряды числа, сигнал с выхода переноса каждого сумматора l-й ступени (i=1,ï) поступает на вход переноса этого же сумматора, в результате чего каждый из сумматоров k-й ступени (k--1,п-2) формирует на выходе свертку по модулю 15 подаваемых на его входы разрядов, С выходов нечетных и четных разрядов двух соседних сумматоров k-й ступени (К=1,п-2) поступают сигналы на входы соответственно нечетных и четных разрядов сумматоров (М+1)-й ступени, Сумматор (и-1)-й ступени 3 формирует на своем выходе свертку по модулю 15 входного числа.

С выходов нечетных и четных разрядов этого сумматора 3 сигналы поступают на входы соответственно нечетных и четных разрядов сумматора 4 по модулю три и-й ступени, который формирует на своих выхо1695308 узлах сравнения элемент ИЛИ 11 вырабаты- 40 вает нулевое значение, записываемое в триггер 12 по заднему фронту синхроимпульсов СИ, и свидетельствует о правильной работе устройства. Несовпадение сравниваемых сигналов указывает на нару- 45 шение работы устройств.

По сравнению с прототипом предлагаемое устройство позволяет обнаруживать ошибки по модулю три, что повышаетдостоверность функционирования устройства. 50

Действительно, достоверность Dn прототипа определяется вероятностью безотказной работы P,,à достоверность Р предлагаемого устройства превышает достоверность D> . практически на величину (1-Р). 55 дах код остатка от деления контролируемого числа на три, причем при делении числа на три нацело этот код может быть представлен двояко: "11" или "00", Например, код остатка "11" формируется для числа

"000"..."11", код "00" — для числа "000...00".

Чтобы код остатка при делении нацело был однозначно представлен комбинацией "00", сигналы с первого и второго выходов сумматора 4 по модулю три поступают на первые входы соответственно первого 5 и второго 6 элементов И и одновременно на входы элемента И-НЕ 7, Если остаток представлен комбинацией "11", то на выходе элемента

И-HE 7 формируется "0", в случае других возможных комбинаций: "00", "10" на выходе элемента И-НЕ 7 будет "1", .Сигнал с выхода элемента И вЂ” НЕ 7 поступает на вторые входы первого 5 и второго 6 элементов

И. Результат свертки по модулю три в однозначном представлении по переднему фронту синхросигналов СИ записывается в регистр 8. Далее на единичном значении синхросигналов СИ происходит инвертированив входного кода на сумматорах 13 по модулю два группы и вычисляется новый результат свертки по модулю три, однозначное представление которого оказывается на входах регистра 8. учитывая, что при четном номере разряда результаты свертки инвентарного значения входного кода меняются местами по сравнению с результатом свертки прямого значения входного кода, сравнение сигналов на первом и втором входах регистра 8 соответственно со значениями сигналов на втором и первом выходах регистра 8 позволяютопределить правильность функционирования устройсвта. При совпадении сигналов на первом 9 и на втором 10

Схема устройства включает в себя следующие стандартные микросхемы: в качестве сумматоров используются микросхемы

155 ИМЗ; регистр, триггер 155 ИР1, узлы сравнения 155ТМ2, элемент ИЛИ 155ЛП5, элементы И 155ЛА1, элемент И вЂ” НЕ

155ЛА11.

Формула изобретения

Пирамидальная свертка по модулю три по авт. св. М.1105896, отличающаяся тем, что, с целью повышения достоверности работы пирамидальной свертки, в нее введены группа сумматоров по модулю два, два элемента И, элемент И-НЕ, элемент ИЛИ, регистр, два узла сравнения и триггер, причем выходы результата первого и второго разрядов сумматора по модулю три соединены с первыми входами первого и второго элементов И соответственно, выходы результата первого и второго разрядов сумматора по модулю три соединены соответственно с первым и вторым входами элемента И вЂ” НЕ, выход которого соединен с вторыми входами первого и второго элементов И, выходы которых соединены с соответствующими разрядами информационного входа регистра, первый и второй разряды информационного выхода которого соединены с первыми информационными входами соответственно первого и второго узлов сравнения, выходы несравнения которых соединены с соответствующими входами элемента ИЛИ, выход которого соединен с информационным входом триггера, выход которого является контрольным выходом пирамидальной свертки, выходы первого и второго элементов И соединены с вторыми информационными входами второго и первого узлов сравнения соответственно, установочные входы регистра и триггера подключены к установочному входу пирамидальной свертки, тактовые входы регистра и триггера подключены к тактовому входу пирамидальной свертки, информациОнные входы нечетных и четных разрядов сумматоров по модулю q первой ступени пирамидальной свертки подключены к выходам соответствующих сумматоров по модулю два группы, первые информационные входы которых являются соответственно входами нечетных и четных разрядов контролируемого числа пирамидальной свертки, вторые информационные входы сумматоров по модулю два группы подключены к тактовому входу пирамидальной свертки.

1695308 и-й

Составитель А.Дрозд

Техред M.Моргентал

Корректор ЭЛончакова

Редактор М.Циткина

Заказ 4163 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5 и-6

ЯЧ7 и 1Ф

ыг н-и и-у н-о н.хн и.нн и-м и-гР

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101