Матричное вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах как программируемый специализированный периферийный процессор реального времени с параллельно-последовательной реализацией вычислений. Целью изобретения является расширение функциональных возможностей матричного вычислительного устройства за счет обеспечения возможности обработки информации в реальном масштабе времени. Поставленная цель достигается тем, что в устройство, содержащее входной регистр 2, матрицу 4 вычислительных ячеек, регистр 5 результата и элемент сравнения 8, введены блок 1 входной буферной памяти, матрица 3 запоминающих ячеек, блок 6 выходной буферной памяти, блок 9 памяти программ, блок 10 управления, блок 11 синхронизации . 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

/Ф /5

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4761997/24 (22) 25.09.89 (46) 30.11.91. Бюл. f4 44 (71) Физико-механический институт им.Г.B.Карпенко (72) А.Е.Батюк, В.В.Грицык, А.Ю.Луцык, Ю.B.Oïîòÿê, Р.М.Паленичка и О.Б.Чопко (53) 681.325(088.8) (56) Авторское свидетельство СССР

ЬЬ 1134948, кл. 6 06 F 15/31, 1985.

Авторское свидетельство СССР по заяв- i ке

М 4247605/24 — 24, кл. G 06 F 15/16, 1988. (54) МАТРИЧНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к вычислитель.ной технике и может быть использовано в

„, Я3,„, 1695319 А1 (з))s G 06 F 15/16, 15/347, 15/80 злектронных вычислительных машинах как программируемый специализированный периферийный процессор реального времени с параллельно-последовательной реализацией вычислений. Целью изобретения является расширение функциональных возможностей матричного вычислительного устройства за счет обеспечения возможности обработки информации в реальном масштабе времени. Поставленная цель достигается тем, что в устройство, содержащее входной регистр 2, матрицу 4 вычислительных ячеек, регистр 5 результата и элемент сравнения 8, введены блок 1 входной буферной памяти, матрица 3 запоминающих ячеек, блок 6 выходной буферной памяти, блок 9 памяти программ, блок 10 управления, блок 11 синхронизации. 4 ил.

aaek (л

О (Л

Ы

1695319

30

Изобретение относится к вычислительной технике и может быть использовано в электронных цифровых вычислительных машинах как программируемый специализированный периферийный процессор реального времени. с параллельно-конвейерной реализации вычислений.

Целью изобретения является расширение функциональных возможностей матричного вычислительного устройства за счет обеспечения возможности обработки информации в реальном масштабе времени.

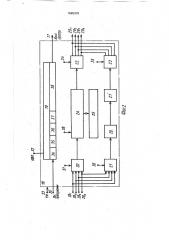

На фиг.1 изображена схема матричного вычислительного устройства; на фиг.2 — запоминающая ячейка матрицы; на фиг.3— блок управления; на фиг.4 — блок синхронизации, Матричное вычислительное устройство (фиг.1) содержит блок 1 входной буферной памяти, входной регистр 2, матрицу 3 запоминающих ячеек, матрицу 4 вычислительных ячеек, регистр 5 результата, блок 6 выходной буферной памяти, регистр 7 микрокоманд, элемент 8 сравнения, блок 9 памяти программ, блок 10 управления и блок

11 синхронизации. Кроме того, устройство содержит вход 12 данных, выход 13 данных, программно-управляющий вход 14, адресный вход 15, контрольный выход 16 и выход

17 готовности, Каждая запоминающая ячейка 18 мат. рицы 3 (фиг.2) содержит регистр 19 команд, два входных коммутатора 20, 21, два выходных коммутатора 22, 23, коммутатор 24 матрицы памяти,. матрицу 25 памяти, блок 26 управления транзитом, элемент 27 задержки, информационные входы 28>-284, информационные выходы 29 — 294, вход 30 программы, выход 31 программы, вход 32 управления вводом программы, вход 33 синхронизации. Регистр команд 19 запоминающей ячейки 18 содержит двухразрядное поле 34 адреса выхода матрицы памяти 25, двухразрядное поле 35 адреса выхода транзита, двухразрядное поле 36 адреса входа транзита, двухразрядное поле 37 адреса входа матрицы памяти 25 и восьмиразрядное поле 38 кода величины задержки.

Блок управления 10(фиг.3) содержит дешифратор 39, регистр 40, постоянную запоминающую память (ПЗУ) 41.

Блок синхронизации 11 (фиг.4) содержит генератор 42 тактовых импульсов, первый 43 и второй 44 элементы И, счетчик 45.

Устройство работает следующим образом.

Управление работой матричного вычислительного устройства осуществляется с блока 10 управления под воздействием команд, поступающих с ЭВМ по входам 14 и

15. Данные загружаются в темпе их поступления через вход 12 данных устройства в блок 1 входной буферной памяти, С адресного входа 15 устройства, подключенного к шине адреса ЭВМ, на вход дешифратора 39 приходят команды, определяющие вид информации, поступающей с программно-управляющего входа 14, подключенного к шине данных ЭВМ. Информация, поступающая на вход 14 блока управления 10, может

- быть трех видов и заносится под воэдействием сигналов, появляющихся на выходах дешифратора 39, либо в блок 9 памяти программ, либо в регистр 40 блока управления 10, либо в счетчик 45 блока синхронизации 11. В регистр 40 блока управления 10 заносятся команды, под воздействием которых ПЗУ 41 вырабатывает на управляющих выходах блока управления 10 сигналы, устанавливающие заданные режимы работы.

В счетчик 45 блока 11 синхронизации заносится число тактов синхронизации, необходимых для выполнения заданного режима. В блок 9 памяти программ заносятся программы настройки матриц 3 и 4. Установка матрицы 4, 3 в режим программиро вания (настройки) или режим обработки (вычислений) производится по сигналу с управляющего выхода блока управления 10, поступающему на вход выбора режима матрицы.

Перед началом решения задачи программа вводится в регистры команд матриц

3 и 4 иэ блока 9 памяти программ через регистр 7 микрокоманд. Хранение программй в процессе решения производится в регистрах команд ячеек матриц 3 и 4.

Последовательное соединение регистров команд ячеек в каждой строке матриц, а также последовательное соединение последнего регистра команд предыдущей строки с первым регистром команд последующей строки матриц позволяет производить запись программ в последовательном коде до полной загрузки программы в ячейки. Регистр микрокоманд 7 служит в качестве буферного регистра, преобразующего команды, принимаемые им из блока 9 памяти программ в параллельном коде, в последовательный код для записи в регистры команд ячеек, При повторном цикле записи программы в ячейки матриц 3 и 4 на элементе сравнения 8 происходит поразрядное сравнение команд, записанных в регистрах команд запоминающих и вычислительных ячеек, с повторно записываемыми командами и на выходе элемента 8, подключенного к конт1695319

15

45 рольному выходу 16 устройства формируется сигнал ошибки записи программ.

Входной поток данных поступает в параллельном коде на входной регистр 2, где преобразуется в последовательный код и порядок загружается в матрицу 3 и дальше с выходов матрицы 3 в матрицу 4. Матрица

4 предназначена для проведения вычислений, а матрица 3 служит для согласования временных интервалов, возникающих при обработке потоков информации, Каждый иэ режимов заканчивается остановкой генератора 42 под воздействием сигнала, поступающего на его вход с выхода переноса счетчика 45. После получения данного сигнала, поступающего также через соответствующий выход блока синхронизации на выход готовности 17, Э ВМ в соответствии с ее программой инициирует выполнение следующего режима.

Формула изобретения

Матричное вычислительное устройство, содержащее входной регистр, матрицу вычислительных ячеек, регистр результата, регистр микрокоманд, элемент сравнения, причем выход регистра микрокоманд соединен с первым входом элемента сравнения, выход программирования матрицы вычислительных ячеек соединен с вторым входом элемента сравнения, выход которого является контрольным выходом устройства, выход данных матрицы вычислительных ячеек соединен с входом регистра результата, о тл и ч а ю щ ее с я тем, что, с целью расширения функциональных возможностей эа счет обеспечения воэможности обработки информации в реальном масштабе времени, в него введены блок входной буферной памяти, матрица запоминающих ячеек, блок выходной буферной памяти, блок памяти программ, блок управления и блок синхронизации, причем вход данных устройства является входом блока входной буферной памяти, выход которого соединен с входом входного регистра, выход которого соединен с последовательным входом данных матрицы запоминающих ячеек, а ее параллельные выходы и входы данных соединены соответственно с параллельными входами и выходами данных матрицы вычислительных ячеек, выход регистра результата соединен с входом блока выходной буферной памяти, выход которого является выходом данных устройства, программно-управляющий вход устройства является первым входом блока управления, выходы с первого по пятый которого подключены соответственно к управляющим входам блока входной буферной памяти, матрицы запоминающих ячеек, матрицы вычислительных ячеек, блока выходной буферной памяти, блока памяти программ, а шестой и седьмой выходы блока управления подключены соответственно к первому и второму разрешающим входам блока синхронизации, первый программный выход блока управления соединен с адресным входом блока памяти программ, выход которого соединен с входом регистра микрокоманд, выход которого соединен с программным входом матрицы запоминающих ячеек, программный выход которого соединен с программным входом матрицы вычислительных ячеек, второй программный выход блока управления соединен с программным входом блока синхронизации, первый выход которого подключен к входам синхронизации блока входной буферной памяти, блока выходной буферной памяти, блока памяти программ и первым входам синхронизации входного регистра и регистра микрокоманд, второй выход блока синхронизации подключен к входам синхронизации матрицы запоминающих ячеек, матрицы вычислительных ячеек, регистра результата и вторым входам синхронизации входного регистра и регистра микрокоманд, третий выход блока синхронизации является выходом готовности устройства, адресный вход которого является вторым входом блока управления, первый выход выбора которого подключен к входу выбора блока памяти программ, а второй выход выбора подключен к одноименному входу блока синхронизации.

1695319

1695319

Цп р. 661ходь!

Tperuu

Фархад синхяРедактор М.Циткина

Корректор Э.Лончакова

Заказ 4163 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., 4/5!

0 и

nöýCairoд

Пврбы быд ора

Вюрой

npCexod, тоРОО

Вход .

АЖра

06 4и о з . 8тщ а Щ.

6ход ахаа Ф а 4

Составитель Б.Резван

Техред M.Ìîðãåíòàë

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101