Устройство для приема избыточных сигналов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (gg)s G 08 С 19/28

ГОСУДАРСТВЕ ННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4756486/24 (22) 25.09,89 (46) 30.11,91. Бюл, ¹ 44 (72) А.Г.Азаров, Ю.И.Николаев, О.П,Малофей и И,В.Чистяков (53) 621.398 (088.8) (56) Авторское свидетельство СССР

¹ 1107146, кл, G 08 С 19/28, 1984.

Авторское свидетельство СССР

¹ 1091210, кл. 6 08 С 19/28, 1984, (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ИЗБЫТОЧНЫХ СИГНАЛОВ (57) Изобретение относится к радиосвязи, а именно к приемным устройствам коротковолновой радиосвязи, и может быть использовано в системах передачи данных, Изобретение относится к радиосвязи, а именно к приемнымустройствам систем КВрадиосвязи, и может быть использовано в системах передачи данных, системах связи, системах телеуправления и телесигнализации, системах связи с подвижными обьектами, в которых для формиоования составных сигналов с избыточностью применяются помехоустойчивые коды.

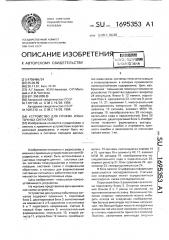

Цель изобретения — повышение помехоустойчивости устройства, На чертеже представлена функциональная схема устройства.

Устройство для приема избыточных сигналов содержит приемник 1, пороговый блок 2, двухпороговый блок 3, выполненный на элементах 4 и 5 сравнения и источниках

6 и 7 порогового напряжения, счетчик 8. первый блок памяти 9. многоканальный формирователь импульсов 10, второй регистр 11, второй блок 12 памяти, преобразо„.,5U„„ 1695353 А1 системах связи, системах телесигнализации и телеуправления, в которых применяется помехоустойчивое кодирование. Цель изобретения — повышение помехоустойчивости устройства. Устройство содержит генератор

24 импульсов, блоки 9, 12 памяти, пороговый блок 2, хронизатор 23, счетчик 8, регистры 11, 21, приемник 1, многоканальный формирователь импульсов 10, преобразователь 13 сигнала, элемент ИЛИ 18, декодер 19, преобразователь 20 последовательного кода s параллельный, блок 22 сравнения, двухпороговый блок 3. Изобретение позволяет формировать векторы многократных ошибок и опреДелять, кратность ошибки в зависимости от состояния канала связи. 1 ил, ватель 13 сигнала, состоящий из ключей 14 и 15, триггера 16 и элемента НЕ 17, элемент

ИЛИ 18, декодер 19, преобразователь последовательного кода в параллельный 20, первый регистр 21, блок сравнения 22, хронизатор 23, генератор импульсов 24.

В блок памяти 12 цифровая информация записывается последовательно. Считывание информации может осуществляться многократно, также последовательно.

Пороговый блок 3 реализован аналогично пороговому блоку 2. Опорные напряжения блоков 6 и 7 равны по величине но противоположны по знаку. Величины источников опорных напряжений можно выбирать исходя из следующих соображений.

Чем больше амплитуды пороговых напряжений, тем больше будет число m ненадежных символов той или иной номерности(отражает степень надежности принятого символа).

Поэтому, увеличивая амплитуды опорных

1695353 напряжений, увеличивают критерий надеж- аналоговым сигналом и первой разрешенности символов. Естественно, чтотакоеуве- ной кодовой комбинацией больше коэффиличение приведет к уменьшению числа циента корреляции между аналоговым наиболее надежных символов и большее сигналом и нулевой кодограммой, хранячисло символов будет отнесено к наименее 5 щейся в регистре 21. надежным. Уменьшив значение U pI, мож- и кодограммы s регистр но уменьшить число fTl, За счет этого поме- хронизатор 23 выдает сигнал на запуск гесов, которыи выдает имхоустойчивость устройства уменьшится, а нератора 24 импульсов, ко . быстродействие возрастет, пульсы на входы формирователя 10, Работает устройство для приема избы- i0 хронизатора 23 и счетчика 8. В формироваточных сигналов следующим образом. теле 10 запускается генератор линейно изВходная аналоговая комбинация двоич- меняющегося напряжения (ГЛИН), после ных символов принимается приемником 1 и чего формируется двоичная кодовая комбипоступает в блок 9. Эти же аналоговые сим- нация, в которой единичный символ наховолы поступают на входы хронизатора 23 и 15 дится в разряде с тем же номером, что и блоков 3 и 2. Хронизатор 23 начинает выда- наименьший аналоговый символ. Другие вать тактовые импульсы на управляющие разрядь. — нулевые. Эта двоичная кодовая входы пороговых блоков 2 и ", определяя комбинация в параллельном коде поступает моменты сравнения аналоговых сигналов на вход регистра 11, ГЛИН при этом остас опорными напряжениями (как правило, 20 навливается, посередине элементарных аналоговь«х Из регистра 1 и бло 12 ф

«и лака инч>ормация сигналов). Одновременно осуществляется начинает считываться одновременно по упзапись дискретной информации в блок 12 равляющим сигналам хронизатора 23. С выкодовая комои нация памяти. Выходные импульсы хронизатора хода блока 12 кодо б

23 поступают также на синхровход счетчи- 25 последовательно поступает на информацика 8, который изменяет свое состояние в онные входы ключей 14 и 15. Управляются зависимости от выходных сигналов блока ключи двоичным символом, и постугающипоступающи3. Если входной аналоговый сигнал превы- ми посчедовательн " ф

l с выхода «рормировашает один из пороговы>; уровней, то сраба- теля 10 на вход триг-е 1б, Е тывает соответствующий элементсравнения 30 триггера 18 поступает нулевой сигнал, то (одновременно они сработать не могут) и сО- открып ключ 15, Если на вход триггера посли на вход триггера постояние счетчика увеличивается на едийи- . дается едини ;íàë то ключ 15 залюч откры«вается и цу. В исходном состоянии счетчик обнулен. крывает".я а кл ю 14

Таким образом, с приходом на его вход К соответствующий информационный сигнал импульсов, отражающих число надежности 35 изменяешься на противополо>кный с посимволов(так как Uc> U/Ipp), состояние счет- мощью элемента НЕ 17. Выходные сигналы чика будет соответствовать числу надежных преобразователя 13 через элемент ИЛИ 18 . символов в кодог амме. д р ме. поступают на вход декодера 19, в котором

После записи последнего и-го двоично- отождествляются с разрешенной двоичной го элемента в блок памяти 12 начинается 40 кодовой комбинацией. Эта комбинация последовательное считывание информации последовательно записывается в преобраизбл к из него, одновременно аналоговые сигналы зователе 20, сбрасывая пре ы из лока9считываются вблок22ивформи- дограмму. Хронизатор 23 выдае рователь 10. Двоичные сигналы с выхода управляющий сигнал, и в блоке 29 снова блока 12 через открытый ключ 15 и элемент 45 вычисляются ксэфф ч ч ициенты корреляции

ИЛИ 18 (в неизменном аиде) поступают на между первой и второй разрешенными ковход декодера 19, в котором отождествля- дограммами и аналоговым сигналом, а так, и я их разность, сли разность ютсясразрешеннайдвоичнойкодавойком- же на"одится их раз о, Е бинацией, больше нуля, то выдается сигнал на управЭта комбинация, запоминается в преоб- 50 ляющие входы преобразователя 20 и региразователе 20, л, . стра 21 и кодограмма из преобразователя

В блок 22 поступает точная оценка из- 20 переписывается в регистр 21, В случае !

ыточного сигнала, считываемая из блока 9. если оазность меньше нуля, т нуля, то сигнал не

В этом блоке определяется, какая из двух выдается и вторая разрешенная кодограм комбинаций (в данном случае — первая раз- 55 ма, хранящаяся в преобразователе 20, заме решенная и нулевая) больше соответствует няется на следующую из декодера 19 на сигналу точной оценки. Управля ощий сиг- очередном такте, нал блока 22 разрешает перезапись кодог- В сл дующий момент раммы из.преобразователя 20 в регистр 21, тор 24 выдает второй импульс. Теперь н. так как коэффициент корреляции между выходе формирователя 10 будет кодогра . удет кодогрм:, 1695353 ма с двумя единичными символами в разрядах с номерами, которые соответствуют двум наименьшим аналоговым символам, и процесс, описанный выше, повторяется, С приходом импульса на первый вход храни- 5 затора 23 он начинает формировать управляющие импульсы для очередного цикла (кроме первого). Отличие первого цикла управления от последующих заключается в том, что дополнительно управляющие им- 10 пульсы подаются на входы блоков 2 и 3, на синхровход счетчика .8, на входы записи блоков 9 и 12 памяти.

Пои поступлении на вход счетчика m импульсо,;, равнь|х числу ненадежных сим- 15 волов с выхода генератора 24, счетчик обнуляется, так как коэффициент счета его равен и — числу символов в код грамме. Сигнал переноса с выхода счетгика поступает на вход хронизатора 23, который выдает сиг- 20 нал на считывание информации из регистра

21, формирует сигнал "Общий сброс", и устройство обрабатывает следующий составной сигнал с изоыточностью.

Таким образом кодовая комбинация, 25 наиболее близкая к комбинации аналоговых величин, хранящаяся в регистре 21, будет выдана получателю, Формула изобретения 30 устройство для приема избыточных сигналов, содержагцее приемник, выход которого соединен--с ийформационным входом первого блока памяти и первым входом порогового блока, причем выходы первого 35 блока памяти подключены к одноименным входам многоканального формирователя импульсов, преобразователь сигнала, первый и второй входы которого соединены соответствено с первым и вторым входами 40 элемента ИЛИ, выход которого подключен к входу декодера, выход которого соединен с информационным входом преобразователя последова гельного кода в параллельный, выход которого подключен 45 к первому входу блока сравнения, выход которого подключен к входу преобразова,еля послвдовательного кода в параллель ный, отл ича ющееся тем,что,с целью повышения помехоустойчивости, в него введены счетчик, хронизатор, генератор импульсов, двухпороговый блок, выполненный на первых и вторых элементах сравнения и источниках порагового напряжения. регистры и второй блок памяти, выходы многоканального формирователя импульсов соединены с соответствующими информационными входами первого регистра, выход которого подключен к первому входу преобразователя сигнала, выход порогового блока соединен с входом второго блока памяти, выход которого подключен к второму входу преобразователя сигнала, выходы хронизатора соединены соответственно с управляющими входами порогового блока, элементов сравнения двухпорогового блока, счетчика первого и второго блоков памяти, преобразователя последовательного кода в параллельный, декодера, первого и второrg регистров, блока сравнения и генератора импульсов, выходы первого блока памяти соединены с соответствующими первыми входами блока сравнения, первый выход первого регистра соединен с вторым входом блока сравнения., второй выход первого регистра является выходом устройства, выход приемника подключен к первому входу хронизатора и первым входам первого и второто элементов сравнения двухпорогового блока, выходы первого и второго элементов сравнения которого объединены с выходами генератора импульсов и соединены с счетным входом счетчика, упра вл я ю щам-ех мирователя им хронизатора, в д А вторым входом хронизатора. выходы первого и второго источников порогового напряжения двухпорогового блока соединены соответственно с вторыми входами первого и второго элементов сравнения двухпорогового блока, 1695353

Составитель 3. Ниэамутдинова

Техред M.Ìîðãåíòàë Корректор В. Гирняк

Редактор Н. Коляда

Производственно-издательский комбинат "Патент", r. Ужгород. уп.Гагарина, 101

Заказ 4165 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб., 4/5