Схема управления жидкокристаллическим экраном

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и предназначено для формирования сигналов кадровой развертки , строчной развертки и коммутаиии видеосигнала матричного ЖК-экрана Целью изобретения является повышение надежности устройства. Цель достигается тем, что регистры сдвига первой и второй групп содержат блоки самотестирования с соответствующими связями с другими блоками 2 ил.

союз сОВетских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (st)s G 11 С 19/18

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4680608/24 (22) 19.04.88 (46) 30.11.91, Бюл. ¹ 44 (71) Московский институт электронной техники (72) В.В,Баринов, В.А,Быков, В.Д.Вернер, В.Ф.Онацько и Н.А.Подопригора (53) 681.327.66 (088,8) (56) SAE Tech, Рар, Ser, 1985, ¹ 8, р.р.4-10, IEEE Trans, Electron Devices, 1986, ¹ 8, р.р.1218 — 1221.

Изобретение относится к цифровой вычислительной технике и предназначено для формирования сигналов кадровой развертки, строчной развертки и коммутации видеосигнала матричного ЖК-экрана.

Целью изобретения является повышение надежности устройства.

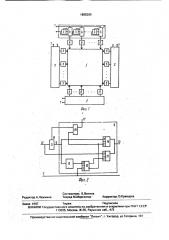

На фиг:1 и 2 представлены соответственно схема управления экраном и блоксхема одного разряда регистра сдвига с блоком самотестирования.

Схема управления ЖК-экраном содержит матричный накопитель 1 в виде запоминающей транзисторной матрицы, регистры

2 сдвига первой и второй групп, состоящие из разрядов 3, блок 4 самотестирования, формирователи 5 кадровой развертки, формирователи 6 строчной развертки, вход 7 разрешения самотестирования, одновибратор 8, первый выход 9 разряда регистра 2, RS-триггер 10, первый ключ 11, информационный вход 12 разряда 3, первый выход 13 блока тестирования, второй ключ 14, схему

„„Я „„1695390 Al (54) СХЕМА УПРАВЛЕНИЯ ЖИДКОКРИСТАЛЛИЧЕСКИМ ЭКРАНОМ (57) Изобретение относится к цифровой вычислительной технике и предназначено, для формирования сигналов кадровой развертки, строчной развертки и коммутации видеосигнала матричного ЖК-экрана.

Целью изобретения является повышение надежности устройства. Цель достигается тем, что регистры сдвига первой и второй групп содержат блоки самотестирования с соответствующими связями с другими блоками. 2 ил.

И 15, второй выход 16 разряда регистра 3, /3

1 -, второй выход 17 блока тестирования. .("

При отсутствии дефектов в разрядах 3 регистра 2 сдвига в исходном состг нии записаны "0". Подачей на i,õoä 12 в первый разряд 3 регистра 2 записывается "1". При этом уровень "1" появляется на выходе 16 разряда 3 регистра 2, активизируя соответст- (Ь вующие формирователи 5 и 6. Q

При последующих тактах подачи "1" на (Я вход 12 первого разряда регистра 3 "1" бу- () дет поочередно появляться на одном из разрядов регистра сдвига. Сканирование вертикальных и горизонтальных регистров

2 сдвига происходит с разной частотой (полное сканирование горизонтального регист-,Ф ра сдвига завершается за один такт сканирования вертикального регистра 2 сдвига, Таким образом осуществляется последовательный перебор всех элементов матричного накопителя 1.

При отсутствии блоков 4 самотестирования возможно появление дефекта залипания "0" или "1" в одном из разрядсв

1695390! . регистра 2, в результате чего последующие исправные разряды 3 регистра 2 не будут функционировать. Для исключения последствий "залипания" предназначен блок 4.

Блок 4 самотестирования работает следующим образом.

Перед началом работы схемы на вход 7 подаетс импульс положительной полярности, устанавливающий RS-триггер 10 в состояние "1". "G" с инверсного выхода

RS-триггера 10 запрещается прохождение

,информации через второй ключ 14 (последо, вательный выход 9 разряда регистра 3 отключается от входа 12 следующего разряда регистра 3) и схема И 15 устанавливается в состоя гие "0" (информация с параллельного выхода 16 р"-зряда регистра 3 не проходит на ьход формирователя 5 или 6), т.е. выход

16 разряда регистра 3 отключен от входа фсрмирователя 5 или 6). "1" с прямого выхода РБ-триггера 10 открывает первый ключ

: :;..,,подключая тем самым вход 12 разряда

; регистра 3 (т.е. выход 13 nepaoro ключа 11 предыдущего разряда) K входу 12 следующего разряда регистра 3.

После этого на вход 12 первого разряда

3 регистра 2 сдвига поступает сигнал запуска, Поскольку в блоках 4 всех разрядов 3 регистра 2 сдвига первые ключи 11 открыты, этот сигнал гаступает одновременно на входы 12 всех разрядов 3 регистра.

В том случае, если разряд 3 регистра исправен, нэ его выходе 9 тоже появляется импульс. Фронт этого импульса запускает

: одновибратор 8, который формирует им, пульс сброса, устанавливающий RS-триггер

10 в состояние "О". При этом первый ключ

11 закрывается, а второй ключ 14 открь вается, т.е. информация с последовательного выхода 9 разряда 3 регистра через второй ключ 14 поступает на вход 12 следующего разряда 3 регистра, а информация с выхода

16 разряда 3 регистра через схему И 15 поступает на вход формирователя 5 или 6.

В противном случае, т,е. если разряд 3 регистра неисправен (залипание " О" или

"1"), на выходе 9 разряда 3 регистра импульса не будет и RS-триггер 10 останется в состоянии "1". Зто означает, что как выход

9„ так и выход 16 неисправного разряда 3 регистра будут отключены от остальной схемы, а информация, приходящая на вход 12, поступает через открытый первый ключ 11 и выход 13 на вход 12 следующего разряда 3 регистра в обход данного неисправного разряда 3 регистра, 1G

Таким образом, введение блока самотестирования позволяет исключить групповые отказы при появлении одиночных дефектов, что приводит к повышению надежности устройства.

Формула изобретения

Схема управления жидкокристаллическим экраном, содержащая матричный накопитель, формирователи строчной и кадровой развертки, выходы которых соедииены соответственно с первой и второй группами адресных входов матричного накопителя, первую и вторую группы регистров сдвига, информационные входы которых являются информационными входами схемы управления жидкокристаллическимэкраном,отличающаяся тем,что, с целью повышения надежности схемы управления жидкокристаллическим экраном, регистры сдвига первой и второй групп содержат блоки самотестирования, первый, второй и третий информационные входы блока самотестирования соединены соответственно с информационным входом, первым и вторым выходами соответствующего разряда регистра сдвига, входы установки тестирования блоков самотестирования объединены и образуют вход установки тестирования схемы управления жидкокристаллическим экраном, первый и второй выходы блоков самотестирования соединены соответственно с адресными входами формирователей кадровой и строчной развертки и информационным входом следующего разряда регистра сдвига, блок самотестирования состоит из одновибратора, RS-триггера, вход сброса которого соединен с выходом одновибратора, первого и второго ключей, входы разрешения которых соединены соответственно с инверсным и прямым выходами RS-триггера, выходы первого и второго ключей объединены и образуют второй выход блока самотестирования, схему И, первый выход которой соединен с входом разрешения второго ключа, информационный вход второго ключа с.оединен с информационным входом одновибратора, второй -ход первого ключа, второй вход второго ключа, вход установки RS-триггера, второй вход и выход схемы И образуют соответственно первый, второй и третий информационные входы, вход установки тестирования и первый выход блока самотестирования.

1695390

Составитель Б,Венков

Техред М.Моргентал Корректор, О.Кравцова

Редактор А.Лежнина

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Заказ 4167 Тираж Подписное .

ВНИИОИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., 4/5