Преобразователь постоянного напряжения

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может быть использовано в системах вторичного электропитания. Цель изобретения - повышение надежности путем обеспечения защиты транзисторов от выхода из строя при возникновении неисправностей в схеме и токовых перегрузках. Параллельно транзисторам 4 и 5 включены информацией - но-согласующие элементы 21 и 22, выходы которых соединены с входами двухвходового логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 и с первыми входами 10,15четырехвходовых логических элементов И 6 и 11. Генератор 16 тактовых импульсов пэрафазными выходами соединен с вторыми входами 7, 12 четырехвходовых логических элементов И 6 и 11. Перекрестные связи между логическими элементами И б и 11 и информационно-согласующими элементами 21 и 22 обеспечивают задержку включения одного транзистора 4 (5) до момента полного выключения другого транзистора 5

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (юцэ Н 02 M 7/538

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4676397/07 (22) 11.04.89 (46) 30.11,91. Бюл, М 44 (71) Рязанский радиотехнический институт и

Научно-производственное объединение

"Старт" г. Тула (72) К.А. Абин, В.Е. Болтнев, В,В. Кандлин и

А.В. Макаров (53) 621.314.58 (088.8) (56) Авторское свидетельство СССР (Ф 1381670, кл. Н 02 М 7/537, 1984.

Патент США hh 4095128, кл. 307-254, 1978. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО

НАПРЯЖЕНИЯ (57) Изобретение относится к электротехнике и может быть использовано в системах вторичного электропитания. Цель изобретения — повышение надежности путем обеспечения защиты транзисторов от выхода из строя при возникновении неисправностей в схеме и токовых перегрузках. Параллельно,, Ж„, 1695471 А1 транзисторам 4 и 5 включены информационно-согласующие элементы 21 и 22, выходы которых соединены с входами двухвходового логического элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 20 и с первыми входами 10, 15 четырехвходовых логических элементов И 6 и 11.

Генератор 16 тактовых импульсов парафазными выходами соединен с вторыми входами 7, 12 четырехвходовых логических элементов И 6 и 11. Перекрестные связи между логическими элементами И 6 и 11 и инфо рм а цион но-согласующими элементами 21 и 22 обеспечивают задержку включения одного транзистора 4 (5) до момента полного выключения другого транзистора 5 (4). При перегрузках и входе транзистора в линейный режим вследствие роста напряжения на входе информационно-согласующего элемента 21 (22) происходит запирание обоих транзисторов с помощью двухвходовчго логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20. 4 з. и. ф-лы, 4 ил. 1695471

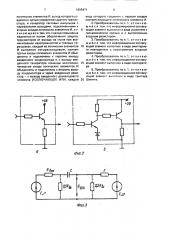

Изобретение относится к электротехнике и может быть использовано в системах вторичного электропитания, Цель изобретения — повышение надежности путем обеспечения защиты транэистОрОВ 0Т Выхода из ctpoR npu возникновении неисправностей и токовы;( перегрузках, На фиг. 1 представлена принципиальная схема предложенного инвертора; на фиг, 2 — схемы информационно-согласующих элементов; на фиг. 3-- схема замещения выходной исполнительной цепи узла защиты; на фиг, 4 — временные диаграммы работы элементов и узлов преобразователя, Преобразователь содержит трансфо1."—

I4a! ор 1 с Выходной обмот5(ой 2 и pBQRIR

Оди на ко Вы ми пОлОВи нами первичной oil" мотки,3 и два транзисторных ключа 4 и 5, Вкгноченных по известной двухтактной схеме со средней точкой, управляющие входы транзисторов 4 и 5 подключены соответстВенно к выходам логических элементов И 6 и 11 с, четырьмя Входами 7 — 10 и входами 12 — 15 соответственно, Входы 7 и 12 подключены к противофазкым выходам генератора такговых импульсов 16. Входы 8, 13 и 9, 14 попарно обьединены и подключены к выводам конденсатора 17, Точка соединения входов 8 и 13 с одним иэ Выводов конденсатора 17 соединена cвых:одом генератора 18 команды Включения, К точке соединения а (адов 9 и 14 и другого вывода конденсатора 17 подключен резистор 19, своим другим

КОНЦОМ СОЕдИНЕННь5й С ВЫХОДОМ ЛОГИЧЕСКОГо элемента 20 типа ИСКЛЮЧАЮЩЕЕ ИЛИ с двумя Входами, подключенными к Входам

10 и 15, а также к выходам двух информациОнно-согласующих элементов 21 и 22.

Информационно-согласующие элемен,ü: 21 и 22 могут быть выполнены, например, в Виде эмиттерного повторителя напряжен::; . ((Ьиг. За), либо в Виде неинвертирующеГО I. OI",aèTaëÿ напряжЕния постояннОГО тОка (фиг. Зб), либо В Виде 1(омпаратора напОЯжения или триггера Шмитта, Вход элементов 2 1 и 22 подключен параллельно транзисторным кг ючам 4 и 5.

Г1редла Гаемый преобразователь работает следующим образом, При подаче питающего напряжения на выводы 23 и 24 и отсутствии команды включения в виде потенциального уровня "1" на

Выходе генератора 18 выходные сигналы элементов 6 и 11 Определяются потенциалом "0", поэтому ключи 4 и 5 заперты и напряжения на их коллекторах равны напряжению источника питания +Е . В укаэанном состоянии выхсдные сигналы элементов 21 и 22 соответствуют уровню

НЛн

1, и, следовательно, выходной сигнал логического элемента 20 sl вляется потенциальным уровнем "0".

Конденсатор 17 в этом состоянии разря>кен, так.как потенциалы обеих его выводов одинаковы и равны потенциалам "0".

Командой на включение преобразователя является генерация единичного уровня на выходе генератора 18 (момент давки. на диаграмме фиг, 4), В момент включения (потенциалы точки соединения входов 8 и 13 и точки соединения входов 9 и 14 скачкообразно увеличиваются до уровня Е*, превышающего минимальный уровень "1". Так как в любой момент времени лишь на одном из входов 7 или 12 присутствует единичный уровень с одного из противофазных выходов генератора 16, например на входе 7 (фиг, 4), то выходной сигнал соответствующего элемента 6 в момент включения оказывается единичным, что, в свою очередь, приводит к отпиранию связанноГО с ключом

4. Отпиранн.. : ключа в силу eI o инерционности происходит в течение некоторого интервала времени тф (фиг, 4), Напряжение коллектора кг Гоча 4.уменьшается до малого значения напряжения насыщения (UxHac), а напряжение коллектора запертого в зто время ключа 5 увеличивается до значения

2ЕЯ Окнас (Фиг. 4), Так как выходной си нал элемента 21 соотг ветствует уровню "0" лишь при напряжении на коллекторе открывающегося в течение тф ключа 4 меньшем значения

UI(4 =- 1,3 — 1,6 В (в случае использования в качестве элемента 21 простого эмиттерного повторителя), то практически можно считать, что нулевой уровень на выходе элемента 21 появляется в момент

1вкл + тф на диаграмме фиг, 4. Следовательно единичный уровень на выходе логического элемента 20 появляется лишь только в момент tean. + Тф, Это обусловливает возникновение переходного процесса заряда конденсатора 17 и нарастания напряжения U9,14 в точке соединения входов 9 и 14 (схема фиг. 3).

Запуск схемы происходит лишь в том случае, когда напряжение на входах 9 и 14 соответствует единичному уровню логического сигнала, т, е, не ниже уровня +2 0 В при использовании стандартных микросхем.

Таким образом, постоянная времени цепи заряда конденсатора 17 должна быть выбрана так, чтобы Ug,14(тф) 2,0 В, Если указанное условие соблюдается, то в моМЕНТ taI(a + Тф (фИГ. 4) На ВЫХОДЕ ЛОГИЧЕСКОГО элемента 20 появляется единичный уровень, повышающий напряжение Ug,<4(t) в те)69"471 чение некоторого интервала времени до уровня Е"1", В дальнейшем при каждой смене фазы тактовых управляющих импульсов на входах 7 и 12 моменты tI, i2, ..., tl(фиг. 4 определяют начало процессов переключения ключей. Если, например, на входе 7 до момента t> был единичный уровень, а на входе

12 — нулевой уровень, то в момент с; ситуация меняется на противоположную и на выходе элемента 6 едмничный уровень меняется на нулевой и ключ 4 начинает запираться. Если транзистор 4 в Открытом состоянии насыщен, то в момент с1 начинается процесс рассасывания избыточного "àðÿäà в его базе и, следовательно, его запирание начнется 8 момент tl + tpac (фиг. 4). Так как в процессе рассасывания избыточного заряда в базе напряжение коллектора выходного транзистора CTK 4 остается на низком уровне, мало отличающемся От уровня

14вас. TO урОВЕНЬ ВЫХОДНОГО СИГНапа ЭЛЕмента 21 в течение интеРвалз tpac ОстаетсЯ нулевым и, следовательно, несмотря на единичный уровень сигнала на входе 12 выходной сигнал элемента 11 также остается нулевым и отпирания ключа 5 не происходит, Таким образом осуществляется автоматическая задержка отпирающего сигнала на входе ключа 4, что исключает одновременное нахождение ключей 4 и 5 во включенном состоянии, приводящем к протеканию крайне нежелательных сквозных токов, В процессе запирания ключа 4 напряжение на его коллекторе увеличивается в течение интервала времени сс (фиг, 4) до величины 2Е„Окнас. Из-за достаточно Высокой крутизны нарастания напряжения на запирающемся ключе 4 выходной сигнал элемента 21 практически в момент t< + tpac становится единичным, обеспечивая прохождение единичного отпирающего импульса на вход ключа 5 с входа 12.

Практическая одновременность начала формирования фронта импульса тока отпирающегося ключа и спада импульса тока запирающегося ключа в моменты времени

ti+ tpac приводит к одновременному появлению на выходах элементов 21 и 22 единичных уровней в течение интервалов времени, практически совпадающих с интервалами сф, что обусловливает наличие нулевых пауз на входе логического элемента 20. В этом случае также справедлива эквивалентная схема на фиг. 3 для определения процесса спада напряжения на входах 9 и 14. В моменты времени «+ ср + сф уровень сигнала на выходе логического элемента 20 снова становится единичным (фиг. 4) и напряжение на входах 9 и 14 снова увеличивается, трансформатора и с обьединенными эмит55 терами транзисторов, содержащий два информационно-согласующих элемента, каждый из которых входом включен параллельно одному из транзисторов, а выходом подключен к первому входу одного из двух

45 сначала скачкообразно, а затем зкспоненциально, Иэ диаграммы на фиг, 4 ясно, ло если

t» »> сф, то постоянная времени спада напряжения Ug,14(с) должна быть выбрана так, чтобы выполнялось условие Ug14(сф):= 2,0 В с целью исключения неаварийного выклю .ения преобразователя, В случае t < сф, Очевидно необходимо выполнение условия

Ug, 4(«) 2,0 В.

При возникновении неисправностей в схеме преобразователя или в силу каких-либо причин, например перегрузки, выходной транзистор может выйти из режима насы-. щения, что ведет к резкому увеличению выделяемых в транзисторе мощности потерь, его перегреву и снижению надежности работы, а во многих случаях к быстрому выходу из строя. В предлагаемом преобразователе увеличение напряжения на коллекторе Открытого ключа до некоторого заданного аварийного уровня, например, до уровня

0„, = 2,5 — 2.8 В (момент tae на диаграмме фиг. 4) фиксируется в виде появления единичного уровня на выходе соответствующего элемента 21 или 22, а так как другой из этих элементов, связанный с закрытым в это время ключом, на своем выходе также фиксирует единичный уровень, то выход логического элемента 20 переводится в нулевое состояние, в результате чего начинается спад напряжения Ug.>4(t) на входах 8 и 14. В момент с„+ ta напРЯжение Ug,>4(t) достигает уровня 0,8 В и выходные сигналы элементов

6 и 11 оказываются в нулевом состоянии и, соответственно, ранее закрытый ключ 5 остается в закрытом -,îñòîÿ нии, а ранее открытый ключ 4 запирается точно также, как и в

МОМЕНТЫ РабОЧИХ КОММУтаЦИй С|+ tpac. ТаКИМ образом, несмотря на наличие разрешающей работы команды "Включено" на выходе генератора 18 преобразователь Оказывается в выключенном состоянии, в которОм может находиться неограниченное время, Для возобновления работы преобразователя при условии устранения причин перегрузки или возникших неисправностей необходимо кратковременно снять и вновь подать команду "Включено", Формула изобретения

Преобразователь постоянного напряжения, выполненный по схеме со средней точкой первичной обмотки выходного

1695471 логических элементов И. выход которого соединен с цепью управления другого транзистора, и генератор тактовых импульсов с парафазными выходами, подключенными к вторым входам логических элементов И, о т- 5 л и ч а ю щи и с я тем, что, с целью повышения надежности путем обеспечения защиты транзисторов от выхода из строя при возникновении неисправностей и токовых перегрузках, каждый из логических элементов 1О

И выполнен четырехвходовым, причем третьи входы логических элементов И объединены и подключены к первому выводу введенного конденсатора и к выходу введенного генератора команды включения, 15 четвертые входы логических элементов И обьединены и подключены к второму выводу конденсатора и через введенный резистор —. к выходу введенного двухвходового элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, каждый 26 вход которого соединен с первым входом соответствующего логического элемента И.

2, Преобразователь по и. 1, о т л и ч а юшийся тем, что информационно-согласующий элемент выполнен в виде усилителя с гальванической связью и с высокоомным входным резистором.

3. Преобразователь по и. 1, о т л и ч а юшийся тем, что информационно-согласующий элемент выполнен в виде эмиттерного повторителя с высокоомным входным резистором.

4. Преобразователь по и. 1, о т л и ч а юшийся тем, что информационно-согласующий элемент выполнен в виде компаратора.

5. Преобразователь по и, 1, о т л и ч а юшийся тем, что информационно-согласующий элемент выполнен в виде триггера

Ш митта.! 69547 и„ и„ и„ иг.

Составитель В. Моин

Редактор Л. Пчолинская Техред М.Моргентал

"орректор О. Кравцова

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 4171 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5