Операционный усилитель

Иллюстрации

Показать всеРеферат

Изобретение относится к усилительным устройствам и может использоваться в аналоговых и аналого-цифровых системах на КМОП-транзисторах. Цель изобретения - расширение диапазона входных синфазных сигналов. Операционный усилитель содержит два входных дифференциальных каскада , соединенных параллельно и с несимметричным выходом, а также выходной каскад и блок динамического смещения выходного каскада, выполненный так, что изменение режима одного из входных дифференциальных каскадов, вызванное входным синфазным сигналом, через блок динамического смещения выходного каскада передается как компенсирующее воздействие в выходной каскад, что выражается в нулевом систематическом смещении. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ()9) (1Ц (э1)э Н 03 F 3/45

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4708518/09 (22) 21.06.89 (46) 30.11.91. Бюл. f4 44 (71) Новосибирский электротехнический институт связи им. Н.Д.Псурцева (72) А.Е.Втюрин, И.B.Ñèòíÿêîâñêèé и

Д,Л.Шлемин (53) 621.375.024(088,8) (56) Патент CliJA ЬЬ 4554515, кл. Н 03 F.З/45, опублик. 1985. (54) ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ (57) Изобретение относится к усилительным устройствам и может использоваться в аналоговых и аналого-цифровых системах на. Изобретение относится к усилительным устройствам и может использоваться в усилителях различного назначения, которые являются элементами аналоговых и аналого-цифровых систем на ЕМОП-транзисторах.

Цель изобретения — расширение диапазона входных синфазных сигналов.

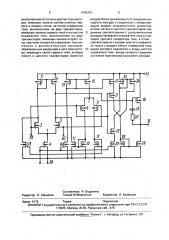

На чертеже представлена принципиальная электрическая схема операционного усилителя, Операционный усилитель содержит первый входной дифференциальный каскад

1, выполненный на первом и втором транзисторах 2 и 3, первом генераторе тока на транзисторе 4, первом отражателе тока на транзисторах 5 и 6 второй входной дифференциальный каскад 7, выполненный на третьем и четвертом транзисторах 8 и 9, втором и третьем отражателях тока на транзисторах 10- 13, втором генераторе тока на транзисторе 14, четвертом отражателе тока

КМОП-транзисторах. Цель изобретения— расширение диапазона входных синфаэных сигналов. Операционный усилитель содержит два входных дифференциальных каскада, соединенных параллельно и с. несимметричным выходом, а также выходной каскад и блок динамического смещения выходного каскада, выполненный так, что изменение режима одного из входных дифференциальных каскадов, вызванное входным синфазным сигналом, через блок динамического смещения выходного каскада передается как компенсирующее воздействие в выходной каскад, что выражается в нулевом систематическом смещении, 1 ил. с дополнительным выходом на транзисторах 15,16 и 17, выходной каскад, выполненный на транзисторе 18, цепи из последовательно соединенных конденсатора 19 и резистора 20, блок динамического смещения, выполненный на пятом и шестом транзисторах 21 и 22, пятом отражателе тока на транзисторах 23 и 24 и шестом отражателе тока на транзисторе 25 и 26, третьем генераторе тока на транзисторах 27, а также источник 28 опорного напряжения, шины 29 и 30 питания, инвертирующий и неинвертирующий входы 31 и 32 операционного усилителя.

Операционный усилитель работает следующим образом.

Предположим, что уровень синфазного входного напряжения близок к величине, равной полусумме абсолютных значений обоих питающих напряжений. В этом случае входные транзисторы обоих входных дифференциальных каскадов находятся в рабо3

1695491

40

55 чем режиме, характеризующемся функционированием на пологом участке ВАХ МОПтранзистора. Следовательно, через каждый. транзистор 5 и 6 входных дифференциальных каскадов в режиме молчания протекает ток, равный сумме половины токов, задаваемых транзисторами 4 и 1б. Допустим, что каждый из транзисторов 4 и 16 задает ток

Io. Тогда через каждый из транзисторов 5 и

6 также протекает ток Io при условии единичного коэффициента передачи тока для отражателей тока на транзисторах 10,11 и

12,13, Транзисторы 21 и 22 блока динамического смещения выходного каскада открыты. Пусть оба генератора тока блока динамического смещения выходного каскада на транзисторах 17 и 2 7 задают ток 0,5!о, обеспечивая таким образом, для транзисторов 21 и 22 режим, аналогичный рабочему режиму транзисторов 2,3 и 8,9 входных дифференциальных каскадов, Тогда через транзистор 25 протекает ток ID при условии единичного коэффициента передачи тока для отражателя тока на транзисторах 23 и

24. Следовательно, при равной крутизне по затвору для транзисторов 18 и 2б операционный усилитель имеет систематическое напряжение смещения, равное нулю, поскольку транзисторы выходного каскада смещены симметрично (Ози Опор,п 18)26 = (/Ози/ /Опор,р/)18, где U3 —.напряжение затвор-исток указанных транзисторов;

Опор,п, Опор,р — пороговые напряжения соответственно для и- и р-канальных транзисторов, Теперь предположим, что уровень входного синфазного напряжения меньше по абсолютному значению на величину, меньшую абсолютного значения порогового напряжения, абсолютной величины одного из питающих напряжений, Тогда входные транзисторы одного из входных дифференциальных каскадов закроются и ток через каждый из, например, транзисторов 5 и б в режиме молчания уменьшится вдвое. Закроется также соответственно один из транзисторов 21 и 22 блока динамического смещения выходного каскада, при этом ток через транзистор 25 также уменьшится вдвое. Следовательно, условие нулевого систематического напряжения смещения не нарушается и в этом случае не имеет значе- ния: то, к какому из входов операционного усилителя подключены затворы транзисторов 21 и 22, поскольку дифференциальное входное напряжение операционного усилителя в результате действия ООС в конкретной схеме очень мало и напряжение любого из входов можно использовать в качестве меры синфазного входного напряжения.

Введение в операционный усилитель блока динамического смещения выходного каскада позволяет получить нулевое систематическое напряжение смещения во всем диапазоне синфазных входных напряжений, что приводит к расширению входного диапазона синфазных напряжений.

Формула изобретения

Операционный усилитель, выполненный на МОП-транзисторах и содержащий первый и второй входные дифференциальные каскады, и выходной каскад, выполненный на транзисторе, имеющем канал первого типа и включенном по схеме с общим истоком, между затвором и стоком которого включена цепь из последовательно соединенных конденсатора и резистора, при этом первый входной дифференциальный каскад выполнен на первом и втором транзисторах, имеющих каналы второго типа, затворы которых являются соответственно инвертирующим и неинвертирующим входами операционного усилителя, стоки соединены соответственно с входом и выходом первого отражателя тока, выполненного на двух транзисторах, имеющих каналы первого типа, а истоки соединены и подключены к выходу первого генератора тока, выполненного на транзисторе, имеющем канал второго типа, затвор которого соединен с источником напряжения смещения, второй входной дифференциальный каскад выполнен на третьем и четвертом транзисторах, имеющих каналы первого типа, затворы которых подключены к затворам соответственно первого и второго транзисторов, стоки подключены к входам соответственно третьего и четвертого отражателей тока, выполненных каждый на двух транзисторах, имеющих каналы второго типа, и выходы которых подключены к стокам соответственно второго и первого транзисторов, а также второй и третий генераторы тока,выполненные каждый на транзисторе, имеющем канал BTOpol o типа, и затвор которого подключен к выходу источника напряжения смещения, при этом выход второго генератора тока соединен с входом четвертого отражателя тока, выполненного на двух транзисторах, имеющих каналы первого типа, выход четвертого отражателя тока соединен с истоками третьего и четвертого транзисторов, причем затвор транзистора выходного каскада соединен со стоком второго транзистора, отличающийся тем, что, с целью расширения диапазона входных синфазных сигналов, введен блок динамического смещения выходного каскаде, 1695491

Составитель И. Водяхина

Редактор Н. Швыдкая Техред M.Ìîðãåíòàë Корректор О. Кравцова

Заказ 4172 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 выполненный на пятом и шестом транзисторах, имеющих каналы соответственно первого и второго типов, на пятом отражателе тока, выполненном на двух транзисторах, имеющих каналы первого типа и на шестом 5 отражателе тока, выполненном на двух транзисторах, имеющих каналы второго типа, при этом четвертый отражатель тока выполнен с дополнительным выходом, образованным введением в него транзисто- 10 ра, имеющего канал первого типа, затворы пятого и шестого транзисторов являются входом блока динамического смещения выходного каскада и соединены с инвертирующим входом операционного усилителя, истоки пятого и шестого транзисторов соединены соответственно с дополнительным выходом четвертого отражателя тока и с выходом третьего генератора тока, а стоки— соответственно с входом шестого отражателя тока и с входом пятого отражателя тока, выход которого подключен к входу шестого отражателя тока, выход которого соединен со стоком транзистора выходного каскада,