Двоичный преобразователь код-частота

Иллюстрации

Показать всеРеферат

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано при построении частотно-цифровых приборов. Цель изобретения - расширение области применения путем обеспечения многоканального преобразователя кода в частоту. Двоичный преобразователь код - частота содержит двоичный делитель частоты, блок формирования частотных компонент, генератор эталонной частоты, m (no числу каналов ) регистров входного кода, m блоков элементов И, m элементов ИЛИ, m сглаживающих делителей частоты, селектор-мультиплексор , регистр адреса каналов, дешифратор адреса каналов, шины записи данных и адреса, шину Адрес/данные, шину выбора канала, выходные шины и выходную шину коммутируемой частоты. Поступающий по шине Адрес/данные код адреса каналов запоминается в регистре адреса. В сопровождении сигнала записи данных пропорциональный частоте входной код записывается в выбранный в соответствии с адресом регистр входного кода. Генератором эталонной частоты, делителем частоты и формирователем частотных компонент фонируется последовательность импульсов, которая поступает на входы блока элементов И, на вторые входы которых поступает преобразуемый код. Эти последовательности , объединенные элементами ИЛИ, поступают на сглаживающий делитель частоты, обеспечивающий равномерность распределения импульсов и, следовательно , высокую точность преобразования кода в частоту.1 ил. (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 М 1/86

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4622462 /24 (22) 20.12,88 (46) 30.11.91. Бюл. ¹ 44 (72) А.И.Ващенко (53) 681.325(088,8) (56) Авторское свидетельство СССР

¹ 664455228844, кл. Н 03 М 1/86, 1979.

Авторское свидетельство СССР . № 982188, кл. Н 03-M 1/86, 1981. (54)ДВОИЧНЫЙ ПРЕОБРАЗОВАТЕЛЬ КОД вЂ” ЧАСТОТА (57) Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано при построении частотно-цифровых приборов.

Цель изобретения — расширение области применения путем обеспечения многоканального преобразователя кода в частоту.

Двоичный преобразователь код — частота содержит двоичный делитель частоты, блок формирования частотных компонент, генератор эталонной частоты, m (по числу каналов) регистров входного кода, m блоков элементов И, m элементов ИЛИ, m сглажиИзобретение относится к информационно-преобразовательной и вычислительной технике и может быть использовано при построении частотно-цифровых приборов.

Цель изобретения — расширение области применения путем обеспечения многоканального преобразования кода в частоту.

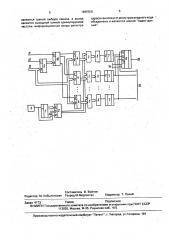

На чертеже изображено устройство, структурная схема.

Двоичный преобразователь код — частота содержит двоичный делитель 1 частоты,,. Ж,, 1695508 А1 вающих делителей частоты, селектор-мультиплексор, регистр адреса каналов, дешифратор адреса каналов, шины записи данных и адреса, шину "Адрес/данные", шину выбора канала, выходные шины и выходную шину коммутируемой частоты. Поступающий по шине "Адрес/данные" код адреса каналов запоминается в регистре адреса. В сопровождении сигнала записи данных пропорциональный частоте входной код записывается в выбранный в соответствии с адресом регистр входного кода, Генератором эталонной частоты, делителем частоты и формирователем частотных компонент фонируется последовательность импульсов, которая поступает на входы блока элементов И, на вторые входы которых поступает преобразуемый код. Эти последовательности, объединенные элементами ИЛИ, поступают на сглаживающий делитель частоты, обеспечивающий равномерность распределения импульсов и, следовательно, высокую точность преобразования кода в частоту. 1 ил, блок 2 формирования частотных компонент, выполненных на D-триггерах, генератор 3 эталонной частоты, m {по числу каналов) регистров 4 вхоДного кода, m блоков элементов И 5, m элементов ИЛИ 6, m сглаживающих делителей 7 частоты, селектор-мультиплексор 8, регистр 9 адреса каналов, дешифратор 10 адреса каналов, шину

11 записи данных, шину 12 записи адреса, шину 13 "Адрес/данные", шину 14 выбора канала, выходные шины 15 каналов, выходную шину 16 коммутируемой частоты, Преобразователь может сопрягаться с внешними устройствами с интерфейсом

МПИ или 2К, 5

Преобразователь работает следующим образом.

По шине 13 "Адрес/данные" в сопровождении сигнала на шине 12 вдешифратор

10 адреса каналов и регистр 9 адреса посту- 10 пает код адреса каналов. Регистр 9 адреса необходим для запоминания адреса до момента прихода сигнала записи данных.

Вслед за адресом по сигналу записи данных на шине 11 íà D-входы регистров 4 входного 15 кода поступает код частоты, который в дешифраторе 10 адреса каналов селектируется и записывается в выбранный по С-входу регистра 4 входного кода.

Сигнал частотой 20

Рвх= р 2 где р — вес младшего разряда входного кода 25 и и m — разрядность делителей 1 и 7 соответственно; с генератора 3 эталонной частоты поступает на двоичный делитель 1 частоты. С выходов двоичного делителя 1 частоты сформиро- ЗО ванные последовательности импульсов поступают на С-входы блока 2 формирования частотных компонент, По R-входу блока 2 импульсы последовательностей укорачиваются до длительности, равной длительности 35 импульсов эталонной частоты. Последовательности импульсовс частотами F»/2, где

k — номер разряда делителя 1 частоты, поступают на соответствующие первые входы элементов И блока 5, на вторые входы кото- 40 рых с соответствующего регистра 4 входного кода поступает код, пропорциональный частоте.

Последовательность импульсов, синтезируемая на выходе элементов ИЛИ 6, по- 45 ступает на сглаживающий делитель 7 частоты, емкость 2, где m выбирается в зависимости от заданной точности преобразования. С выхода сглаживающего делителя 7 частоты при m.-..-5 снимается 50 практически равномерная последовательность импульсов, частота которой может быть определена по формуле и

Felix = (Fex, „1Й )2 Р) 55 =о

При этом относительная погрешность распределения импульсов выходной частоты соответствует выражению

g = "г — — где m — количество разрядов в сглаживающем делителе 7 частоты.

С выходов сглаживающих делителей 7 частоты последовательность импульсов заданной частоты поступает на 0-входы селектора-мультипле .сора 8, который . позволяет на выходной шине 15 преобразователя коммутировать частоты с внешнего устройства в соответствии с кодом номера канала, подаваемым на шины 14. Селектормультиплексор 8 позволяет модулировать выходную частоту по заданному закону.

Формула изобретения

Двоичный преобразователь код — частота, содержащий двоичный делитель частоты и блок формирования частотных компонент, выполненный на блоке D-триггеров, С-входы которого соединены с соответствующими выходами двоичного делителя частоты, R-входы обьединены с входом двоичного делителя частоты и соединены с выходом генератора эталонной частоты, а 0-входы являются шиной логической единицы, первый реги"тр входного кода, первый элемент

ИЛИ, выход которого подключен к входу первого сглаживающего делителя частоты, отлича ощийся тем,что,сцелью расширения области применения путем обеспечения многоканального преобразования кода в частоту, в него введены m no числу каналов блоков элементов И, m — 1 элементов ИЛИ, m — 1 сглаживающих делителей частоты, m-1 регистров входного кода, селектор-мультиплексор, дешифратор адреса каналов и регистр адреса каналов, вход синхронизации ко-араго является шиной записи адреса, а выходы соединены с соответствующими адресными входами дешифратора адреса каналов, управляющий вход которого является шиной записи данных, а выходы подключены к входам разрешения записи m соответствующих регистров входного кода, выходы которых соответственно подключены к соответствующим первым входам блоков элементов И, вторые входы которых объединены и подключены к соответствующим выходам блока

О-триггеров, а выходы соответственно соединены с входами соответствующих элементов ИЛИ, выходы сглаживающих делителей частоты являются соответствующими выходными шинами каналов и подключены к соответствующим информационным входам селектора-мультиплексора, управляющие входы которого

1695508

Составитель В. Войтов

Редактор M. Кобылянская . Техред М.Моргентал Корректор Т. Палий

Заказ 4173 Тираж, Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 являются шиной выбора канала, а выход является выходной шиной коммутируемой частоты; информационные входы регистра адреса каналов и m регистров входного кода обьединены и являются шиной "Адрес-данные".