Устройство для контроля р-кода фибоначчи

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, может быть использовано в качестве преобразователя частично-развернутой формы Р - кода Фибоначчи в минимальную форму кода. Цель изобретения - повышение быстродействия преобразования . Устройство содержит в первом и втором каналах сумматоры 1.1 - 1.8 по модулю два, элементы И 2.1 - 2.8 n-входовые элеметы ИЛИ 3.1 - 3.2, а также контрольный сумматор 4 по модулю два, информационные входы 5.1 -5,8, выходы Ј.1 - 6.7, трехвходовый элемент ИЛИ 7, контрольный выход 8 устройства. Повышение быстродействия в два раза достигается за счет одновременного преобразования двух групп разрядов исходного кода. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!9) (3!) (я)з Н 03 M 13/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4707173/24 (22) 19.06.89 (46) 30.11.91. Бюл. ¹ 44 (71) Специальное конструкторско-технологическое бюро "Модуль" Винницкого политехнического института (72) И.В.Матюшенко, В.Г.Ваховский и

П. В, Козл юк (53) 681.3(088.8) (56) Авторское свидетельство СССР № 1608805. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ Р-КОДА

ФИБОНАЧЧИ (57) Изобретение относится к вычислительной технике, может быть использовано в качестве преобразователя частично-развернутой формы Р— кода Фибоначчи в минимальную форму кода. Цель изобретения— повышение быстродействия преобразования. Устройство содержит в первом и втором каналах сумматоры 1.1 — 1.8 по модулю два, элементы И 2.1 — 2.8 и-входовые элеметы ИЛИ 3.1 — 3,2. а также контрольный сумматор 4 по модулю два, информационные входы 5;1 — 5,8, выходы 6,1 — 6.7, трехвходовый элемент ИЛИ 7, контрольный выход 8 устройства. Повышение быстродействия в два раза достигается за счет одновременного преобразования двух групп разрядов исходного кода. 1 ил.

Составитель А.Тимофеев

Редактор М, Кобылянская Техред М.Моргентал Корректор T. Палий

Заказ 4173 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Изобретение относится к вычислительной технике и может быть использовано для ускоренного преобразования частично развернутой формы Р = 1 кода Фибоначчи в минимальную форму при одновременном 5 контроле исходного кода на соответствие признакам частично развернутой формы

P = 1 кода Фибоначчи.

Цель изобретения — повышение быстродействия преобразования, 10

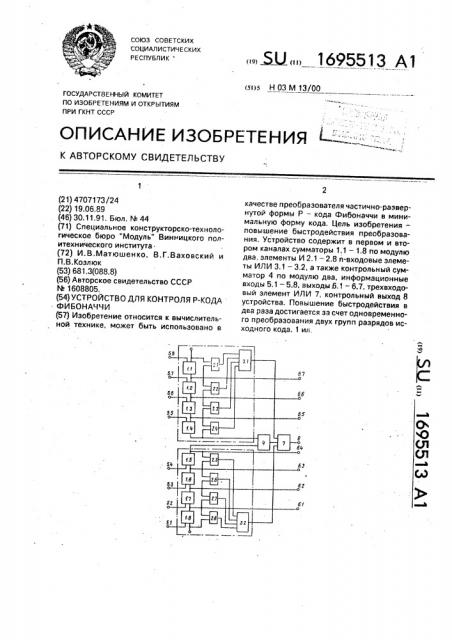

На чертеже изображена структурная схема устройства для контроля 8-разрядного P-кода Фибоначчи.

В устройстве используются следующие позиции: в первом и втором каналах — сум- 15 ,маторы 1,1 — 1,8 по модулю два, элементы И

2,1 — 2.8, и-входовые элементы ИЛИ 3.1—

3,2, а также контрольный сумматор 4 по модулю два, информационные входы 5,1—

5,8, выходы б,1 — 6,7, трехвходовый элемент 20

ИЛИ 7, контрольный выход 8 устройства.

Принцип работы предлагаемого технического решения в функции преобразова ния кода основан на инвариантности результата к направлению свертки по моду- 25 лю два исходного кода от младших разрядов к старшим или наоборот. Отличие лишь в том, что полученные коды сдвинуты один относительно другого на один разряд, Пример 1.01101111001100 30

- —:-0100101 0001000

О О 1 001 О 1 0001 00 -Поэтому, разделив исходный код пополам, осуществив встречнук> свертку по модулю два всего кода, исключив старший 35 разряд результата свертки, например, со старших разрядов, получим преобразование всего кода в два раза быстрее по сравнению с основным техническим решением.

Пример 2, 01101111001100 40

-o> oo > вЩ ) q < оПоскольку код делится пополам, то только одна группа рядом стоящих единиц в исходном коде не будет охвачена контро- 45 лем. Ее контроль при отсутствии ошибок в других группах осуществляется по признаку четности числа единиц всего кода, Формула изобретения

Устройство для контроля P-кода Фибо- 50 наччи, содержащее первый канал из и сумматоров по модулю два. и элементов И, ивходовый элемент ИЛИ, причем в первом канале входы разрядов информационного входа устройства соединены с первыми входами соответствующих сумматоров по модулю два, второй вход i-ro (I = 1 - n) сумматора по модулю два соединен с пер= вым входом l-ro элемента И, второй вход которого соединен с выходом i-ro сумматора по модулю два и вторым входом (! + 1)-го сумматора по модулю два, выход i-го элемента И подключен к 1-му входу и-входового элемента ИЛИ, второй вход первого сумматора по модулю два является первым входом расширения устройства, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия преобразования, в него введены второй канал из и сумматоров по модулю два, п элементов И, и-входовый элемент ИЛИ, а также контрольный сумматор по модулю два, трехвходовый элемент ИЛИ, причем во втором канале входы разрядов информационного входа устройства соединены с первыми входами соответствующих сумматоров по модулю два, второй вход l-ro (i = 1- n) сумматора по модулю два соединен с первым входом l-го элемента И, второй вход которого соединен с выходом i-го сумматора по модулю два и вторым входом (i + 1)-го сумматора по модулю два, выход i-го элемента И подключен к 1-му входу и-входового элемента ИЛИ, второй вход первого сумматора по модулю два является вторым входом расширения устройства для контроля, выход трехвходового элемента ИЛИ является контрольным выходом устройства, первый и второй входы трехвходового элемента ИЛИ соединены с контрольными выходами и- входовых элементов ИЛИ первого и второго каналов соответственно, а третий вход — с выходом контрольного сумматора по модулю два, первый и второй входы которого соединены соответственно с первым и вторым выходами расширения устройства, выходы сумматоров по модулю два первого и второго каналов являются выходами соответствующих разрядов информационного выхода устройства .