Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике, предназначено для использования в универсальных и специализированных цифровых вычислительных устройствах и является усовершенствованием устройства по а.с, № 1117635. Цель изобретения-повышение достоверности функционирования вычислительного устройства . Вычислительное устройство содержит матрицу вычислительных ячеек, параллельный сумматор, группу ячеек памяти, группу узлов сравнения, блок контроля, матрицу 6 ячеек памяти, входы множимого устройства, прямой и инверсный множителя устройства соответственно, входы первого и второго слагаемых устройства соответственно, тактирующий вход и выход результата устройства , группу выходов неисправности множителя устройства, выход неисправности работы устройтсва, установочный вход устройства. В устройстве осуществляется контроль множителя путем сравнения на неравнозначность прямого и инверсного значений его разрядов Контроль работы устройства осуществляется путем сравнения двух результатов вычисления: прямого кода множимого и слагаемых и кода множимого и слагаемых, сдвинутых на два разряда влево. 8 ил. сл С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

Р РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ (si)s 6 06 F 7/52

ГОСУДАР CTSE ННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (61) 1117635

{21) 4701016/24 (22) 05.05.89 (46) 07.12,91. Бюл. №45 (71) Харьковский автомобильно-дорожный институт им. комсомола Украины

{72) В.В,Шатилло, С:Н,Прохоров, Л.С.Явиц, В.В.Пономарев и О,А.Четверикова (53) 681.3(088.8) (56) Авторское свидетельство СССР

¹ 1117635, кл, 6 06 Р 7/52, 1983. (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

{57) Изобретение относится к цифровой вычислительной технике, предназначено для использования в универсальных и специализированных цифровых вычислительных .устройствах и является усовершенствованием устройства по а.с. ¹ 1117635. Цель изобретения — повышение достоверности функционирования вычислительного устройИзобретение относится к цифровой вычислительной технике, предназначено для использования в универсальных и специализированных цифровых вычислительных устройствах и является усовершенствовани-: ем устройства по авт. св, N 1117635, Цел ь изобретен ия — повышение достоверности функционирования вычислительного устройства.

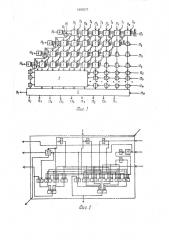

На фиг.1 приведена функциональная схема вычислительного устройства для случая m=6 и n=4 (m — разрядность множимого, n —; на фиг.2 — функциональная схема вычислительной ячейки матрицы; на фиг,3 — функциональная схема

„„5U„„1697077 А2 ства. В ы числ ител ьнсе устройство содержит матрицу вычислительных ячеек, параллельный сумматор, группу ячеек памяти, группу узлов сравнения. блок контроля, матрицу 6 ячеек памяти, входы множимого устройства, прямой и инверснь.й множителя устройства соответственно, входы первого и второго слагаемых устройства соответственно, тактирующий вход и выход результата устройства, группу выходов неисправности множителя устройства, выход неисправности работы устройтсва, установочный вход устройства. В устройстве осуществляется контроль множителя путем сравнения HG неравнозначность прямого и инверсного значений его разрядов. Контроль работы устройства осуществляется путем сравнения двух результатов вычисления: прямого кода множимого и слагаемых и кода множимого и слагаемых, сдвинутых на два разряда влево. 8 ил. ячейки памяти; на фиг.4,5 — функциональные схемы узла сравнения группы и параллельного сумматора соответственно: на фиг.6, 7 — функциональные схемы одноразрядного сумматора и блока контроля соответственно; на фиг.8 — временная диаграмма подачи тактирующих сигналов устройства.

Функциональная схема вычислительного устройств, приведенная на фиг.1, содержит матрицу 1 вычислительных ячеек, параллельный сумматор 2, группу ячеек 3 памяти, групу узлов 4 сравнения, блок 5 контроля, матрицу 6 ячеек памяти, вход 7 множимого устройства, прямой и инверс1697077 ный входы 8, 9 множителя устройства сооТветственно, входы 10, 11 первого и второго слагаемых устройства соответственно, TB„тирующий вход 12 и выход 13 результа,а устройства, группу выходов 14 неисправности множителя устройсгва, выход 15 неис1равности работы устройства, установочный вход 16 устройства, Вычислительная ячейка матриць1 1. изображснная на фиг,"., Содержит элеме,;, ы l- Е

17-21, элемент 22 задержки, я-1ейку 23 памяти, B IGMGHTbl И 23 — 34, элем<".Нть1 И.Г1И 35, 36.

Ячейка 3 памяти групгы, изображенная на фиг.3, содержит элемент 37 задер>к;<и, элемент HF 38, элементы И 39 — 41 и элемент

Nfl Ir1 42, Узел 4 сравнения группы, изобра>кенныи на фиг.4, содержит элемент 43 заде.. жки, элементы HE 44-46, элементы И 47-51, элемент И.1! И 52.

Параллельный сумматср 2, изображенHblA на фиг,5, содержит ячейки 53 памятr! и группу одноразрядных сумматоров 54, Одноразрядный сумматор 54 групгь„ изображенный на фиг,б„содержиг элемент

55 задержки, элемент НЕ 56-59, элементы

И 60-68, элементы ИП1/I 69, 70.

Блок 5 контроля, изображе;— ный на фиг,7, содержит триггер 71, компаратор 72., гр ппу ячеек памяти 73, элементы задержки группы 74, элементы 75, 7г., элемент И 77, Вычисг1ительное устройство оеализует функцию

S-А+ В D+ С, Для вычлсления пролзведения чисел В и

D слагаемые А и С должны бь1ть нулевыми.

Вычислительное устройство работает следующим образом, В исхОднОм сОстОЯнии на такти ующий вхоп, l2 устройства посту.ает нулевой сигнал, Процесс вычисления начинается с ггодачи на входы 7о-7з, 8p — 8з, 9о--9з, 10о-10з, 11о-11з устройстьа первых сомножитегсй

01 и  l, инвертирован ноге множителя B l, а также слагаемых А1 и С1. I-, a входы 71-75, 114 115 пОЦаетсЯ нулеВой сигнал, на усТВНОвочный вход 16 устройстьа — единичный сигнаг1, В течение Времени Тр (фиг.8) происходят вычисление в ячейках первой строки матрицы 1 и проверка прямого и инвертированного младшего разряда множителя Вр на неравнозначность. В случае неисправности шины множителя с выхода

141 группы устройства снимается единичный сигнал, при исправной шине — нулевой.

В момент времени Тя, ко-да вычисления в первой строке матрицы 1 заканчиваются, на тактирующий вход 121 устройства подается единичный сигнал, которь и запоминает информацию, установившу1ося на выходах ячеек матрицы 1 первой строки. При этом на выхОдах ГiGpGHocB я -1сек первой стооки мат"

Оицы 1 ус анавливается сооTBGTcTBóþùèé

5 разряд множимого В1. Си .нал "" на входе

121 устройств заг1ре<цает также обрабо- ку ячейками первой строки матрицы 1 сигналОВ с, вхоДОВ 7"; — 75, 85-9о, 10о — 10, 11о — 11

Единичный;. Игнал нг1 вх де ",61 устройства :0 сохраняется в течение времени Тп (фиг,8), обеспечивает правильное проведение выЧИ ЛЕ лИй - г Втврпй РОКЕ МатоицЫ 1 И Заи :1 мин а ни» сиГнала в ячей "<е памяти ВтороГО ряда Гоуппы 3, 11 5 Время, IloI:а В первом ряду ма оицы 1 не

ПРОИЗВОДИ,СЯ ВЫЧИСЛЕНИЙ, ИСПОЛЬЗУЕТСЯ для поцачи на Входь1, <- -7-, 10 ????” 105 11 1 1?? ??????????????????; ??????>кимого Й1 и слагаемых /À, CI, сдвинуть хтаким образом на два разряда

20 влево прием на входы 7о и 7l 10о и ":01, 11о и 11, устройст .а подаются нулевые сигнал ь!, на вхо Ц 1 6 устрсйстВа также пОДаетсЯ нулевой сигнал. Через время 2Тр на в: од 12:> устройства подается единичнь .й сигнал, ко25 торый запоминает информацлю В ячейках второго ряда матриць 1 и в ячейках 3 памяти второго ряда группы и запрещает обработку ин рОрмации B этих ячейках.

С момента време: H 2Òp Вычисление

30 продол I

Поскольку первый ряд ячеек л гтрицы 1

--еперь готов к работе, на ВХОД 121 устройства в момент времени Т1>+Тп Г1одается сигнал "0", который разрешает обработку

35 вновь поступив, .Gé информации ячейками рядэ матрицы ", Сигнал этот устанавливаетсл на вРВ::.Я т+Тр, что Обеспечивает пРаВиль IOG Вы 1ислен1 е (т — задержка в элементе ИЕ и элем нте задержки!, 40 К моменту Bpемени 2Тр+Тр+ < зычисление B первом ряду матрицы, заканчивается и начинае1ся вь;исление Ви Второл1 ее ряду. Далее — вычисление в третьей строке матриць1.

45 Аналогич:->о конвейерный процесс прсдолжается дал. ше. Ilo леое o;OH :àHèÿ Bb,числений в К-й ступени (1 .=- К 5) устройства в нее Вводится новая информация, Управление работой ступенел устрой50 стьа ос ществляетсг сигналами тактового входа 12 jcTpolrlcTBB, !

При этом В Г1ервый пог1упериОД рабОты I lpoисходит с поямь1ми, а ВО Втооом со сдвинутыми на два разряда влево операндами.

55 Одновременно с Bbl÷ècëçblèÿìL1 Bo BcGx cTv" пеняхустройства происходит проверка пряМОГО и инверснОГО значений разрядОВ множителя на неравнозначность с помощью узлов 4 сравнения гр гп1..Ы.

",697077

10 устройство введены группа узлов сравнения 15

В блоке 5 контроля результат вычисления с прямыми операндами сравнивается с результатом вычисления со сдвинутыми операндами. При несравнении формируется единичный сигнал на выходе 15 неисправности работы устройства.

Результат вычислений поступает на выход 13 результата устройства.

Формула изобретения

Вычислительное устройство по авт. св, И. 1117635, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности функционирования, в матрицу вычислительнь;х ячеек введены и+ 1-й и и+2-й столбцы, в блок контроля, матрица ячеек памяти размерности (n+1).m и @+1-я группа ячеек памяти, параллельный сумматор содер>кит группу одноразрядных сумматоров и и+2 группы ячеек памяти, ричем выход элемен.та ИЛИ каждой ячейки памяти m-й группы соединен с первым входом первого элемента И соответствующей ячейки памяти первой строки матрицы, в матрице ячеек памяти первый вход первого элемента И каждой ячейки памяти любой строки, кроме первой, соединен с выходом элемента ИЛИ соответствующей ячейки памяти предыдущей строки, вторые входы вторых элементов И ячеек памяти каждой строки матрицы соединены с соответствующим тактирующим входом устройства, выходы первых v. вторых элементов ИЛИ m+1-й и m+2-й вычислительных ячеек m-й строки матрицы соединены с соответствующими весовыми входами первого и второго слагаемых паралельного сумматора, входы четвертого элемента НЕ m+1-й и m+2-й вычислительных ячеек первой строки матрицы соединены с соответствующими разрядными входами множимого устройства, входы первого и второго элементов НЕ а+1-й и m+2-й вычислительной ячеек первой строки матрицы соединены с соответствующими разрядными входами первого и второго слагаемых устройства соответственно, выход элемента

ИЛИ каждой р-й ячейки памяти m+1-й группы (1 < р « m + и + 1) соединен с первым входом первого элемента И р+1-й ячейки памяти m+1-й группы, вторые входы вторых элементов И каждой ячейки памяти m+1-й группы подключены к соответствующему тактирующему входу устройства, выходы элементов ИЛИ ячеек памяти последней строки матрицы, выход результата параллельного сумматора и выход элемента ИЛИ последней ячейки памяти m+1-й группы соединены соответствующими информационными входами блока контроля, информационный выход которого является

55 выходом результата устройства. выходы неисправности блока контроля являются выходами неисправности результата устройства, первый информационный вход каждого i-го узла сравнения группы подключен к прямому входу i-го разряда множителя устройства (1 < I m), второй информационный вход каждого i-го узла сравнения группы подключен к инверсному входу 1-го разряда множителя устройства, ",àê-,овый вход каждого i-го узла сравнения группы подключен к (-му тактирующему входу устройства, выходы сравнения узлов сравнения группы образут группу выходов неисправности множителя устройства, ",ервый вход первого элемента И первой ячейки памяти m+1-й группы подключен к ,становочному входу устройства, в параллельном сумматоре вход первого слагаемого первого одноразрядного сумматора группы и первые входы первых элементов И нечетных ячеек памяти группы образуют вход первого слагаемого параллельного сумматора, вход второго слагаемого первого одноразрядного сумматора группы и первые входы первых элементов И четных ячеек памяти первой группы образуют вход второго слагаемого сум 4атора, выход элемента

ИЛИ каждой Ы-й:.-чейки памяти Т-й группы (I < M < — 1; 2 <Т S< и + 1) соединен с первь:м входом первого элемента И М-й ячейки памяти Т+2-й группы, выходы элементов ИЛИ каждой R-й и R+1-й ячеек памяти Я-й группы(1 = К < П+ 1) соединены соответственно с входами первого и второго слагаемых R+ I-го одноразрядного сумматора группы, выход элемента ИЛИ каждой

Q-и ячейки памяти 1-й группы (+ 2 < Q 1 < I < и ) соединен с первым входом Q-1-й ячейки памяти !+1-й группы, выход результата каждого R-го одноразрядного сумматора группы соединен с первым входом первого элемента И R-й ячейки памяти

R+1-й группы, выход переноса каждого R-ro одноразрядного сумматора группы соединен с входом переноса R+1-го одноразрядного сумматора группы, вторые входы второго элемента И ячеек памяти N-й строки и тактовый вход N-co одноразрядного сумматора группы (1 < К < и + 2) подключены к N+m-vyxa;a ирующему входу устройства, вход переноса первого и вход второго слагаемого последнего одноразрядных суммато- . ров группы подключены к шине нулевого потенциала устройства, выходы элементов

ИЛИ я-;век памяти последней группы и выход переноса последнего одноразрядного сумматора группы образуют выход результата параллельного сумматора. 1697077

"/ И, 4 1/„ 11, Я

Q5 6

Ь

/3 15 13 15 1,>

160707"/

У8, 1697077

- >- Ао

1697077!

51 150

ПИочп

ЖФ г г

g2i

/22

2fQ

l2ri

Составитель В.Гречнев

Редактор Т.Федотов Техред МЛоргентал Корректор М.Кучерявая

Заказ 4306 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Подача l7одача Di 2г, D>,Âi,ÿ,С Si,4> 2г, С Я! 2 7 6 0 6

Й г.

Плача Э: 2>

Вг,яг.;, Сг Р