Устройство обмена данными

Иллюстрации

Показать всеРеферат

Изобретение от носится к вычислительной технике и может быть использовано для построения высокопроизводительных процессоров или систем с максимальной организацией . Цель изобретения - расширение функциональных возможностей за счет организации обмена информацией, подлежащей обмену по одинаковым адресам. Поставленная цель достигается тем, что устройство обмена данными содержит блок 1 дешифрации номера регистра, блок 2 регистров , блок 3 вывода информации, формирователь 4 управляющих сигналов, счетчик 5 адреса, узел 6 регистровой памяти, элемент ИЛИ 7, шифраторЭ, регистр 10, дешифратор 11, элемент И 12, регистры 131-13к, многовходовый коммутатор 14, шину 15 адреса, шину 16 данных, шину 17 управления, выход 18, вторые адресные входы 19, вход 20 установки в нулевое состояние, центральный процессор 21, вспомогательный процессор 22, вход 23 начальной установки.2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я>ю G 06 F 15/16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1325497 (21) 4724836/24 (22) 28.07,89 (46) 07.12.91. Бюл. ¹ 45 (72) Е.Я.Ваврук, Ю.В,Галкин и Л,В.Чиркова (53) 681. 3(088. 8) (56) Авторское свидетельство СССР

¹ 1325497, кл, G 06 F 15/16, 1986. (54) УСТРОЙСТВО ОБМЕНА ДАННЫМИ

{57) Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных процессоров или систем с максимальной организацией. Цель изобретения - расширение функциональных возможностей за счет организации обмена информацией, подлежа„„5U 1697083 А2 щей обмену по одинаковым адресам. Поставленная цель достигается тем, что устройство обмена данными содержит блок 1 дешифрации номера регистра, блок 2 perucTpos, блок 3 вывода информации, формирователь 4 управляющих сигналов, счетчик 5 адреса, узел 6 регистровой памяти, элемент

ИЛИ 7, шифратор 9, регистр 10, дешифратор

11, элемент И 12, регистры 13> — 13к, многовходовый коммутатор 14, шину 15 адреса, шину 16 данных, шину 17 управления, выход 18, вторые адресные входы 19, вход 20 установки в нулевое состояние, центральный процессор 21, вспомогательный процессор 22, вход 23 начальной установки. 2 ил, 1697083

Изобретение относится к вычислительной технике, может быть использовано для построения высокопроизводительных процессоров или систем с максимальной органиэацией и является усовершенствованием устройства по основному авт.св.

N 1325497.

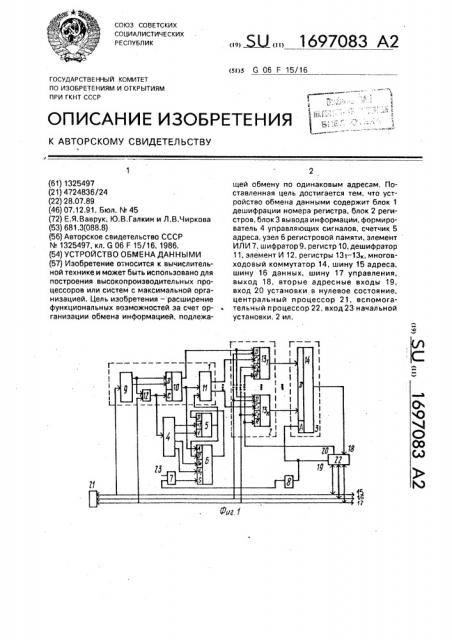

Цель изобретения — расширение функциональных возможностей за счет организации обмена информацией, подлежащей обмену по одинаковым адресам, На фиг.1 приведена функциональная схема устройства; на фиг,2 — временная диаграмма работы формирователя управляющих сигналов.

Устройство содержит блок 1 дешифрации номера регистра, блок 2 регистров, блок

3 вывода информации, формирователь 4 управляющих сигналов, счетчик 5 адреса, узел

6 регистровой памяти, элемент ИЛИ 7 и дешифратор 8, Блок 1 дешифрации номера регистра содержит шифратор 9, регистр 10, дешифратор 11 и элемент И 12.

Блок 2 регистров содержит регистры

131 — 13 к.

Блок 3 вывода информации содержит многовходовый коммутатор 14.

Кроме того, обозначены шина 15 адреса, шина 16 данных, шина 17.управления, выход 18, вторые адресные входы 19, вход

20 установки в нулевое состояние, центральный процессор 21, вспомогательный процессор 22 и вход 23 начальной установк л.

Устройство работает следующим образом.

По аигналу начальной установки регистры узла 6 регистровой памяти устанавливаются в единичное состояние. По сигналу на вход 20 регистры 13 устанавливаются в нулевое состояние, Центральный процессор

21 управляет работой системы: осуществляет сегментацию памяти, вычисляет адреса операндов, сами операции и т.д.

Вспомогательный процессор 22 является специализированным и выполняет математические операции. При работе системы на шине 15 адреса находится адрес, на шине

16 — данные, по шине 17 формируются сигналы управления, Каждый адрес, по которому формируется информация для процессора 22, распознается шифратором

9, и, если операнд "принадлежит" процессору 22, на первом выходе идентификации шифратора 9 появляется сигнал единичного уровня. На информационных выходах шифратора 9 формируется код номера операнда для записи в блок 2 регистров. Запись ин50

5

45 формации с выходов шифратора 9 в регистр

10 происходит по сигналу стробирования адреса, поступающего на вход стробирования адреса через шину 17, при наличии единичного сигнала признака идентификации (с выхода элемента И 12). Одновременно, сигнал единичного уровня с выхода элемента И 12 запускает формирователь 4 управляющих импульсов. В начальный момент времени и при первоМ считывании каждого из регистров узла 6 регистровой памяти, на вход счетчика 5 поступают все сигналы единичного уровня("111...11"), увеличение которых на+1 формирует на выходе счетчика 5 значение "000...00", тем самым формируя на выходе дешифратора 11 сигнал выборки первого регистра определенной группы регистров блока 2 регистров.

По сигналу на входе стробирования данных, поступающему по шине 17, информация, поступающая через шину 16, записывается в соответствующий регистр

13ь Одновременно. в регистр 13 записывается и признак идентификации. При

"распознавании" следующего адреса происходит увеличение содержимого счетчика адреса на + 1 относительно информации, записанной в соответствующий регистр узла 6.

После подготовки данных процессор 21 . передает управление вспомогательному процессору 22. Получив управление, процессор 22 начинает выполнять заданную подпрограмму и считывает данные из регистров 13, открывая коммутатор 14 по определенным входам на выход устройства.

Одновременно с информацией из регистров

13 считывается признак идентификации, указывающий, что в соответствующий регистр 13 записана информация. Одновременно со считыванием информации информация по вторым адресным входам поступает на вход дешифратора 8, который

Яастроен так, что при выполнении любой программы процессором 22 на его выходе формируется сигнал единичного уровня, который через элемент ИЛИ 7 устанавливает регистры узла 6 регистровой памяти в единичное состояние, подготавливая устройство к приему новых данных для процессора

22. После считывания всей информации процессор 22 формирует сигнал на входе 20. по которому все регистры 13 устанавливаются в нулевое состояние, После окончания выполнения подпрограммы процессор 22 выдает сообщение процессору 21 об окончании работы и считывание результата происходит через шины

15-17.

1697083

Формула изобретения

zvum

hem йм

Счгп нюй

fbix

Юь ход

3ппиШ

Составитель А.Астапов

Техред М.Моргентал КоРРектоР Т.Малец

Редактор И.Шмакова

Заказ 4307 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Устройство обмена данными по авт.св.

М 1325497, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет организации обмена информацией, подлежащей обмену по одинаковым адресам, в него введены формирователь управляющих сигналов, счетчик адреса, узел регистровой памяти, дешифратор, элемент ИЛИ, причем первый выход блока дешифрации номера регистра соединен с входом формирователя управляющих сигналов, первый и второй выходы которого соединены соответственно со счетным и установочным входами счетчика, третий и четвертый выходы формирователя управляющих сигналов соединены с входами записи и считывания узла регистровой памяти, адресные входы которого соединены с группой выходов блока дешифрации памяти регистра, вторые адресные входы которого соединены с входом данных узла

5 регистровой памяти и выходами счетчика адреса, информационные входы ксторого соединены с выходами узла регистровой памяти, входустановки в единичное состояние которого соединен с выходом элемента

10 ИЛИ, первый вход которого соединен с входом начальной установки устройства, второй вход элемента ИЛИ соединен с выходом .дешифратора, вход которого является адресным входом устройства, вход установки

15 в нулевое состояние которого соединен с входом установки в нулевое состояние блока регистров, вход идентификации которого соединен с выходом идентификации блока дешифрации номера регистра.