Устройство для скользящего усреднения частотно-импульсного сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического управления для усреднения и преобразования в двоичный код сигналов датчиков с частотным выходом . Цель изобретения - повышение точности . Устройство содержит блок 1 регулируемой задержки, блоки 2, 3 вычисления разности частот, блоки 4 распределения импульсов, каналы 5 задержки, генератор 6 импульсов, релейный элемент 7, интегратор 8, элемент 9 дифференцирования, ограничитель 10, регистр 11. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)л G 06 F 15/36

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ а (21.) 4623820/24 (22) 21.12,88 (46) 07.12.91, Бюл, М 45 (72) В,И.Брихара (53) 681.3(088.8) (56) Авторское свидетельство СССР

N 1218405, кл. G 06 G 7/52, 1984.

Авторское свидетельство СССР

N 624235, кл. G 06 F 15/36, 1977, (54) УСТРОЙСТВО ДЛЯ СКОЛЬЗЯШЕГО УСРЕДНЕНИЯ ЧАСТОТНО-ИМПУЛЬСНОГО

СИГНАЛА /

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического управления для усреднения и преобразования в двоичный код сигналов датчиков с частотным выходом.

Цель изобретения — повышение точности.

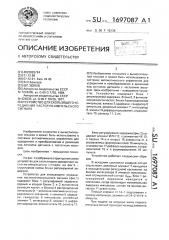

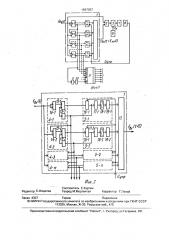

На фиг.1 изображена структурная схема устройства для скользящего усреднения частотно-импульсного сигнала; на фиг,2— структурная схема блока регулируемой задержки.

Устройство для скользящего усреднения частотно-импульсного сигнала (фиг.1) содержит блок 1 регулируемой задержки, первый и второй блоки 2 и 3 вычисления разности частот, и блоков 4 распределения импульсов (и — величина максимального ус редняемого значения), п каналов 5 задержки, генератор 6 импульсов, релейный элемент 7, интегратор 8, элемент 9 дифференцирования, ограничитель 10, регистр 11.

„„ Ы„„ 1697087 А 1 (57) Изобретение относится к вычислительной технике и может быть использовано в системах автоматического управления для усреднения и преобразования в двоичный код сигналов датчиков с частотным выходом. Цель изобретения — повышение точности. Устройство содержит блок 1 регулируемой задержки, блоки 2, 3 вычисления разности частот, блоки 4 распределения импулbcoB, каналы 5 задержки, генератор 6 импульсов, релейный элемент 7, интегратор

8, элемент 9 дифференцирования, ограничитель 10, регистр 11. 2 ил, Блок регулируемой задержки (фиг.2) содержит элемент ИЛИ 12, и элементов НЕ 13, и первых 14 и и вторых 15 элементов И, и управляемых формирователей 16 импульса, и элементов 17 дифференцирования, и ограничителей 18 и и формирователей 19 импульса.

Устройство работает следующим образом, В исходном состоянии входной сигнал О отсутствует, релейный элемент 7 находится 4 в отрицательном (исходном) состоянии, на С) выходе интегратора 8 имеется максималь- QO ный отрицательный сигнал Uypp, блок 1 регулируемой задержки находится в состоянии, когда происходит максимальная задержка импульсов, сигнал на выходе регистра 11 равен нулю.

Первый элемент И 14 — 1 подготовлен к приему импульсов, элементы И 14-2 — И 14 — п закрыты.

При подаче на входную шину первого импульса сигнал проходит на вход элемента

1697087

И 15, поскольку на второй вход этого элемента через элемент HE 13 подается логическая единица и запускает управляемый формирователь 16 импульса, который срабатывает, блокирует подачей логического нуля через элемент НЕ 13 прохождение второго импульса и одновременно разрешает прохождение сигнала на первом входе элемента И 14-2 следующей цепочки блока регулируемой задержки, Если к моменту прихода на вход блока

1 регулируемой задержки второго импульса не снят запрет на запуск формирователя

16-1, запускается формирователь 16-2. Таким образом, количество сработавших цепочек блока 1 задержки за время ЛТ определяется простотой импульсной последовательности и величиной управляющего напряжения Оулр, т,е. количество задействованных информационных выходов блока задержки зависит от количества импульсов за время ЬТ.

На входы блока 2 поступают входная

f(t) и задержанная импульсные последовательности, На выходе блока 2 получается импульсная последовательность, пропорциональная величине производной входного сигнала. Этот сигнал поступает на вход блока 3 вычисления разности частот, на второй вход которого поступает постоянная частота F< от генератора 6. На выходе блока 3 формируется сигнал, когда производная входного сигнала превышает определенное значение. Сигнал с блока 3 поступает на релейный элемент 7, выход которого соединен с интегратором 8. Если величина производной превышает пороговое значение F<, сигнал с релейного элемента уменьшает напряжение на выходе интегратора 8 Оудр, что приводит к уменьшению времени задержки.

На вход регистра 11 поступает информация о количестве сработавших информационных входов. Сигнал по первому информационному входу, проходя через элемент 9, ограничитель 10, формирует тактовый импульс, и на выходе регистра 11 получается выходной код, Формула изобретения

Устройство для скользящего усреднения частотно-импульсного сигнала, содержащее генератор импульсов и п каналов задержки (п — количеСтво дискретов . максимального усредняемого значения), каждый из которых содержит два элемента

И, о т л и ч а ю щ е е с я тем, что, с целью

5 повышения точности, в него введены элемент ИЛИ, два блока вычисления разности частот, релейный элемент, интегратор, элемент дифференцирования, ограничитель, регистр и в каждый канал задержки — эле10 мент НЕ, управляемый формирователь импульса, элемент дифференцирования, ограничитель и формирователь импульса, причем в каждом канале задержки выход первого элемента И соединен с первым вхо15 дом второго элемента И. выход которого соединен с входом запуска управляемого формирователя импульса, выход которого подключен к цепочке из последовательно соединенных элемента дифференцирова20 ния, ограничителя и формирователя импульса и через элемент НŠ— к второму входу второго элемента И, выход формирователя импульса j-ro канала задержки

0 = 1, и) подключен к j-му входу элемента

25 ИЛИ, информационный Вход устройства со единен с первыми входами первых элементов И всех каналов, с вторым входом первого элемента И первого канала и входом уменьшаемого первого блока вычисления разности частот, выход управляемого формирователя импульса i-го канала (i = Т, и-1) подключен к второму входу первого элемента И i+1-ro канала, выход управляемого формирователя импульса j-го канала подключен к j-му информационному входу регистра, выход управления формирователя импульса первого канала последовательно соединенные элемент дифференцирования и ограничитель подключен к тактовому вхо40 ду регистра, выход которого является выходом устройства, выход элемента ИЛИ соединен с входом вычитаемого первого блока вычисления разности частот, выход которого соединен с входом уменьшаемого

45 второго блока вычисления разности частот, вход вычитаемого которого соединен с выходом генератора импульсов, а выход — с входом релейного элемента, выход которого соединен с входом интегратора, выход кото50 рого подключен к входам управления длительностью импульса управляемых формирователей импульсов всех каналов задержки.

1697087

Составитель Е.Хуртин

Техред М.Моргентал Корректор Т.Палий

Редактор 5.Федотов

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 4307 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5