Устройство для формирования векторов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в графических дисплеях и графопостроителях . Цель изобретения - повышение точности устройства - достигается введением двух усилителей, двух мультиплексоров, двух селекторов и соответствующих функциональных связей. Изобретение позволяет формировать векторы как с коррекцией напряжений на выходе устройства (для повышения точности), так и без коррекции, если требуется высокое быстродействие. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 09 6 1/08

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР.Ф

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4753867/24 (22) 27.10.89 (46) 07,12.91. Бюл. ¹ 45 (71) Институт проблем моделирования в энергетике AH УССР, Специальное конструкторско-технологическое бюро средств моделирования в энергетике АН УССР (72) Г.И.Грездов, Ю.О.Шимановский и

В.А.Ярославкин (53) 681,327.11(088.8) (56) Авторское свидетельство СССР

N 1267469, кл, 6 09 G 1/08, 1983.

Авторское свидетельство СССР № 1277084, кл. G 06 F 3/153 1985.

Изобретение относится к автоматике и вычислительной технике и может быть использовано в графических дисплеях и графопостроителях.

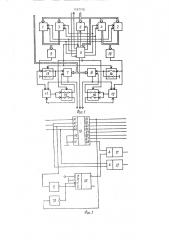

Цель изобретения — повышение точности устройства, На фиг.1 приведена структурная схема устройства; на фиг.2 — структурная схема блока управления; на фиг.3 — структурная схема интегратора; на фиг.4 — структурная схема ус ил,ителя.

Устройство содержит регистры 1-4, блок 5 управления, счетчик 6, интеграторы 7 и 8 цифроаналоговые преобразователи 9 и

10, усилители 11 и 12, мультиплексоры 13 и

14, селекторы 15 и 16, Блок 5 управления содержит инверторы

17,18, блок 19 постоянной памяти, триггер

20, элементы И 21,22.

Ы2 1697105 А1 (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

ВЕКТОРОВ (57) Изобретение относится к автоматике и вычислигельной технике и может быть использовано в графических дисплеях и графопостроителях. Цель изобретения — повышение точности устройства — достигается введением двух усилителей, двух мультиплексоров, двух селекторов и соответствующих функциональных связей. Изобретение позволяет формировать векторы как с коррекцией напряжений на выходе устройства (для повышения точности), так и без коррекции, если требуется высокое быстродействие, 4 ил, Интегратор 7(8) содержит коммутаторы

2324,резисторы 25 — 31, конденсаторы 32,33, операционный усилитель 34.

Усилитель 11(12) содержит резисторы

35 — 39 и операционный усилитель 40.

Устройство работает следующим образом, Из ЭВМ(на фиг.1 не показана) в устройство передается информация о координатах и параметрах вектора:

Х вЂ” координата "Х" начальной точки вектора;

Y — координата "Y" начальной точки вектора;

ЛХ вЂ” проекция вектора на ось "Х";

ЛУ вЂ” проекция вектора нв ось "Y" .

М-макс { ЛХ, Л У j — величина большей проекции

m — мин {ЛХ, ЛУ1 — величина меньшей проекции, V = m/Ì вЂ” приведенное значение меньшей проекции

1697105

l — код, соответствующий максимально возможной (еди нич ной) и рое кции вектора

I г

R =3 ЛХ + ЛУ вЂ” длина векгора, В общем случае информация о векторе передается тремя словами. Структура слов представлена ниже, В первом информационном слове, двоичный код номера слова которого ОО, передаются координаты точки начала вектора Х,> и Ón. На первом выходе блока 5 управления формируется импульс записи в регистры 1,2 координат Х, и Ур, Одновременно с импульсом записи в регистры 1,2 на девятом выходе блока 5 управления формируется сигнал готовности, по положительному фронту которого производится смена входной информации, Следующим приходит слово, двоичный код которого 01. В этом слове содержатся величины и V, которые записываются в регистры 3 и 4 импульсом записи, формируемым на третьем выходе блока 5 управления. Одновременно с появлением кода слова 01 блок 5 управления формирует на восьмом выходе сигнал управления селекторами 15,16, которые подключают на вторые информационные входы интеграторов

7 и 8 напряжения с выходов усилителей 11 и 12, К этому моменту на первые информационные входы интеграторов подается нулевой потенциал, а на выходах усилителей

11 и 12 присутствует разность между выходными напряжениями цифроаналоговых преобразователей и соответствующих интеграторов, Разность напряжений на входах усилителей 11,12 начинает уменьшаться. Она уменьшается до тех пор, пока напряжение на выходе интегратора HB станет равным напряжению на выходе соответствующего цифроаналогового преобразователя, На входах же цифроаналоговых преобразователей в этот моменг присутствуют коды координат Х и У >(в этот момент на втором выходе блока 5 управления присутствует сигнал, разрешающий считывание аз регистров 1,2).

По окончании записи в регистры 3,4 параметров вектора (содержимое слова с кодом 01) сигнал готовности позволяет принять следующее слово, двоичный код которого 10. В этом слове содержится величина М, которая импульсом записи с пятого выхода блока 5 управления записывается в счетчик 6, На выходе счетчика 6 при этом появляется высокий потенциал, обозначающий, что идет формирование вектора. На шестом выходе блока 5 управления формируются счетные импульсы в счетчик длины вектора, который работает в режиме вычи20

35 0

55 тания. При достижении счетчиком 6 нулевого состояния íà его выходе устанавливается низкий уровень напряжения, обозначающий окончание формирования вектора. Выходы цифроаналоговых преобразователей 9 и 10 при помощи мультиплексоров 13, 14 подключаются к первым информационным входам интеграторов 7 и 8 только на время формирования вектора. В момент появления кода слова 10 сигнал на втором выходе блока 5 переводит регистры 1 и 2 в третье состояние, а сигнал на четвертом выходе блока 5 считывает данные иэ регистров 3,4.

Сигнал формирования вектора с выхода счетчика 3 запрещает формирование сигнала готовности вплоть до окончания формирования вектора, Таким образом, слово, двоичный код которого 10, присутствует на входе в течение всего времени формирования вектора, После окончания формирования вектора появляется сигнал готовности, разрешающий смену входной информации, Если следующее слово имеет двоичный код

00, весь описанный цикл повторяется. При этом, если вследствие каких-либо причин напря>кения на выходах интеграторов 7 и 8 отличаются от напряжений на выходах цифроаналоговых преобразователей, соответственно 9 и 10, происходит, как описано выше, коррекция выходных напряжений интеграторов, и координаты начальной точки следующего вектора точно соответствуют координатам, записанным в регистрах 1 и 2.

Если же следующее, после окончания формирования вектора, слово имеет код 01, напряжения интеграторов не корректируются, а цикл работы в этом случае повторяет предыдущий, начиная с второго слова, Задание параметров векторов в виде, описанном выше, приводит к тому, что яркость наклонных векторов отличается от яркости ортогональных, Чтобы избежать э ого, необходимо в качестве параметров вектора задавать не I,а I/Я, не V,а V/й, не

М, а M R, При этом обеспечение нужного порядка расположения параметров„вектора в слове возлагается на ЭВМ.

Таким образом, устройство позволяет работать как с коррекцией выходных напряжений интеграторов, что исключает накопление погрешности и снимает ограничения

На количество формируемых векторов, так и без коррекции, что позволяет повысить быстродействие устройства при формировании малых векторов (например, текстовой информации), Для устранения погрешности, накопленной при формировании некоторого количества малых векторов, необходимо подать на третий вход устрой1б97105

Второе слово

Третье слово

Первое слово

1 р-д1 номер слова

2 р-д р л

1 р-д номер слова

2 р-д

1 р-д1

„ номер слова г р-д

1р-д Х

1 р-д

Ч, или l или к к

КилиМR

p-a X р-д 7 о

{и+1) рТ М1 и р-д

1 р-д или Ч, или

I V ц9 или и р-д г и рства слово, код которого 00, содержащее координаты начальной точки следующего вектора.

Векторы можно формировать с различными скоростями. Для выбора скорости 5 подают соответствующий код на управляющий вход устройства.

cDopMyna изобретения

Устройство для формирования векторов, содержащее с первого по четвертый 10 регистры, счетчик, первый и второй цифроаналоговые преобразователи, первый и второй интеграторы, блок управления, первый выход которого соединен с входами управления записью первого и второго регистров, 5 входы управления считыванием которых соединены с вторым выходом блока управления, третий выход которого соединен с входами управления записью третьего и четвертого регистров, входы управления 20 считыванием которых соединены с четвертым выходом блока управления, пятый выход которого соединен с управляющим входом счетчика, тактовый вход которого соединен с шестым выходом блока управ- 25 ления, седьмой вы од которого является выходом видеосигнала устройства, информационные входы с первого по четвертый регистров, счетчика и блока управления являются информационным входом уст- 30 ройства, выход счетчика соединен с управляющим входом блока управления, тактовый вход которого является тактовым входом устройства, выходы первого и третьего регистров соединены с информацион- 35 ными входами первого цифроаналогового преобразователя, информационные входы второго цифроаналогового преобразователя соединены с выходами второго и четвертого регистров, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, оно содержит первый и второй мультиплексоры, первый и второй селекторы, первый и второй усилители, выходы которых соединены соответственно с информационными входами первого и второго селекторов, управляющие входы которых соединены с восьмым выходом блока управления, девятый выход которого является выходом сигнала готовности устройства, управляющие входы первого и второго интеграторов являются управляющим входом устройства, первые информационные входы первого и второго интеграторов соединены соответственно с выходами первого и второго мультиплексоров, управляющге входы которых соединены с выходом счетчика, выходы первого и второго цифроаналоговых преобразователей соединены соо)ветственно с первыми информационными входами перового и второго мультиплексоров, вторые информационные входы которых соединены с шиной нулевого потенциала, первые информационные входы первого и второго усилителей соединены соответственно с аыходами первого и.второго цифроаналоговых преобразователей, вторые информационные входы первого и второго интеграторов соединены соответственно с первыми выходами первого и второго селекторов, вторые выходы которых соединены соответственно с вторыми информациочными входами первого и второго усилителей, выходы первого и второго интеграторов, соединенные соответственно с третьими информационными входами первого и второго усилителей, являются первым и вторым выходами отклоняющих напряжений устройства.

169 7105

П

Фдг, 2

Составитель И.Загинайко

Редактор Б.Федотов Техред М.Моргентал Корректор M.Äåì÷åíêo

Заказ 4308 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4!5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101