Фильтр - реле тока

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике , в частности к устройствам релейной защиты электроустановки, Цель изобретения - повышение чувствительност 1 в условиях отклонения частоты от номинальной и надежности работы во всех режимах работы линии. Цель достигается тем, что в устройство дополнительно введена фильтр прямой последовательности 41, цифровой сум:лз ор 30, форми -ратель сигнала коррекции уставки 24. 1 и

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУбЛИК

„„5U „„16971 38А1 (я)5 Н 01 Н 83/20 // Н 02 Н 3/08

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР,4 ° 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

C АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4727144/07 (22) 07.08.89 (46) 07,12.91. Бюл. ¹ 45 (71) Ленинградский политехнический институт им, М, И. Калинина (72) А. И, Таджибаев и С. В. Чурсин (53) 621.316,925(088.8) (56) Авторское свидетельство СССР № 1295471, кл. Н 02 Н 3/08, 1985.

Авторское свидетельство СССР

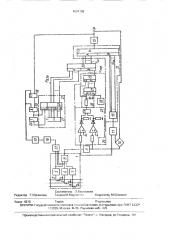

N 1541700, кл. Н 02 Н 3/08, 198, Изобретение относится к автоматизации энергетических систем и может быть использовано в релейной защите и протИвоаварийной автоматике, Целью изобретения является повышение чувствительности в условиях отклонения частоты от номинальной и повышение надежности работы во всех режимах работы линии, На чертеже представлена схема фильтрреле тока.

Фильтр-реле содержит формирователь контролируемого сигнала, включающий трансформаторы 2, 3, 4 тока, входные преобразователи 5, 6, 7 тока и фильтр 8 симмет.— ричных составляющих, первый элемент 9 задержки, ключ 10, сумматор 11, сравнивающий блок 12, включающий аналого-цифровой преобразователь 13 и цифровой компаратор 14, реагирующий элемент 15, амплитудный детектор 16, элемент ЗАДЕРЖКА НА СРАБАТЫВАНИЕ 17, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18, элемент И-НЕ 19, элемент НЕ 20, блок 21 задания уставки, (54) .ФИЛЬТР-РЕЛЕ ТОКА (57) Изобретение относится к электротехнике, в частности к устоойствам релейной защиты электроустановки, Цель изобретения— повышение чувствительност 1 в условиях отклонения частоты от номинальной и надежности работы во всех режимах работы линии. Цель достигается тем, что в устройство дополнительно введень фильтр прямой последовательности 31, цифровой сум:. а-ор 30, формир-ватель сигнала коррекции уставки 24. 1 .:.n. включающий формирователь 22 кода устаВоК и мультиплексор 23, формирователь 24 сигнала коррекции уставки, включающий фазовый детектор 25, второй элемент 26 задержки, счетчик 27, генератор 28 стабильной частоты и регистр 29 памяти, цифровой сумматор 30 и фильтр 31 прямой последовательнссти, Работает фильтр-реле следующим образом.

На выходе формирователя 1 может быть сформирован контролируемый си.нал U< в виде напряжения, пропорционального току прямой или обратной, или нулевой последовательности, фазному току или их комбинации. На выходе сумматора 11 выделяется аварийная составляющая сигнала путем сум -ирсваниг, его с выходным сигналом первого элемент= 9 задержки. На номинальной частоте коэффициент передачи первого элемента задержки равен единице, а фазовый сдвиг — 180 . Цифровым компараторсм

14 сравнивающего блока 12 производится сравнение кода аналого-цифрового преоб1297133 разователя 13 N!nK и кодэ ка выходе }г«1фрсf3oro сумматора 30 Nyi, П ричем

} }уСт =}а)БЗаГ +! «)КОр, irÄB !«)ЬЗЧ вЂ” КОД На 31-.!ХОДЕ мультиплексора 23; N«<>» — !<.îä на выходе регистра 29 г:амяти формировэтел ; 24 сигнала коррекции уставки, Значенле кода уставки Npay может принимать два 3 -i-: }е,-.ия;

}а} 1 и N2 в заВисимссти ")т рея» имr<;.30()Tb защищаемой линии, При Hdcro; -: сигнал,, Нк, РаВНОй НОМИН3 bHOV" }Ы), Ll), ЭНЗЧЕКИ:= : кода N.o;> равно нулю.

В режиме, когда защи}цае«n.-aë лики; отключена... .=-О, а уровень вьх:;.qHbix сиг налов сравнивающего блока 12, реагиру}сщего элемента . 5, амплит, ДH:; .", детектора 16, элеме;; =: 3)а jFPÆI("

CPAbAThlBAHt 17 са-<тветс!в Р:а! ло! Иче" скому "0", При этом кл,эч 10 замкнут. На выходе элемента И-Н" !(9 формируеа ..:я ".и!нал логической "1". В результате на i:b!>Од мультиплекс )pa 23 э видe о-Оазррдк;ro Кода коммутируется, cTBDI

СамаздПУСКВ }зал, Т, 8, )«11 -.- К }аа>) где К -- коэффициент преобразо}зания.

При вкл!Очении линии под нагрузку ка выходе формирователя 1 возникае) напряжение U < и формируется си нал на Вь;.::о,,"сумматора 11. Но этог сигнал Не п . и}аодит;< срабатыванию pear èðóþùåãî элемента 1, -:, l 3K К3К N>n«!а}ус)= ЙЕTy=- }а}1. IОЯВЛ(НИЕ

НВПРЯЖ8НИЯ i< ÎßÌÎÉ ПОСЛЕДС В31 ЕЛЬ! !2CT и b! а выходе фильтра 31, кроме того, Г!риводи)<. !i срабатыванию амплитудного детек": ора 1! б и с задер><кой элемента ЗАДЕРЖКА НА СР,-,БА ЫВАНИ" ".7, Величика вае}лен}л задержки определяется максимально Воэмох<ной длительностью переходно о процесса в первом элементе 9 задержки. После перехода элемента ЗАДЕРЖКА НА а РАБАТЬ}Вга.НИЕ 17 в состояли" логической "1 На выходе элемента И-НЕ 19 г}«2яв) .IB, ся логический "0, Б резу)bTare На выход мультиПЛЕКСО})3 23 KOMIЛУТИра:«- Т Ся 1<с Га 3K,: и< входу Y Nz. Значение М; "f-ределяется исходя из вел}лчины наибольщегo броска то})

Ка НВГРУЗКИ В НВГРУЗОЧНОРЛ ()8>КИМЕ наср

Ng О K l >Ра- Я чеавидко при ".>ТОМ, что .бр й2< N1, В случае вклк)кения линии из от<люченного состояния на короткое замыкал!ie (K3) величина напрг!>Кения ка вы:(о 28 сумматора 11 правы}аает уставку iN1, .

8. N>nK> Nyrr= N1. Р еаг}лРУк)щ}лЙ . 2г!еме-IT

15 срабатывает, и линия отклк.чается

В случае возникнаве:.ия КЗ на включенной под кагрузку лил<ли уровень скачка наг}ряжения на выходе сумматора 11 }n соответственно сигнала в цифровом коде на

5 Выходе прео,разователя 13 оказывается

ВЬ}щ}ъ ЗНВЧЕНИя }<1< Соврав сЫВ<ЭЮТ циф})овои ком<п<арат<эр 1}4 и реаг}лрующ!)é элеме.-}т 15, В p83 ëьтаа е размыкается кл}ач 10, обеспечивая надел.Ное самоудержигание филь-:р10 реле в- сработанн.-.)м coc(ОЯнии, Элемент

И-!) Е 1 9 переходит B ccicT< f)H v<8, lo! иче< кай

"1", yl в блоке задания устаек}л происходит г}ерекгючение уставки с " > Ha I,l;,. Под дейСа" }8}Л Вь}ХОДНОГО СИГИ-)Г}3 рва; ИруЮ«цека л= MBI- 3 15 прс>и" opi < ()т!<л}оценив защи—

«ма<Э!«10!) Л!<а -! ли И ф}ЛЛЬТР ОЕЛB ВОЗВРащаЕТ Я

В ИСКOi„HC;8 OCTO;3 Н ИЕ °

Прл раб те ка номинальной:астоте Рном входное и выходное лапрях<ение первого

20 элемента 9 задер:-}<ки находится в противофазе. На выходе фазового детектопа 25 формируется с.лгнал ло!.n»BOKofn "1", через

Второй элемент 26 з})дерх(ки удерживая счетчик 27 В абнуленн;f«cocTo fHvln, В ре25 зуль)ате }чкор=0, При отключении частать!

СИГH3f!3 Цк OT НОМИНВЛЬНОЙ (= ном.1Г На ВЫходе сумматора 11 возникает напрях<ение

НЕбагlане3 .)нс>, а Ка ВЫХОДЕ 3НВЛОГС цИф

}20ВРГО ПО80браз(2Вателя 13 КОД Кнб. ОД

30 llавременнО фа}зовый сДвиГ ВхоДнОГО и выходного }!апряжений первого элемента

9 ЗВДЕР>ККИ .",ТЗНОВИТСЯ ОТ)<ИЧНЫМ OT 1С>0, На выходе фазового детектора 5 появляется (дваждь: за пер}лад 1)к! Импульс нулевого ,.".> УРовкя, Длительность котоРаго Tфд пРопоРЦИОНВЛЬНа ОТКЛОНЕНИ}С ЧЗСта..bi дк. Геi!BPa-..са 28 стабильной час(оты вырабать:вает

ИМПУЛЬСЫ С IBÑòOòàé Гг. И КатОРЫМИ НаПОЛняется счетчик 27 за "- эемя т4}д, Сип ал в

4 " виДе коДа I«I «p пеРеп lcblaaется из счетчика

; 7 в реГистг) 29 памЯти Б момент появлениЯ

Рлмпульса единичлОГО уровня на ВыхОде дегектора 25, Второ}л элемект 26 задерж(è в виде РС-цепл служит дл задер>кки поступ45 г}ения иРлпульса едини -IHÎf о уровня 3 RВход счеT.- ик - .7 с целью 1<адежHОГО

СЧИ" ЫВВН ЛЯ Кода Йкор !28Г<ЛСТРОРИ )9 ПВМЯТИ.

:: H3×8ÍÈ2 КОД3:«! Pf)BKЦVill УСТВВКИ p Tr.u г <а 4:ор=-—

Кг}

r!8 К -- коэффициент делBHi;Я счетчиK3 27.

Работа формирователя сигнала коарек}>И}i УС i 33K}1 ИДЕ >ном.

11<}лфро!)ым сумматорсм,)0 г}рслзводитСя:-"!To>KBHV<8 КОДОВ !а}}кi l " I"!i<<>f» Е 1 year=

:=Мкор+ МАЗУ, В РезУльтате пРИ ст .лонсчии в нормаг)ьном режиме;астоть, ат но!,инэльНГ}1 ПРОИЗВОДИтСЧ KOРРВКЦИЯ !<а!.,С,; ТЗК, ЧТО вакф > М,ь. Заглубление фильтр-реле тока в этом случае происходит только при f=f>i<».

Амплитудный детектор 16, подключенный к выходу фильтра 31, обеспечивает выявление тока в защищаемой линии при 5 любом ее режиме работы.

Формула изобретения

Фильтр-реле тока, содержащий формирователь контролируемого сигнала, выполненный в виде Входных преобразователей 10 тека, подключенных входами к соответствующим трансформаторам тока линии, 8 выходами к Входам фильтра симметричных составляющих, выход которого является выходом формирователя контролируемого 15 сигнала, он подключен к первому вхоцу сум. матора и через последовательно соединенные первый элемен — задержки и ключ к второму входу сумматора, Выход которого соединен с первым входом сравнивающего 20 блока, выполненного в виде последовательно соединенных аналого-цифрового преобразовагеля и цифрового компаратора, причем вход аналого-цифрового преобразователя является первым входом срав- 25 нивающего блока, выходом которого является выход цифрового компаратора, соединенного с входом реагирующего;. емента, выход г1оследнего явл ется выходом фильтр-реле тока, который подключен к уп- 30 равляющему входу ключа и к первому вхоцу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, последовательно соединенные амплитудный детектор и элемент задержки на срабатывание, выход последнего подключен к первому вхо- 35 ду элемента И-НЕ и к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом элемента И-НЕ, выход которого подключен к первому входу блока задания уставки и к входу элемента

НЕ, выход которого подключен к второму входу блока зацания уставки, выполненного в виде последовательно соединенных формирователя кода уставок и мультиплексатора, первый и второй входы последнего соответственно являются первым и вторым ВхоДами, 8 его ВыхОД выхоДом бло ка задания уставки, отличающийся тем, что, с цель О повышения чувствительности в условиях отклонения астоты оТ номинальнсй и надежности оаботы Во всех режимах работы линии, в него введены фил ьтр прямой 11осл едовател ь насти, цифроВой сумматор и формирователь сигнала коррекции уставки, выполненный В виде генератора сгабильной частоты и последовательно соединенных фазового детектора, Второго элемента задержка, Р,— âõoäà счетчика и D-входов регистра памяти, причем первый и второй входы фазового детектора подключены соответственно к входу и выходу первого элемента задержки, выход генератора стабильной частоты подключен к

С-входу счетчика, выход фазового детектора подключен к С-входу регистра памяти, выход Kolорогс является выходом формирователя сигнала к:- екции сигнала и подключен к пера му входу цифрового сумматора, вторые В, оды ксторо-о подключены к вь;".Одам блоха задания уставки, а выходы — к вторым входам цифрового компаратора сравнивающего блока, филf,T(! прямой последовательности Включен между выходами входных преобразователей тока и входом амплитудного детектора.

1697138

Составитель Л.Во,:зопаева

Редактор Т,НЗрчикова Техред M.MîðãàãT Корректор M.Øàðîøè

Закаэ 4310 Гираж Подписное

ВНИИПИ Госуд рс- ого ко..итета о ..-;обретен»: и от р при ГКНТ СССР

113G35, Москва, Ж-35, Рауоккая наб., 4/5

Производственно-издательский комбинат Патент", г, Ужгород, ул, Гагарина. 1О1