Устройство допускового контроля скорости изменения периода сигнала

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в системах автоматического контроля и управления . Целью изобретения является расширение функциональных возможностей путем обеспечения допускового контроля скорости изменения периода сигнала с возможными помехами при надежном обнаружении пропадания сигнала. Устройство допускового контроля скорости изменения периода сигнала содержит формирователи 1-4 коротких импульсов, элементы ИЛИ 10- 12, элементы И 13-15, счетчик 16 импульсов, регистр 17 и общую шину. Для достижения цели в устройство введены интеграторы 5-7 и пороговые элементы 8 и 9. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 01 R 23/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4697599/21 (22) 26.05.89 (46) 15 12.91. Бюл. № 46 (71) Институт спектроскопии АН СССР (72) В.И.Азаров (53) 681.3(088.8) (56) Авторское свидетельство СССР

¹ 811156, кл. G 01 R 23/00, 07.03.81.

Авторское свидетельство СССР № 1325375, кл. G 01 R 23/00, 23,07,87, (54) УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ СКОРОСТИ ИЗМЕНЕНИЯ ПЕРИОДА

СИГНАЛА .

«„Я3. «,1 698815 А1 (57) Изобретение может быть использовано в системах автоматического контроля и управления. Целью изобретения является расширение функциональных возможностей путем обеспечения допускового контроля скорости изменения периода сигнала с возможными помехами при надежном обнаружении пропадания сигнала. Устройство допускового контроля скорости изменения периода сигнала содержит формирователи

1 — 4 коротких импульсов, элементы ИЛИ 10—

12, элементы И 13 — 15, счетчик 16 импульсов, регистр 17 и общую шину. Для достижения цели в устройство введены интеграторы 5 — 7 и пороговые элементы 8 и 9, 3 ил.

1698815

Изобретение относится к электро- и радиоизмерительной технике и может быть использовано в различных системах автоматического контроля и управления.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения допускавого контроля скорости изменения периода сигнала с возможными помехами. при надежном обнаружении пропадания сигнала.

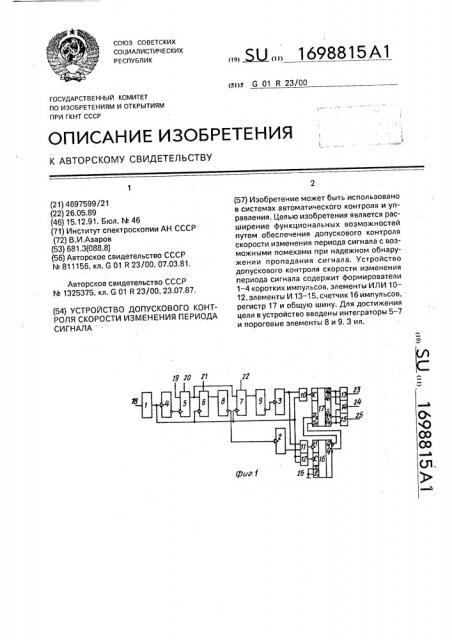

На фиг.1 представлена функциональная схема устройства допускового контроля скорости изменения периода сигнала, на фиг.2 — эпюры напряжения.

Устройство содержит первый, второй, третий и четвертый формирователи 1,2,3 и 4 коротких импульсов, первый, второй и третий интеграторы 5,6 и 7, первый и второй пороговые элементы 8 и 9, первый, второй и третий элементы ИЛИ 10,11 и 12, первый, второй и третий элементы И 13,14„и 15, счетчик 16 импульсов, регистр 17, входы 18—

22 устройства, выходы 23-25 устройства, общую шину 26, BbfXopbt 3llBMBHTOB И 13-15 являются выходами 23 — 25 устройства, к входам элемента И 13 подключены прямые выходы регистра 17, к входам элемента И 15— инверсные выходы регистра 17, а к входам элемента И 14 — прямой выход нулевого и инверсный выход первого разрядов регистра 17, информационный вход которого подключен к выходу счетчика 16, нулевой и первый разряды информационного входа которого подключены к общей шине 26, а счетный вход и вход записи соответственно к выходу второго и выходу третьего элементов ИЛИ 11 и 12, к входу записи регистра 17 подключен выход первого элемента ИЛИ

10, к входам которого подкл очены выход первого и выход третьего формирователей

1 и 3 коротких импульсов, к входам второго элемента ИЛИ 11 подключены выход втара.го и выход третьего формирователей 2 и 3 коротких импульсов, а к входам третьего элемента ИЛИ 12 — выход первого формирователя 1 коротких импульсов. вход которого является первым входом 18 устройства, входом контролируемого сигнала, выход первого формирователя 1 коротких импульсов подключен также к входу четвертого формирователя 4 коротких импульсов и к третьим управляющим входам первого и третьего интеграторов 6 и 7, первые входы которых являются соответственна четвертым и пятым входами 21 и 22 устройства, вторым и третьим входами 19 и 20 которого являются соответственно второй и первый входы перaoro интегратора 5, третий вход которого подключен к инверсному выходу четвертого формирователя 4, а выход — к вторым вха5

55 дам второго и третьего интеграторов 6 и 7, выходы которых подключены соответственно к входу первого и входу второго пороговых элементов 8 и 9, инверсные выходы которых подключены соответственно к входу второго и входу третьего формирователей 2 и 3 коротких импульсов.

На фиг,2 обозначены напряжения на выходе первого и четвертого 1 и 4 формирователей коротких импульсов (а) и (б), второго и третьего формирователей 2 и 3 коротких импульсов (в) и (г), первого интегратора 5(д), второго и третьего интеграторов 6,7 (е) и (ж), на первом, втором, третьем выходах устройства 23,24 и 25 (з), (и) и (к), На фиг.3 представлена диаграмма напряжений на выходе первого и четвертого формирователей 1 и 4 коротких импульсов (а) и (б) и на выходе первого и второго интеграторов 5 и 6 в масштабе, позволяющем наблюдать переходный процесс при установке в интеграторы начального напряжения.

Устройство работает следующим образом.

По сигналу на первом входе 18 устройства первый формирователь I формирует последовательность коротких импульсов » с тем же периодом, чта и сигнал (фиг.2а).

Первый интегратор 5 постоянно интегрирует положительное напряжение, установленное на третьем входе 20 устройства и периодически передним фронтом импульса с выхода четвертого формирователя 4 устанавливается на напряжение, заданное на втором входе 19 устройства (д). Длительность импульса, формируемого четвертым формирователем 4 (фиг.2б, фиг.Зб), устанавливают как можно меньшей, но не менее длительности переходных процессов при записи в интеграторы 6 и 7.

К приходу переднего фронта импульса т», где I — любое целое, на выходе первого

1 интегратора 5 будет находиться напряжение

0 = К1U> (Т вЂ” zq)+ Uo, 0 >О,К1>0, 0)>О,Uo>0, где K> — коэффициент пропорциональности, характеризующий строение первого интегратора 5;

Uo и U> — положительные напряжения на втором и третьем входах 19 и 20 устройства; т - — длительность импульса, формируемого четвертым формирователем 4; (Т вЂ” интервал между импульсами to 1 и

1о

Чтобы напряжение 0 на выходе перво1

ro интегратора 5 (фиг.Зв) к моменту прихода

1698815 переднего фронта импульса to (фиг.3э) соотI ветствовало Т вЂ” интервалу между импульса-! ми to и t>, на второй вход t9 устройства !

1 I подают напряжение Up = K1 01 т4, компенсирующее запаздывание на r4 установки 5 первого интегратора 5 по. отношению к времени прихода переднего фронта им!

-1 пульса о

Если указанное напряжение U< установлено, то по переднему фронту импульса 10

t< во второй и третий интеграторы 6 и 7 установится напряжение U!=K1U1T с выхоI. да первого интегратора 5.

Далее вплоть до импульса to, второй и третий интеграторы 6 и 7 будут интегрировать отрицательные напряжения, присутствующие соответственно на четвертом и пятом входах 21 и 22 устройства (e), (ж).

Напряжения на выходе второго и третьего интеграторов 6 и 7 достигают нулевого 20 значения (при отсутствии импульса t< ) соответственно через интервалы времени

Т !+1 Т2 1

ТI1+1 = K1 U1 Т!

K2 I U2 l 25

Т +1 Кг 01 Т!

Ka Ual

Ka>0: К2>0; 02<0; Оз < О, где Кг и Ка- коэффициенты пропорциональ- 30 ности, характеризующие строение второго и третьего интеграторов 6 и 7 соответственно; U2 и Оз — напряжение на четвертом и пятом входах 21 и 22 устройства соответственно, 35

Проверка условия T1 < Т < Тг !

+1 . !+1 I+1 осуществляется путем форми !ования по истечении интервалов Т1 и Тг после пере-!

+1 +1 днега фронта импульса t>, при помощи

I первого и второго пороговых элементов 8 и 40

9 и второго и третьего формирователей 2 и

3 коротких импульсов t1"" и t2 (фиг. 2 в и г ) и определения положения ожидаемого импульса to относительно этих двух импульi+1 сов. Осуществляется эта проверка и выдача соответствующих сигналов аппаратурой контроля очередности прихода импульсов, тод1 и 12, включающей в себя элементы ИЛИ

10 — 12, элементы И 13-15, счетчик 16 и регистр 17 с соответствующими связями.

Своим передним фронтом каждый из импульсов с1 и t2 формируемых соответст-.. венно вторым и третьим формирователями

2 и 3, прибавляет единицу к содержимому счетчика 16, а задним фронтом импульсов to 55 и сг информация из счетчика 16 переписывается в регистр 17, причем задним фронтом импульса to счетчик обнуляется, т.е. переходит в исходное состояние, начиная тем самым новый цикл контроля времени прихода очередного импульса t<.

Возможны следующие варианты прихода очередного импульса to

j+1.

Импульс to приходит раньше 11, В

I+1 I+1 этом случае по переднему фронту импульса во второй и третий интеграторы 6 и 7

I+1 заносится напряжение U с выхода первоi+1 го интегратора 5, отменяя тем самым„формирование импульсов t1 и 12 и запуская !

+1 i+1 процесс, в результате которого должны бу-!

+г !+2 дут формироваться импульсы t1 и t2 для контроля следующего импульса to . Кроме

i+2 !

+1 того, задним фронтом импульса то, прошедшего через первый элемент ИЛИ 10, в регистр 17 заносится код "00" с выхода счетчика 16, который обнуляется задним фронтом импульса to прошедшего через

I+1 третий элемент ИЛИ 12, используемый в качестве задержки. В результате чего аппаратура контроля переходит в исходное состояние и готова контролировать приход импульса то, а на третьем выходе 25 устI+2 ройства присутствует логическая единица при нулях на двух других выходах 23 и 24, свидетельствующая о раннем приходе импульса to, — сигнал "Период меньше нормы".

Импульс t< приходит позже импульса

i+1 !

+1 !+1

t1 ", но раньше импульса t2 ". В этом случае напряжение на выходе второго интегратора

6 через время Т! после переднего фронта импульса to понижаясь, проходит нулевой

I уровень. Вследствие чего, на инверсном выходе первого порогового элемента 8 появляется положительный перепад, по которому второй формирователь 2 формирует короткий импульс t1 который, пройдя через !

+1 второй элемент ИЛИ 11; своим передним фронтом увеличивает содержимое счетчика

16 на единицу, на выходе которого появляется код "01".

С приходом импульса to, по его nepei+1 днему фронту во второй и третий интеграторы заносится напряжение U с выхода первого интегратора 5, отменяя тем самым формирование импульса t2 и запуская процесс, в результате которого должны будут сформироваться импульсы t1 и 12 для контроля следующего импульса to

Кроме того, задним фронтом импульса то I+1 проведшего через первый элемент ИЛИ 10, в регистр 17 заносится код "01" с выхода счетчика 16, который обнуляется задним !

+1 с. фронтом импульса to прошедшего через третий элемент ИЛИ 12, используемый в качестве задержки, в результате чего аппаратура контроля переходит в исходное состояние и готова контролировать приход очередного импульса то, а на втором выхоi 2

1698815 де 24 устройства присутствует логическая единица при нулях на двух других выходах

23 и 25 устройства, свидетельствующая о нормальном приходе импульса tp, — сиг1 нал "Период в норме". 5

Импульс tp приходит позже импульса

i+1

1г1+1 или не и риходит вообще. В этом случае, аналогично предыдущему сформируется ко1+1 роткий импульс t1 который, пройдя через второй элемент ИЛИ 11, своим передним 10 фронтом увеличивает содержимое счетчика

16 на единицу, на выходе которого появится код "01". Кроме того, напряжение на выходе третьего интегратора 7, через время Тг

1+1 после переднего фронта импульса tp, пони- 15

I жаясь, проходит нулевой уровень. Вследствие этого на инверсном выходе второго порогового элемента 9 появляется положительный перепад, по которому третий формирователь 3 формирует короткий импульс 20, который, пройдя через второй элемент

ИЛИ 11, своим передним фронтом увеличивает содержимое счетчика 16 на единицу, на выходе которого появляется код "11", который, пройдя через первый элемент ИЛИ 10 25 своим задним франтом, переписывает код

"11" с выхода счетчика 16 в регистр 17. В результате на первом выходе 23 устройства присутствует логическая единица при нулях на двух других выходах 24 и 25, свидетель- 30 ствующая о позднем приходе или отсутствии ожидаемого импульса tp вообще—

I+1 сигнал "Период больше нормы", В случае прихода импульса tp по его

1+1 переднему фронту во второй и третий интег- 35 раторы б и 7 заносится напряжение Ui с выхода первого интегратора 5, запуская процесс, в результате которого должны буAye сфармирова ca vMnyn cbi t1 z т г длЯ контРолЯ следУющего импУльса tp г 40

Кроме того, задним фронтом импульса tp I+1 прошедшего через первый элемент ИЛИ 10, ° в регистр 17 повторно заносится код "11" с выхода сче1чика 16, который обнуляется задним фронтом импульса tp прошедшего 45

I+1, через третий элемент ИЛИ 12, используемый в качестве задержки. Диагностика при этом не меняется, а аппаратура контроля переходит в исходное состояние и готова контролировать приход очередного импуль- 50 сато г, Импульс tp перекрывается во времеi+1 ни импульсом т1

Поскольку по переднему фронту импульса tp, где i — любое целое, второй 55

I+1 интегратор 6 устанавливается на начальное положительное напряжение, то максимальный интервал го1между передним фронтом импульса tp и передним фронтом импуль1+1

Са t1, СЛЕДУЮЩЕГО ПОЗЖЕ ИМПУЛЬСа tp

I+1 1+1 равен максимальному времени задержки конца интегрирования и начала установки, второго интегратора 6 относительно переднего фронта импульса т< плюс максиi+1 мальное время задержки первого порогового элемента 8 плюс максимальное время задержки второго формирователя 2.

Для надежного перехода аппаратуры контроля в исходное состояние необходимо обеспечить отсутствие гонки переднего фронта импульса т1 и заднего фронта имi+1 пульса tp, для чего необходимо, чтобы заi+1 дний фронт импульса то приходил позже

1+1

1+ переднего фронта импульса т1 на время т — время срабатывания элемента ИЛИ плюс время задержки переключения счетчика 16. Отсюда для длительности импульсов

tp tp имеем требование: т> > t „1+ т

При выполнении этого условия появление импульса т1 при контроле прихода

1+1 импульса то надежно влечет диагностику

1+1

"Период в норме", а отсутствие — диагностику "Период меньше нормы", Импульс tp перекрывается во време1+1 ни с импульсом тг . Для длительности импульсов tp имеем требование Tp ) туг+ t где toz — максимально возможный интервал между передним фронтом импульса tp

1+1 и передним фронтом импульса tz следую1+ щего позже импульса tp . С другой стороны, I+1 поскольку по заднему фронту импульсов tz происходит запись в регистр 17, а обнуление счетчика 16 должно быть позже перепиci его содержимого в регистр 17, необходимо, чтобы t p woz+ tg,гд е г z— длительность импульсов tz, При выполнении этого условия задний фронт импульса tz, если импульс появля1+1 ется, всегда предшествует заднему фронту импульса tp, что гарантирует в начале nei+1 репись в регистр 17 -одержимого счетчика

16, а затем уже обнулечие последнего.

Формула изобретения

Устройство допускового контроля скорости изменения периода сигнала, содержащее первый, второй, третий и четвертый формирователи коротких импульсов, первый, второй и третий элементы ИЛИ, первый, второй и третий элементы И, счетчик импульсов, регистр и общую шину, причем первым, вторым и третьим выходами устройства являются соответственно выходы первого, второго и третьего элементов И, к входам первого из которых подключены прямые выходы регистра, к входам третьего — инверсные выходы регистра, а к входам второго— прямой выход нулевого и инверсный выход первого разрядов регистра, информацион1698815

10 ный вход которого подключен к выходу счетчика импульсов, нулевой и первый разряды информационного входа которого подключены к общей шине, а счетный вход и вход записи — соответственно к выходу второго и 5 третьего элементов ИЛИ, к входу записи регистра подключен выход первого элемента ИЛИ, к входам которого подключены выход первого и выход третьего формирователей коротких импульсов, к вхо- 10 дам второго элемента ИЛИ подключены выход второго и выход третьего формирователей коротких импульсов, а к входам третьего элемента ИЛИ вЂ” выход первого формирователя коротких импульсов, вход 15 которого является входом контролируемого сигнала, от л и ч а ю щ ее с я тем, что, с целью расширения функциональных возможностей путем обеспечения допускового контроля скорости изменения периода сиг- 20 нала с возможными помехами при надежном обнаружении пропадания сигнала, в него введены первый, второй и третий интеграторы, первый и второй пороговые элементы, причем выход первого формирователя коротких импульсов подключен к входу четвертого формирователя коротких импульсов и к управляющим входам второго и третьего интеграторов, первые входы которых являются соответственно четвертым и пятым входами устройства, вторым и третьим входами которого являются соответственно второй и первый входы первого интегратора, управляющий вход которого подключен к инверсному выходу четвертого формирователя коротких импульсов, а выход — к вторым входам первого и третьего интеграторов, выходы которых подключены соответственно к входу первого и второго пороговых элементов, инверсные выходы которых подключены соответственно к входу второго и входу третьего формирователей коротких импульсов, 1698815

Составитель E.Ñoëoâüåâ

Техред М,Моргентал Корректор Э.Слиган

Редактор Ю.Середа

Производственно-издательский комбинат "Патент", г; Ужгород, ул,Гагарина, 101

Заказ 4393 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5