Патент ссср 169887

Иллюстрации

Показать всеРеферат

О П И С А Н И Е l69887

ИЗОБР ЕТЕ НИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 14 1.1963 (№ 813545/26-24) Кл. 42m, 14юз с присоединением заявки №

Приоритет

Государственный комитет по делам изобретений и открытий СССР

МПК G 061

УДК 681.14(088.8) Опубликовано 17.lll.1965. Бюллетень № 7

Дата опубликования описания 2Х1.1965

Авторы изобретения

А. Н. Бойко, В. В. Городецкий, В. П. Сигорский, Л. С. Ситников,,-,, ", и Л. Л. Утяков I

° l (Заявитель

СУММАТОР

Подписная группа № 174

Известны сумматоры, содержащие хронотроны, логические схемы «И» и «ИЛИ», схемы формирования переноса.

Предлагаемый сумматор отличается, тем что хронотрон запоминания разряда первого слагаемого подсоединен к хронотрону запоминания второго слагаемого и к схеме «ИЛИ» суммирования длительности первого слагаемого с единичной длительностью переноса, выход которой подсоединен к хронотрону для запоминания второго слагаемого, а также к схеме

«ИЛИ» суммирования длительности первого слагаемого с единичной длительностью переноса, Выход этой схемы подсоединен к схеме

«ИЛИ» суммирования длительности слагаемых и переноса и к схеме «И» выделения разности суммы и основания системы счисления, которые подсоединены к выходу хронотрона запоминания второго слагаемого. Выход схемы суммирования длительностей слагаемых и переноса подсоединен к логической схеме формирования переноса и к схеме «ИЛИ» развязки, второй вход которой соединен со схемой «И», а ее выход подключен к хронотрону запоминания суммы.

Предлагаемый сумматор дает возможность суммировать числа, р азряды которых представлены во время-импульсной форме с произвольным основанием системы счисления.

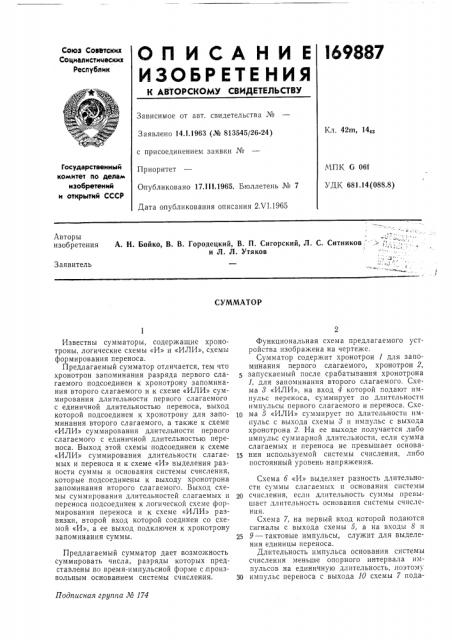

Функциональная схема предлагаемого устройства изображена на чертеже.

Сумматор содержит хронотрон 1 для запоминания первого слагаемого, хронотрон 2, запускаемый после срабатывания хронотрона

1, для запоминания второго слагаемого, Схема 8 ««ИИЛЛИИ»», на вход 4 которой подают импульс переноса, суммирует по длительности импульсы первого слагаемого и переноса. Схе10 ма 5 «ИЛИ» суммирует по длительности импульс с выхода схемы 8 и импульс с выхода хронотрона 2. На ее выходе получается либо импульс суммарной длительности, если сумма слагаемых и переноса не превышает основа15 ния используемой системы счисления, либо постоянный уровень напряжения.

Схема б «И» выделяет разность длительности суммы слагаемых и основания системы

20 счисления, если длительность суммы превышает длительность основания системы счисления.

Схема 7, на первый вход которой подаются сигналы с выхода схемы 5, а на входы 8 и

25 9 — тактовые импульсы, служит для выделения единицы переноса.

Длительность импульса основания системы счисления меньше опорного интервала импульсов на единичную длительность, поэтому

30 импульс переноса с выхода 10 схемы 7 пода169887

Предмет изобретения д 9

Составитель В. Субботин

Текред Т. П. Курилко Корректор О. Ь. Тюрина

Редактор П. Шлаин

Заказ 1023/12 Тира>к 950 с1>ормат бум. 60>(90 /8 Объем 0,16 изд. л. Цена 5 коп.

Цг1ИИПИ Государственного комитета по делам изобретений и открытий СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2

Ьт на следующий разряд в течение этого промежутка времени.

Схема 11 «ИЛИ» служит для развязки выходов схем б и б. Напряжение с выхода этой схемы подают на хронотрон 12, запоминающий сумму.

Достоинством предлагаемого сумматора по сравнению с известными, например десятичными сумматорами, является большая помехоустойчивость и надежность его работы при сравнительной простоте схемы. Предлагаемый сумматор может найти применение в различных системах обработки информации, например в малых вычислительных машинах, электронных арифмометрах, телеметрических устройствах.

Сумматор, содержащий хронотроны, логические схемы «И» и «ИЛИ» и схему формирования перейоса, отличающийся тем, что, с целью суммирования чисел, разряды которых представлены во время-импульсной форме с произвольным основанием системы счисления, 5 хронотрон запоминания разряда первого слагаемого подсоединен к хронотрону запоминания второго слагаемого, а также к схеме

«ИЛИ» суммирования длительности первого слагаемого с единичной длительностью nepelo носа, выход которой подсоединен к схеме

«ИЛИ» суммирования длительности слагаемых и переноса и к схеме «И» выделения разности суммы и основания системы счисления, которые подсоединены к выходу хронотрона

15 запоминания второго слагаемого, выход схемы суммирования длительностей слагаемых и переноса подсоединен к логической схеме формирования переноса и к схеме «ИЛИ» развязки, второй вход которой соединен со схемой

20 «И», а ее выход подключен к хронотрону запоминания суммы.