Устройство синхронизации с фазовой автоподстройкой частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и может быть использовано в аппаратуре синхронизации цифровой сети связи. Целью изобретения является повышение помехоустойчивости. Устройство содержит синтезатор частоты, образованный опорным генератором 1, первым 2 и вторым 7 делителями с переменным коэффициентом деления, импульсно-фазовый детектор 3, фильтр нижних частот 4, управляющий аяемент 5 и управляемый генератор 6, цифровой фазовый детектор 8, усреднитель 9, первый и второй умножители 10 и 11, первый и второй сумматоры 12 и 13, регистр 14, реверсивный счетчик 15, дешифратор 16 нулевого состоя ния,Р5-триггер 17, инвертор 18, пеовый и агорой элементы И 19 и 20, первый и второй делители 21 и 22 частоты. Выходной сигнал управляемого генератора 6 сравнивается по фазе с входным в цифровом фазовом детекторе 8, а код рассогласования фаз подвергается фильтрации с помощью усреднителя 9 и астатического фильтра на первом 10 и втором 13 сумматоре и регистре 14 и далее управляет подстройкой фазы синтезатора . Цель изобретения достигается путем распределения команд управления по паоиоду дискретизации с помощью реверсивного счетчика 15, дешифратора 16 нулевое гс состояния, RS-триггера 17, инвертора 18 и двух элементов И 19 и 20. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ((9) () () (я)5 Н 03 (7/06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

6(.«4," 1 4В6

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДETEllLC7Ð / (21) 4608928/09 (22) 28,11.88 (46) 23,12.91. Бюл. М 47 (72) Е.B. Зильберг и М.Н. Колтунов (53) 621.396.666(088.8) (56) Авторское свидетельство СССР

N 1215185, кл, Н 04 (7/04, 03.05,84, (54) УСТРОЙСТВО С )(РО ЗАЦ 4

ФАЗОВОЙ АВТОПОДСТРОЙКОЙ ЧАСТОТЫ (57) Изобретение относится к электросвязи и может быть использовано в аппаратуре синхронизации цифровой сети связи.

Целью изобретения является повышение помехоустойчивости. Устройство содержит синтезатор частоты, образованный опорным генератором 1, первым 2 и вторым 7 делителями с переменным коэффициентом деления, импульсно-фазовый детектор 3, фильтр нижних частот 4, управляющий зммент 5 и управляемый генератор 6, цифровой фазовый детектор 8, усреднитель 9, nep",.ûé и второй умножители 10 и 11. первый и второй сумматоры 12 и 13, регистр 14, реверсивный счетчик 15, дешифратор 16 нулевого состояния,RS-триггер 17, инвертор 18,. пеовый и второй злементы И 19 и 20, первый и второй делители 21 и 22 частоты. Выходной сигнал управляемого генератора 6 сравнивается по фазе с входным в цифровом фазовом детекторе 8, а код рассогласования баз подвергается фильтрации с помощью усреднителя 9 и астатического фильтра на первом 10 и втором 13 сумматоре и регистре

14 и далее управляет подстройкой фазы синтезатора. Цель изобретения достигается путем распределения команд управления по пеоиоду дискретизации с помощью реверси .,ого счетчика 15, дешифратора 16 нулево- гс состояния, RS-триггера 17, инвеотора 18 и двух элементов И 19 и 20. 1 ил.

Изобретение относится к электросвязи и может быть использовано в аппаратуре синхронизации цифровой сети связи, Целью изобретения является повышение помехоустойчивости.

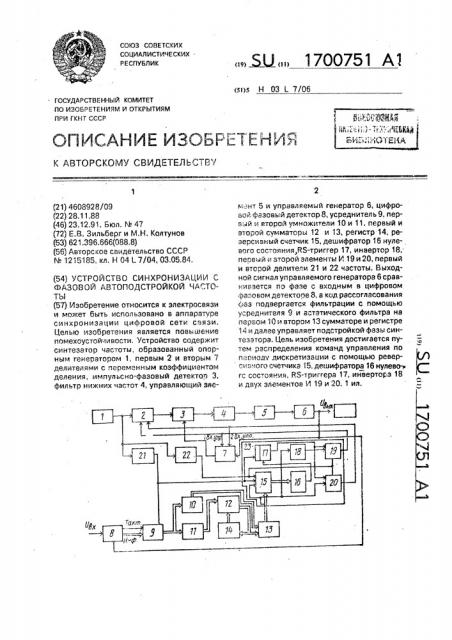

На чертеже изображена структурная электрическая схема устройства.

Устройство содержит Опорный генератор 1, первый делитель 2 частоты с переменн ы м к о эффи цие н том делен ия (Д П КД), импульсно-фазовый детектор 3, фильтр 4

,нижниМ частот, управляющий элемент 5, vr(, равляемый генератор 6, второл ДПКД 7, цифровой фазовый детектор 8, усреднитель

9, первый 10 и второй 11 умнох<ители, пер вый 12 и второй 13 сумматоры, регистр 14, (реверсивный счетчик 15, дешифратор 16 ну;левого состояния, RS-триггер 17, инвертор

18, первый 19 и второй 20 элементы И, пер вый 21 и второй 22 делители частоты, Устройство работает следующим образом.

В отсутствие команд управления коэффициентами деления ДПКД 2 и 7 совокупность блоков 1 — 7 представляет собой синтезатор фиксированной частоть(, требуемый для хронирования сети связ(л, Цифровой фазовый детектор 8 вырабатывает код. соответствующий разности фаз Входного и

Выходного сигналов. Усреднитсль 9 осушзствляет усреднение этой величины на интервале времени, являющемся периодом дискретизации (определяется коэффициек1ом деления делителя 21), который на к-:.(;Koil(K0 порядков преВыша6т постоянку(О ьреМЕНИ СИНтЕЗатсра ЧаСтотЫ. ДаЛЕЕ СИГНаЛ фильтруется в астатическом цифрово(.:. фильтре, образованном пропорциональным (первый умножитель 10) и интегрирующим (второй умножител ь 11 л накопительный сумматор на первом сумматоре 12 и регистре 14) каналами управления, коды с которых суммируются ВО втором сумматоре 13. В результате Вь(рабать(вает ; . значение приращения фазы выходного сиг" нала, которое должно быть осуществлено HB данном периоде дискретизации.

Данное приращение осуществляется посредс вом подачи на ДПКД 2 и 7 соответствующего числа команд изменения коэффициентов деления. Принцип отрабо Гки возмущений, вносимых В синтезатор частоты при изменении на фиксированное время коэффициентов деления ДПКД 2 и 7 в уст. ройстве в точности совпадает с описанным в известном устройстве. Вследствие того, что период дискретизации намного больше постоянной времени синтезатора, имеется возможность последовательной подачи команд управления с такой частотой, что =

10 ф У (25

Р

F ,4 моменту подачл каждой последующей команды фаза Выходного сигнала изменяется на один дискрет подстройки путем предыдущей команды управления. Нужная частота подачл команд управления коэффициентами деления обеспечивается вторым деллтелем 22, .",ам О распределение команд уп ра аления по периоду дискретизации Осуществляется следующим Образом, ПО сигналу инициализации с парного делителя 21 В реверсив(чь(Й счетчик 15 запиcI,IaB6Tca входная информация, модуль (;Оторой раве:I числу команд управления, которые требуется Выработать HB данно(..; периоде дискретизации, а старший разряд несет информациго о знаке и ooçòoìó управляет Выбором одного из элементов (119 «20 направлением счета рев6рсиВнОГО счетчика ! 5, Кроме ТОГО, сиГнал иь(ициал(,зации уста" нээлиВает ЯЯ-Tp!i(rrep 17, что gael Возможность элементу И, Выбранному старшим разрядом сигнала Второго сумматора !3,, r.pGrIycxBT(HB соо(нетствующи(л выход импульсы, пост Jпаvо(цие на треть(4 Входы первого 19 и Второго 20 элементов И с второго дслителя 22. Зти импульсы, пост (пая также на счетный Вход ревepc(iaкого с ет:,ика 15, доводят В Ko! IUe концов его содержимое до нуля. что Обнаруживает де(((ифратор 16, который сбрасывает RS-триггер 17, прекращая тем самым дальнейшую выдачу команд управления. Таким образом, блоки 15 — 18 представляют собой преобразователь кода

В ЧИСЛО ИМПУЛЬСОВ, КОТОРЬ(8 ПОДВЮТСЯ HB один из Входов управления ДПКД2 и 7 через коммутатор ка элементах (1 19 и 20. За счет ра.".пределения подстройки синтезатора по

i= ceìii периоду дискретизации (нирика спектра флуктуаций фазь(его Выходного сигнала умень(((ается, что и обусловл1лвает ул чшеHvI8 помехоустойчивости, с((г р и у л à,; э о б р 6 т н и Я

"стйойстВО сии pe(-:(; лзаци ",, с фа.л нгiv;

ВВТОПОВСТРОАКОЙ i(BrTOT(;i CGB6P>KBL :86 ПО

СледоьатеЛЬКО СОЕДИНВНКЫЕ ОПОрКЬ(Й ГЕНЕpBTGG, Пер БЫЙ ДВЛИ reriь ЧВСТО rÛ С перемен((ым .::Озффициектом дбле(чля, имГ(,(,;I,cHo-фазовый дете(тор, фильтр H(i Hих (астот, управ (яющий B(le(i (6HT, управляемый генератор и цифровол фазовый дете(стОР, BTGPGA Вход !;"GTGPorО ЯвляетсЯ ВхОДОм у -TpGIAcTBB, 3 таюхе делитель -!астОты с пеОеме"!ным коэффицие(тс(м деления, Выход д Оч" О P G I G Г О ",P i l H 6 H (e TO O!=4 V. ВХ ОД О ° l .л 4 I VЛ (, с(-(О-Фазовогодетектора, О (л и ; а ю (486ся

ТВМ., ЧТО, С цель(О ПОВЫШОНИЯ ПОМВХОУСТОЙ-!!1BocT(a, В н8ГО Введены последовательно соединенные усреднитель, первый умкожитель, перьый и второй сумматоры, Второй

1700751

Составитель В.Козлов

Техред M,Моргентал

Корректор О.Кравцова

Редактор H.Áoáêoâà

Заказ 4477 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1 13035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 умножитель, включенный между выходом усреднителя и вторым входом второго сумматора, регистр, включенный между выходом и вторым входом первого сумматора, реверсивный счетчик, дешифратор нулево- 5 го состояния, RS-триггер, инвертор, первый и второй элементы И, при этом тактовый вход усреднителя соединен с тактовым выходом цифрового фазового детектора, аго информационный вход — с информациан- 10 ным выходом цифрового фазового детектора, а его вход сброса, вход записи реверсивного счетчика и S-вход RS--;ðíããàpa — с выходом первого делителя частоты, вход которого и вход второго делителя час- 15 таты подключены к выходу опорнага генератора, информационные входы реверсивного счетчика соединены с выхадом второго сумматора, его вход направления счета, первый вход второго элемента И и вход инвертора — с выходом старшего разряда второго сумматора, а его тактовый вход, первый вход первого элемента И и второй вход второго элемента И вЂ” с выходам второго делителя частоты, выход реверсивного счетчике: рез дешифратор нулевого состояния подключен к R-входу RS-триггера, выход которого соединен с вторим входам первого элемента И и третьим входом второго элемента И, выход инвертара соединен с третьим входам первого элемента

И. а выходы первого и второго элементов И ссединены соответственно с первым и вторым управляющи;ли входами первого и второго делителей частоты с пеоеменным коэффициентом деления.