Устройство временной коммутации асинхронных цифровых сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой .связи и может быть использовано в, электронных системах коммутации. Цель - повышение точности приема и коммутации сигналов за счет исключения возможности их потери. Устр-во содержит блок 1 накопления служебных сигналов, блок 2 первичной памяти, блок 3 коммутации и памяти служебных сигналов, два регистра 4 и 8, блок 5 вторичной памяти, блок 6 сравнения, мультиплексор 7, блок 9 распределения сигналов. Блок 1 имеет п ячеек памяти. Каждая входящая линия связи имеет свою временную позицию АИМ и свою ячейку памяти в блоке 1. Блок 1 производит выделение служебной информации из общего потока информации в АИМ. Служебные сигналы, которые необходимо выдать -в исходящие линии связи, записываются в ячейки блока 3. Считывание сигналов из блока 3 и выдача их в блок 2 производится циклически и побитно. 1 ил. о 8 (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (1) Н 04 М 9/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A ВТОРСНОМУ СВИД=ТЕЛЬСТБУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4757033/09 (22) 04.08.89 (46) 23.12.91.Бюл. К-* 47 (72) В.П.Чуркин (53) 621.395 .4 (088.8) (56) Авторское свидетельство СССР

У 773955, кл. Н 04 М 9/00, 1979. (54) УСТРОЙСТВО ВРЕМЕННОЙ КОММУТАЦИИ

АСИНХРОННЫХ ЦИФРОВЫХ СИГНАЛОВ (57) Изобретение относится к цифровой связи и может быть использовано в, электронных системах коммутации.

Цель - повьппение точности приема и коммутации сигналов за счет исключения возможности их потери. Устр-во содержит блок 1 накопления служеб„„SU„,, 1700762 А1

2 первичнои памя блок 3 коммутации и памяти служебных сигналов, два регистра 4 и 8, блок 5 вторичной памяти, блок 6 сравнения, мультиплексор 7, блок 9 распределения сигналов. Блок 1 имеет п ячеек памяти.

Каждая входящая линия связи имеет свою временную позицию АИМ и свою ячейку памяти в блоке 1. Блок 1 производит выделение служебной информации из общего потока информации в

АИМ. Служебные сигналы, которые необходимо выдать -в исходящие линии связи, записываются в ячейки блока 3.

Считывание сигналов из блока 3 и выдача их в блок 2 производится цикли« а чески и побитно. 1 ил. 9.

1700762 сигнала из i-й ячейки памяти. Блок 1 производит вьделение служебной информации из общего потока информации в АИИ и выдает служебные сигналы вместе с адресами входящих ли1 ний связи, по которым поступают сигналы.

Служебные сигналы, которые необходимо вьдать в исходящие линии связи, записываются в ячейку памяти блока 3. Служебные сигналы поступают в сопровождении адресов исходящих линий„ которые соответствуют адресам ячеек памяти блока 3. Вместе со служебными сигналами в ячейки памяти блока 3 записывается также сигнал фБ = 1. Считывание сигналов из блока

3 и вьдача их в блок 2 производится циклически и побитно. За один цикл работы блока 3 выдается по одному биту. для каждой из обслуживаемых исходящих линий связи. В блок 2 для

i-й исходящей линии вьдается из бло" ка 3 один бит служебного сигнала и сигнал oL = 1, который запрещает запись в i-ю ячейку памяти блока 2 информации из АИИ и обеспечивает запись в эту же ячейку памяти бита слуго кода времени. Выдача служебных сигналов в исходящие линии связи производится циклически, Для прекращения вьдачи служебных сигналов в исходящие линии связи в ооответствун щие ячейки памяти блока 3 заносится сигнал М = 0;

Информация иэ ячеек памяти блока 2 считывается циклически и выдается через первый регистр 4 на вход блока 5. При этом бит информации из

i-й ячейки памяти блока 2 вьдается также на блок 6, на который поступает бит информации из i-й исходящей линии через мультиплексор 7, т.е.. тот бит информации, который ранее бып выдан в i-ю линию и записан в блоке 9.

Если эти биты были одинаковы, например равны "1" или "0", блок 6 вырабатывает сигнал = 1, который запрещает запись новой информации в i-ю ячейку памяти блока 5, так как пре-дьдущий бнт информации (противоположной полярности) в данном случае еще не вьдан из блока 5 в исходящую линию.

До тех пор пока предыдущий бит не выдан иэ i-й ячейки памяти блока 5 в

i-ю исходящую линию, сигнал ф =1 запрещает запись новой информации в

Изобретение относится к цифровой связи и может быть использовано в электронных системах коммутации.

Цель изобретения — повышение точЪ ности приема и коммутации сигналов за счет исключения их потери.

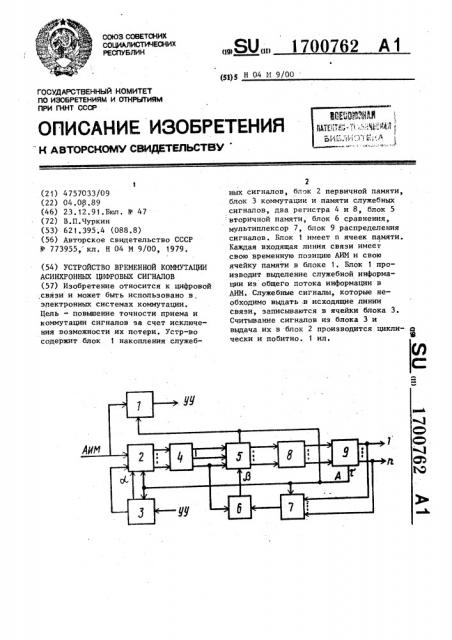

На чертеже изображена структурная электрическая схема устройства временной коммутации асинхронных цифро- 10 вых сигналов.

Уатройство временной коммутации асинхронных цифровых сигналов содер жит блох 1 накопления служебных сигналов, блок 2 первичной памяти, блок 15

3 коммутации и памяти служебных сигналов, первый регистр 4, блок S вто .-. ричной памяти, блок 6 сравнения, мультиплексор 7, второй регистр 8, блок 9 распределения сигналов. 2р

Устройство временной коммутации . асинхронных цифровых сигналов работает следующим образом.

По адресно-информационной магист,рали (АИИ) параллельным кодом посту- 25 пает информация в сопровождении адресов (номеров) исходящих линий связи, которым эта информация принадлежит. Информация представляет собой коды фронтов коммутируемых сигналов, 30 жебного сигнала из блока 3 и нулево— и код времени, определяющий моменты, времени вьдачи сигналов в исходящие линии связи.

При этом кодом "1" кодируется пе- . редний фронт "единичного" (1) сигча= ла, а кодом "0" — задний фронт.

Блок 2 принимает слова н, исполь- зуя адрес линий связи, записывает информацию.в соответствующие ячейки памяти.. При этом каждая исходящая ли- щ0 вия связи имеет свою ячейку в блоке

2. Номера линий связи.и ячеек памяти совпадают.

Служебные сигналы, поступающие на входы коммутационной системы из других станций сети связи, передаются в блок 1, который имеет п ячеек памяти

Каждая входящая линия связи коммутационной системы имеет свою временную позицию АИИ и свою ячейку памяти в блоке 1 накопления служебных сигналов.

Номера временных позиций AHN„ ÿ÷ååê памяти блока 1 и входящих линий связи р совпадают. В ячейках памяти блока 1 производится побнтное накопление служебных сигналов, Блок 1 за время, равное одной временной позиции ANN, осуществляет операцию считывания и записи одного и того же служебного

1700762

Составитель А.Микуцкий

Редактор Н.Бобкова Техред-Л,Олийнык

Корректор С.Некмар

Заказ 4478 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,101 эту ячейку памяти. Таким образом, исключается потеря битов информации.

После выдачи этого бита сигнал =Q.

В этом случае новый сигнал записан из д-й ячейки блока 2 в i-ю ячейку блока 5 вторичной памяти.

Блок 9 циклически считывает информацию из ячеек блока 5 и производит сравнение кода времени КВ, сопровождающего информацию иэ блока 5 с кодом времени КВ, вырабатываемым блоком 9.

Если эти коды времени .одинаковые, то блок 9 определяет номер исходящей линии связи, в которую необходимо вы- 1g дать поступивший бит информации. Ес ли коды KS и КВ времени не равны, то с помощью сигнала = 0 выдача поступившего из блока 5 через второй регистр 8 (фиг.1) очередного бита ин-.20 формации запрещается.

Формула из обретения

Устройство временной коммутации асинхронных цифровых сигналов, содер- 5 жащее блок накопления служебных сигна-. лов, вход которого соединен с первым входом блока первичной памяти, второй и третий входы которого соединены соответственно с первым и вторым выхо-.30 дами блока коммутации и памяти служебных сигналов, а также блок распределения сигналов, о т л и ч а ю щ е е с я тем, что, с целью повышения точности приема и коммутации сигналов за счет исключения возможности их потери,введены последовательно соединенные первый регистр, блок вторичной памяти и ,второй регистр, а также последовательно соединенные мультиплексор и блок сравнения, выход которого соединен с вторым входом блока вторичной памяти, третий вход которого соединен с вторым выходом первого регистра и вторым входом блока сравнения, причем выход блока первичной памяти соединен с входом первого регистра, а выход второго регистра соединен с входом блока распределения сигналов, первый выход которого соединен с вторым входом блока накопления служебныхсигналов, четвертым входом блока вторичной памяти, первым входом мульти.плексора, входом блока коммутации и памяти служебных сигналов и четверTbIH входом блока первичной памяти, а выход блока распределения сигналов соединен с вторьМ входом мультиплексора.