Патент ссср 170212

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

l7O 212

Союз Советских

Социалистических

Республик

Зависимое от авт, свидетельства №

Заявлено 10.1П.1964 (№ 885770/26-24) с присоединением заявки ¹

Приоритет

Опубликовано 09.1У.1965. Бюллетень ¹ 8

Дата опубликования описания 8Л .1965

Кл. 42m, 14йз

МПК б 06f

УДК 681.14(088.8) Государственный комитет по делам изобретений и открытий СССР

А. П. Вишневский, A. А. Койфман, В. Н. Сигорский, Л. С. Ситников и Л. Л. Ут11КОВ.Ф. - .

" !!,"!

Институт математики Сибирского отделения АН ССС, Авторы изобретения

Заявитель

r. -, .-i r

Ъ !

НАКОПИТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР

Подписная группа Л 174

Известны накопительные десятичные сумматоры, содержащие триггеры, кл1очи и схемы «ИЛИ».

Предложенный десятичный сумматор отличается тем, что В нем к динамическому Входу фазо-импульсного элемента памяти подключена схема «ИЛИ», подсоединенная к источнику опорных нулевых импульсов и к датчику импульсов числа. Нулевой вход триггера устройства преобразования фазы в число импульсов подключен к источнику импульсов второго слагаемого, его единичный вход подключен к источнику опорных нулевых импульсов, выход триггера подсоединен к одному из входов схемы совпадения, два других входа которой подключены к выходу разрешения сложения и к источнику тактовых импульсов, сдвинутых на половину периода высокого такта. Выход схемы совпадения подсоединен к одному из входов схемы «ИЛИ», два других входа которой подключены к источнику тактовых импульсов и к выходу схемы переноса предыдущего разряда. Выход схемы «ИЛИ» подсоединен к счетному входу фазо-импульсного элемента, первый выход которого подключен к нулевому входу триггера схемы переноса. Единичный вход триггера подключен к источнику импульсов, сдвинутых на половину периода тактОВых импульсоВ Относительно опорных нулевых импульсов, а выход триггера подключен и 11ервому входу схемы «1т», второй вход которой подключен ко Второму выходу фазо-импульсного элемента. Это позволяет построить сумматор на фазо-импульс5 ном элементе и уменьшить его стоимость.

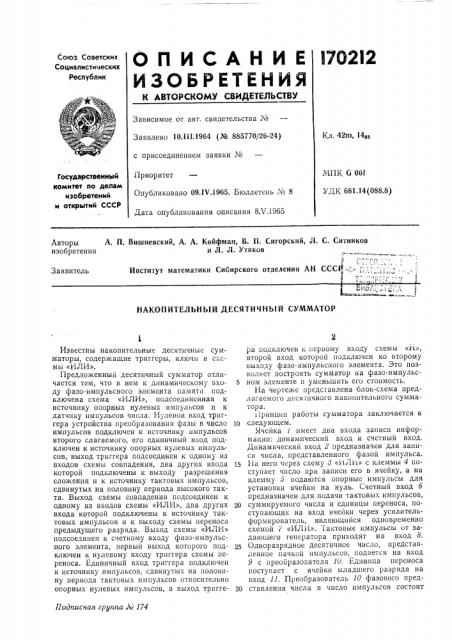

На чертеже представлена блок-схема предлагаемого десятичного накопительного сумматораа.

11ринцпп работы сумматора заключается в

10 следующем.

Ячейка i имеет два входа записи информации: динамический вход и счетный вход.

Динамический вход 2 предназначен для записи числа, представленного фазой импульса.

15 I.ia него через схему 8 «1 1ЛИ» с клеммы 4 поступает число при записи его в ячейку, а на клемму 5 подаются опорные импульсы для установки ячейки на нуль. Счетный вход 6 предназначен для подачи тактовых импульсов, 20 суммируемого числа и единицы переноса, поступающих на вход ячейки через усилительформирователь, являющийся одновременно схемой 7 «ИЛИ». Тактовые импульсы от задающего генератора приходят на вход 8.

25 Одноразрядное десятичное число, представленное пачкой импульсов, подается на вход

9 с преобразователя 10. Единица переноса поступает с ячейки младшего разряда на вход 11. Преобразователь 10 фазового пред30 ставления числа в число импульсов состоит

170212 из триггера 12 и трехвходовой схемы совпадения 18 «И». На вход 14 триггера поступают импульсы с фазой второго слагаемого, а на вход 15 триггера — опорная последовательность импульсов. Таким образом, на входе 16 схемы совпадения 18 «И», присоединенном к выходу 17 триггера 12, цифра представляется длительностью импульсов. На вход 18 схемы

18 «И» подается последовательность импульсов, сдвинутых на половину периода высокого такта относительно опорного. На вход 19 схемы 18 «И» подается стробирующий импульс, разрешающий сложение и действующий в течение одного периода опорных импульсов.

Процесс суммирования происходит в фазоимпульсной ячейке 1. Пусть в ячейке записано число А (0(А (9). Прибавим число В. Если

А+В<10, то в течение такта сложения на выходе 20 ячейки 1 появляется только один импульс сброса, который поступает на вход

21 схемы 22 «И». На вход 28 схемы 22 «И» поступает с выхода 24 триггера 25 низкий потенциал, так что на выходе 26 схемы 22 «И» нет импульса переноса. Импульс на выходе

27 ячейки 1 следует после окончания импульса на выходе 20 и поступает на вход 28 триггера 25. Триггер 25 возвращается в исходное положение импульсами, сдвинутыми на половину периода тактовых импульсов относительно опорной нулевой последовательности импульсов. В ячейке 1 остается записанным число А+В.

Если А+В)10, то в течение такта сложения на выходах 20 и 27 ячейки 1 появляются по два импульса. Первый импульс с выхода

20 не проходит через схему 22 «И», но первый импульс с выхода 27 подготавливает триггер 26.

Второй импульс с выхода 20 проходит через схему 22 «И», так как на вход 28 схемы

22 «И» подается высокий потенциал с выхода

24 триггера 25 и появляется на выходе 26, поступая на следующий.

В фазо-импульсной ячейке остается записанным число А+ — 10. Предлагаемый сумматор может быть использован в настольных вычислительных машинах.

Предмет изобретения

1О Накопительный десятичный сумматор, содержащий триггеры, ключи и схемы «ИЛИ», отличающийся тем, что, с целью построения сумматора на фазо-импульсном элементе и уменьшения его стоимости, в нем к динамиче15 скому входу фазо-импульсного элемента памяти подключена схема «ИЛИ», подсоединенная к источнику опорных нулевых импульсов и к датчику импульсов числа; нулевой вход триггера устройства преобразования фа20 зы в число импульсов подсоединен к источнику импульсов второго слагаемого, его единичный вход подключен к источнику опорных нулевых импульсов, выход триггера подсоединен к одному из входов схемы совпадения, два дру25 гих входа которой подключены к выходу разрешения сложения и к источнику тактовых импульсов, сдвинутых на половину высокого такта, выход схемы совпадения подсоединен к одному из входов схемы «ИЛИ», два друЗО гих входа которой подключены к источнику тактовых импульсов и к выходу схемы переноса предыдущего разряда, выход схемы

«ИЛИ» подключен к счетному входу фазоимпульсного элемента, первый выход фазоЗ5 импульсного элемента подключен к нулевому входу триггера схемы переноса, единичный вход триггера подключен к источнику импульсов, сдвинутых на половину периода тактовых импульсов относительно опорных нулевых

40 импульсов, выход триггера подключен к первому входу схемы «И», второй вход которой подключен ко второму выходу фазо-импульсного элемента.

170232

Составитель В. Субботин

Редактор П. Шлаин Техред А. А, Камышиикова Корректор О. Б. Тюрина заказ 899/3 Тираж 950 Формат бум. 60;к,90 /q Объем 0,27 изд. л. Цена 5 кон.

ЦНИИПИ Государственного комитета по делам изобретений и открытий СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2