Устройство для контроля погрешности отработки шага шагового двигателя

Иллюстрации

Показать всеРеферат

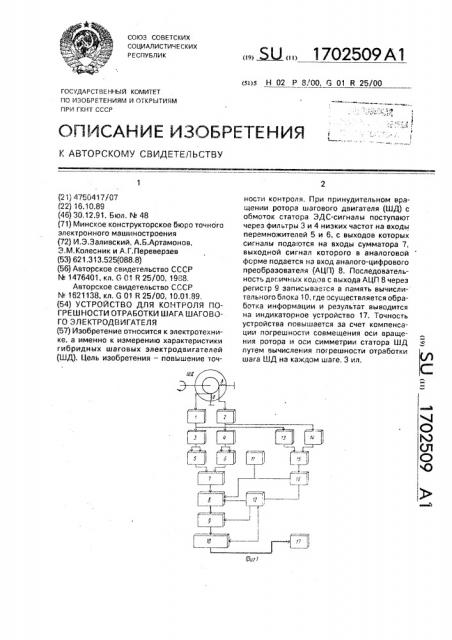

Изобретение относится к электротехнике , а именно к измерению характеристики гибридных шаговых электродвигателей (ШД). Цель изобретения - повышение точности контроля. При принудительном вращении ротора шагового двигателя (ШД) с обмоток статора ЭДС-сигналы поступают через фильтры 3 и 4 низких частот на входы перемножителей 5 и 6, с выходов которых сигналы подаются на входы сумматора 7. выходной сигнал которого в аналоговой форме подается на вход аналого-цифрового преобразователя (АЦП) 8. Последовательность дрг ичных код IB с выхода АЦП 8 через регистр 9 записываемся в память вычислительного блока 10. где осуществляется обработка информации и результат выводится на индикаторное устройство 17. Точность устройства повышается за счет компенсации погрешности совмещения оси вращения оотооа и оси симметрии статора ШД путем вычисления погрешности отработки шага ШД на каждом шаге. 3 ил. Ј XI О ГО ел о ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21> 4750417/07 (22) 16.10.89 (46) 30. !2.91. Бюл, № 48 (71) Минское конструкторское бюро точного электронного машиностроения (72) И,Э.Заливский, А.Б.Артамонов, Э,M,Êîëåñíèê и A.Ã,Ïåðeâåðçåâ (53) 621.313.525(088.8} (56} Авторское свидетельство СССР № 1476401, кл. 6 01 R 25/00, 1988.

Авторское свидетельство СССР

¹ l621138, кл. G 01 R 25/00, 10.01,89, (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОГРЕШНОСТИ ОТРАБОТКИ ШАГА ШАГОВОГО ЭЛЕКТРОДВИГАТЕЛЯ (57) Изобретение относится к электротехнике, а именно к измерению характеристики гибридных шаговых электродвигателей (ШД). Цель изобретения — повЫшение точ«.. Ж 1702509 А1 (я)5 Н 02 Р 8/00, G 01 К 25/00 ности контроля. При принудительном вращении ротора шагового двигателя (ШД) с обмоток статора ЭДС-сигналы поступают через фильтры 3 и 4 низких частот на входы перемножителей 5 и 6, с выходов которых сигналы подаются на входы сумматора 7, выходной сигнал которого в аналоговой форме подается на вход аналого-цифрового преобразователя (АЦП) 8. Последовательность двг;ичных кодов с выхода АЦП 8 через регистр 9 записывается в память вычислительного блока 10, где осуществляется обработка информации и результат выводится на индикаторное устройство 17. Точность устройства повышается за счет компенсации погрешности совмещения оси вращения ротора и оси симметрии статора ШД путем вычисления погрешности отработки шага ШД на каждом шаге. 3 ил.

1702509

ИЛИ 15 соответственно, где преобразуются в одну последовательность прямоугольных, импульсов на частоте 2м, Сигнал с выхода элемента ИСКЛКЗЧАЮ(ЦЕЕ ИЛИ 15 поступает нг второй вход БИГД 16., который фоомирует на выходе последовательность 5 прямоугольных импульсов с длительностью .= С,.". Т<, где Т; — период ГТИ 11, и частотой.

2й». Это достигается тем, что выход "ТИ 1": подключен к первому входу БИГД 16. Временное Оасположение этих импульсов ссот- 10 ветствует нулевым значениям напряжения входных ЭДС-сигналов. Сигнал с выхода

:=»ИГД 16 поступает на первый вход блока I2 управления, где по входному си-налу фсрмируется сигнал "Запуск АЦП", поступаю- 15 щий через первь;и выход блока 12 управления на третий вхсд АЦП 8, После записи по входу регистра двоичного кода блок 12 управления устанавливает на шине обмена данных флаг готовности данных в 20 регистре 9.

По получении сигнала готовности данных BE 10 устанавливает на шине обмена данных сигнал чтения данных и считывается код с выхода регистра через информацион- 25 ный вход, После считыванця кода ВБ 1« устанавливает сигнал оконч: ия считыв:ния, по которому выход регистр - 9 устанавливается в нулевое положение и снимается флаг готовности данных блока 12 управле- 30

H!»Ig, Вычислительный блок 10 работает следующим образом.

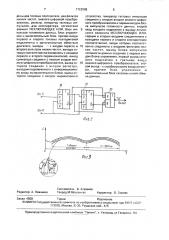

После одного оборота ротора ШД в памяти ВБ 10 находится N. значений 35 (AMAH! Амакц j (фиг. 3). Погрешность отработки каждого»-го шага определяют по формуле

Амакс(— Амин

Амакс(+ Амин) () 10 где А - амплитуда ЭДС на каждом шаге, и получают совокупность значений (Л Xj ) .

Затем по программе, занесенной в память

ВБ 1С, статическую погрешность отработки 45 шага ШД определяют по формуле

Лг() = 1/2(ЛХмакс+ Л Хмин) . 100 (2)

Результат вычислений выводят на индикаторное устройство 17, Из совокупности пар чисел (Амакц, Амин,. j определяют ЬХ,кц для выходного сигнала сумматора 7 на участке

ИЗМЕНЕНИЯ СИГНаЛа ОТ Амин! ДО

Амакс + 1 а Хмин, определяют на учаCT!(8 ИЗМЕНЕния СИГНаЛа ОТ Амакс! + 1 ДО

Ами я -, -, согласно фиг. 3.

Наличия погрешности совмещения оси вращения ротора и оси симметрии статора

ШД приводит к тому, что выходной сигнал сумматора 7 имеет вид, представленный на фиг. 3. В этом случае не представляется возможным определить однозначно постоянную саставляющ »ю всего сигнала и тем самым точно определить погрешность отработки шага. Компенсация несовмещения осей вращения ротора и симметрии статора осуществляется тем, что погрешность отрабо-ки шага определяют на каждом!-м шаге по формул».: (1), а затем о фор .уле (2) рассч тывают ст;-.т..-ческую погрешность отработки единичного шага ШД.

ТочнОСТЬ КОНТРОЛЯ ПОГРЕШНОСТИ ТакжЕ повышае "cR "3:. «»;- T согласования ВХОдных цепей чстройстьа и шмоток ШД и фильтрации основной гармоники ЭДС.

Быстродей. гвие устройства контроля погрешности повышается за счет применения вычислительного блока О, который позволяет автоматически обрабо ать N nap кодов значений амплитудь сигнала сумматора 7 и вычислить с ат. ческую погрешность отработки шага.

БИГД 16 работает следующим образом.

На один вход БИГД 16 п,:т, пает сигнал от ГТИ 11 частотой F-., = 21 = кГц. а на другой вход — сигнал на удвоенной частоте следования ЭДС-сигналов Fr = 1 кГц, Схема IlO страена так, что выходной сигнал триггера

19 на выходах О " Q сдвинут на один период

ГТИ 11 па сравнению с выходным сигналом

»j и С. триггера 13, Четыре последовательности прямоугольных импульсов поступают на входь! элемента 2-И-И»1И-HF 20, в котором обрабатываются в соответствии с логикой преобразования на выходе которого формируется последовательность прямоугольных импульсов на частоте Fc =- 1 кГц с длительностью г = 1/(2- FT), Вычислительный блок 0 может быть выполнен в виде микроЭВ1А с контроллером сопряжения, а индига-орное устройство 17 — в в -;де дисплея, печатающего устр: йства и др.

Пре:.,ельная точность и быстродействие предлагаемо,о устройства определяются точностью аналого-цифрового преобразования и частотой генератора тактовых импульсов, При экспериментальной проверке легре UHGcTb устройства составила 30 угл, с.

«л ормула изобретения . . Стройство для контроля погрешности

o;:l=.6îгки шага ша-î.üàãñ дьигателя, содержащее два перемнояителя, сумматор, входы которого соединены с выходами перемножителей, и индикаторное устройство. Q т л и ч а Io щ е е с я тем, что, с целью повышения точности контроля, в него ввеОт О,Ф

« ф

/ оГоро

Г pGf770p V. (оставитель В, Алфимов

Редактор А, Лежнина Техред М,Моргентал Корректор В, Гирняк

Заказ 4550 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 дены два токовых повторителя, два фильтра низких частот, аналого-цифровой преобразователь, регистр, генератор тактовых импульсов, два компаратора, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, блок им- пульсов готовности данных, блок управления и вычислительный блок, причем входы первого и второго. токовых повторителей подключены к ортогональным обмоткам двигателя, выходы — к входам первого и второго фильтров низких частот, выходы которых соответственно соединены с входами первого и второго перемножителей, выход сумматора соединен с первым входом аналого-цифрового преобразователя, выход которого соединен с входом регистра, выходом подключенного к информационному входу вычислительного блока, выход которого соединен с входом индикаторного устройства, генератор тактовых импульсов соединен с вторым входом аналого-цифрового преобразователя и первым входом блока импульсов.готовности данных, второй

5 вход которого подключен к выходу логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первым и вторым входами соединенного с выходами первого и второго кампаратооов соответственно, входы которых соответст1Î венно "îåäèíåíû с входами фильтров низких частот, выход блока импульсов готовности данных соединен с первым входом блока управления, первый выход которого подключен к третьему входу

15 аналого-цифрового преобразователя, второй выход — к стробирующему входу регистра, причем блок . управления и вычислительный блок связаны шиной обмена данных.