Автоматический измеритель импульсной мощности свч - радиосигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиоизмерениям и может быть использовано, в частности , в системах автоматического контроля радиоэлектронного оборудования. Цель изобретения - повышение точности измерения . Цель достигается введением перепрограммируемого запоминающего блока 8 и блока 9 записи информации в перепрограм

СО103 СОВЕTCKHX

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sos G 01 R 21/04 21/00

ГОСУДАРСТВЕННЫР КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Ъ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4691182/21 (22) 11.05.89 (46) 07.01.92, Бюл. М 1 (71) Рязанское конструкторское бюро "Глобус" (72) Ю.Н, Максимов (53) 621.317.78,023 (088.8) (56) Авторское свидетельство СССР

М 1290188, кл. G 01 R 21/00, 1985.

Авторское свидетельство СССР

N. 1287025. кл. G 01 R 21/00, 1985.

Я.1 1704102 А1 (64) АВТОМАТИЧЕСКИЙ ИЗМЕРИТЕЛЬ

ИМПУЛЬСНОЙ МОЩНОСТИ СВЧ-РАДИОСИГНАЛОВ (57) Изобретение относится к радиоизмерениям и может быть использовано, в частности, в системах автоматического контроля радиоэлектронного оборудования. Цел ь изобретения — повышение точности измерения. Цель достигается введением перепрограммируемого запоминающего блока 8 и блока 9 записи информации в перепрограм1. 04102 мируемый запоминающий блок. Введенные блоки и образованные связи позволяют линеаризовать проходную характеристику детектора 3, выходной сигнал которого поступает в первый вычислитель 5 совместно с сигналом о средней мощности, Если во всех известных технических решениях в качестве сигнала в форме огибающей используется непосредственно сигнал с детектора, то в изобретении сигнал с детектора 3 испольэу ется для формирования адреса перепрограмИзобретение относится к радиоизмерениям и может быть использовано, в частности. в системах автоматического контроля радиоэлектронного оборудования.

Целью изобретения является повышение точности измерения.

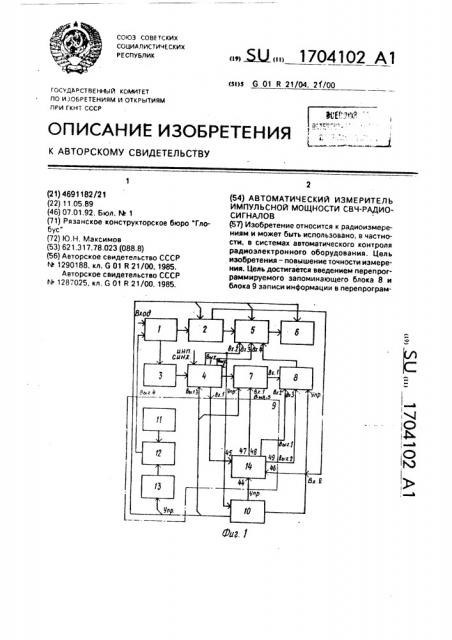

На фиг. 1 приведена структурная схема измерителя; на фиг. 2 — структурная схема блока записи мгновенных значений напряжения; на фиг, 3 — структурная схема первого вычислительного блока; на фиг. 4— структурная схема второго вычислительного блока; на фиг. 5 — структурная схема блока управления: на фиг, 6 — график, поясняющий принцип линеаризации характеристики детектора; на фиг. 7 — алгоритм работы второго вычислительного блока.

Автоматический измеритель импульсной мощности CB +радиосигналов (фиг. 1) содержит делитель 1 мощности, преобразователь 2 средней мощности, детектор 3, блок 4 записи мгновенных значений напряжения, первый вычислительный блок

5, индикатор 6. коммутатор 7, перепрограммируемый запоминающий блок 8, блок 9 записи информации в перепрограммируемый запоминающий блок и блок 10 управления.

Делитель 1 мощности, преобразователь 2 средней мощности, первый вычислительный блок 5 и индикатор 6 соединены последовательно. Также последовательно соединены .детектор 3, вход которого подключен к выходу делителя 1 мощности, блок 4 записи мгновенных значений напряжения, коммутатор 7 и программируемый запоминающий блок 8. причем первый вычислительный блок 5 своими вторым и третьим входами соединяется с первым и вторым выходами блока 4 записи мгновенных значений напряжения, а четвертым входом — с выходом перепрограммируемого запоминающего блока (ЗУ) 8.

Блок 9 записи информации в перепрог раммируемый запоминающий блок содержит

45 мируемого постоянного запоминающего

6 ока 8 для занесения и считывания числовых значений, линеариэующих сквозную характеристику измерительного тракта. Этим исключается влияние нелинейности характеристики детектора 3 на результат измерения. Устройство также содержит делитель 1 мощности, преобразователь 2 средней мощности, индикатор 6, блок 4 записи мгновенных значений напряжения, комутатор 7 блок 10 управления, 1 з. и. ф-лы, 7 ил, соединенные последовательно генератор

11, управляемый аттенюатор 12 СВЧ. цифроаналоговый преобразователь 13, а также второй вычислительный блок,4, входами соединенный с и реобразователем 2 средней мощности и блоком 4 записи мгновенных значений напряжения, а выходом — c nepeпрограммируемым блоком 8 и коммутатором 7.

Блок 10 управления соединен с управляющими входами блоков измерителя.

Блок 4 записи мгновенных значений напряжения (фиг. 2) содержит преобразователь 15 мгновенного значения напряжения, блок 16 памяти, коммутатор 17 адреса, регистр 18 пользователя, синхронизируемый генератор 19, состоящий из последовательно соединенных элемента И 20. усилителя

21 импульсов, элемента ИЛИ 22, первого блока 23 задержки, формирователь 24 импульсов, счетный триггер 25, второй блок 26 задержки, счетчик 27 адреса записи, элемент И 28, установочный триггер 29, третий блок 30 задержки, Узлы блока 4 записи мгновенных значений напряжения соединены следу : щим образом. Элемен- И 28, второй вход которого подключен к установочному триггеру 29. соединен последовательно со счетным триггером 25, фсрмировате".ì 24 импульсов, синхронизируемым генератором 19, преобразователем 15 мгновенного зна-ения напряжения, на вход которого поступает сигнал с детектора 3, и ;эх 16 па ",яти, ад ресный вход которогс соединен через коммутатор 17 адреса с регистром 18 пользователя и выходом счетчика 27 адреса записи, входом соединенного через блок 30 задержки со счетным триггером 25, Елок 16 памяти соединен также входом через блок

26 задержки с выходом синхронизируемого генератора 19 и через коммутатор 17 адреса с выходом счетчика 27 eäðåñà записи.

Вычислительный блок 5 (фиг. 3) содержит блок 31 памяти, блок 32 умножения, 1704102

10

35

50

55 коммутатор 33, блок 34 деления и блок 35 суммирования, Узлы первого вычислительного блока 5 соеди не н ы следующим образом, Коммутатор 33 соединяется одним выходом с блоком 34 деления, другим выходом — c блоком

35 суммирования, выход которого подключен к второму входу блока 34 деления. Блок

31 памяти соединяется с блоком 32 умножения, второй вход которого подключен к выходу блока 34 деления.

Вычислительный блок 14 (фиг. 4) содержит генератор 36 тактовых импульсов, центральный процессорный элемент 37, например, серии 580, буфер 38 шины адреса, буфер 39 шины данных, формирователь

40 управляющих сигналов, постоянное запоминающее устройство 41, оперативное запоминающее устройство 42 и блоки 43 программируемого параллельного интерфейса, блок 14 связан входами 44 — 46 соответственно с выходами блоков 10, 4 и преобразователя 2, а выходами 47 — 49 связан с входами коммутатора 7 и перепрограммируемого запоминающего блока 8.

Узлы второго вычислительного блока 14 соединены следующим образом, Генератор

36 тактовых импульсов соединяется с входом центрального процессора 37. выходы которого через буфер 38 шины адреса, буфер 39 шины данных, формирователь 40 управляющих сигналов соединяются с ПЗУ 41 и ОЗУ 42 и блоками 43 программируемого параллельного интерфейса.

Блок 10 управления (фиг. 5) содержит последовательно соединенные генератор

50 опорной частоты, ключ 51, счетчик 52 импульсов, блок 53 хранения программ, регистр 54 команд, дешифратор 55 команд, а также дешифратор 56 "О", первый блок 57 задержки, первый элемент ИЛИ 58, второй блок 39 задержки, счетчик 60 шага программ, шифратор 61, элемент И 62, второй элемент ИЛИ 63, счетчик 64, счетчик 65 адреса считывания.

Элемент ИЛИ 63 соединяется со счетчиком 60 шага программ и через элемент 59 задержки с блоком 53 хранения программ, который соединяется также с выходом счетчика 60 шага программ и входом дешифратора 56 "О, выход которого подключен к управляющему входу ключа 51. Один из выходов дешифратора 55 команд через элемент И 62, соединенный также со счетчиком

64, соединяется с шифратором 61, выход которого подключен к счетчику 60 шага программ. Выход дешифратора 55 команд соединяется также с входами счетчиков 64 и 65 и через блок 57 задержки с элементом ИЛИ

58, на выходе которого формируется команда на считывание информации из блока 16 памяти, На фиг. 7 представлены операции 66-6R алгоритма работы вычислительного блока

14.

Измеритель работает в двух режимах: режиме автоматической настройки и режиме измерения импульсной мощности.

При использовании измерителя по прямому назначению, т. е. в режиме измерения импульсной мощности. входной сигнал поступает на делитель 1 мощности, который направляет его по двум каналам: на преобразователь 2 средней мощности и на канал дискретизации огибающей по уровню и времени, включающий детектор 3, блок 4 записи мгновенных значений напряжения, коммутатор 7 и перепрограммируемый запоминающий блок 8.

На выходе преобразователя 2 средней мощности образуется сигнал, несущий информацию о средней мощности последовательности входных радиоимпульсов. В канале дискретизации огибающей детектор

3 выделяет огибающую измеряемого радиоимпульса, а блок 4 записи мгновенных значений напряжения огибающей преобразует ее в последовательность цифровых отсчетов. Эти цифровые отсчеты используются как адреса для выборки из перепрограммируемого запоминающего блока 8 цифровых данных, записанных туда ранее в режиме автоматической настройки.

В режиме измерения импульсной мощности устройство работает в три этапа.

Первый этап — запись мгновенных значений напряжения огибающей радиоимпульсов — реализуется блоком 4 записи мгновенных значений (фиг. 2>. который работает следующим о5разом. Для реализации записи мгновенных значений блок 10 управления подает управляющие комгндь на коммутатор 17 адреса, обеспечиуая -аким образом подключение счетч ка 27 адоеса записи к входу адреса блока 16 памяти.

Преобразование мгновенного значенио преобразователем 15 мгновенного значения напряжения производится по приходу импульсов запуска с усилителя 21 импульсов.

С задержкой. необходимой для преобразования сигнала в преобразова1еле 15 мгновенного значения напряжения, из импульсов запуска блоком 26 задержки формируются импульсы записи на блок 16 памяти.

Рассмотрим более подробно Формирование импульсов записи и адреса записи.

По приходе с блока 10 управления ко анды управления установочный триггер 29 уста1704102 продолжается в течение времени единичного состояния счетного триггера 25. Импульсы с выхода синхронизируемого генератора

19 поступают в качестве импульсов запуска на преобразователь 15 мгновенного значения напряжения, зти импульсы, пройдя блок

26 задержки, поступают в качестве импульсое записи нг блок 16 памяти. Адрес записи формируется счетчиком 27 адреса записи блока 4 путем счета импульсов синхронизируемого генератора 19. Задним фронтом импульса со счетного триггера 25 с задержкой, определяемой блоком 30 задержки, счетчик 27 адреса записи устанавливается в исходное положение. Незадержанный сигнал счетного триггера 25 поступает в качестве импульса занесения на блок 31 (фиг. 3) памяти, куда также поступает код числа и со счетчика 27 адреса записи, Таким образом, Т формируется n = импульсов запуска

t преобразователя мгновенного значения напряжений, л импульсов записи и код адреса зап1" и на блок 16 памяти (Т вЂ” период повторения радиоимпульсов, ht — период импульса запуска преобразователя 15 мгновенного значения напряжения).

По истечении времени, необходимого для окончания процесса записи, блок 10 управления подает команду на преобразователь

2 средней мощности, по которой последний производит преобразование среднего знз30

55 навливается е единичное положение. При э ом через элемент И 28 разрешается прохождение импульсов синхронизации, однозначно связанных с измеряемым сигналом, на счетный триггер 25. Первым после прихо- 5 да управляющей команды импульсов синхронизации связанным с измеряемым сигналом счетный триггер 25устанавливается вединич-, ное положение, а следующим импульсом вновь переводится в исходное нулевое поло- 10 жение. При переходе в исходное положение счетного триггера 25 переводится в исходное положение и установочный триггер 29, Таким образом, на выходе счетного триггера 25 формируется единичный импульс с длитель- 15 ностью, равной периоду импульсов синхронизации. Этот импульс, поступая на элемент И 20, замыкает цепь положительной обратной связи усилителя 21 импульсов через линию первый блок 23 задержки — 20 элемент ИЛИ 22. Сформированный формирователем 24 импульсов по переднему фронту импульса со счетного триггера 25 короткий импульс поступает через элемент

ИЛИ 22 на синхронизируемый генератор 19 25 и начинает циркулировать в кольце с периодом, определяемым величиной задержки первого блока 23 задержки. этот процесс чения мощности, При этом результат преобразования хранится в преобразователе до третьего этапа.

Второй этап работы — получение среднего значения мощности по дискретным мгновенным значениям огибающей сигнала, полученным на первом этапе. На этом этапе блок 10 управления последовательно формирует команды, обеспечивающие обработку записанной в блоке 16 памяти информации.

В начале этого этапа блок 10 управления формирует команду нв коммутатор 17 адреса, «оторый осуществляет переключение шин адреса блока 16 памяти от счетчика 27 адреса записи к блоку 10 управления, а также команды на коммутатор 33 (фиг. 3), который подключает блок 35 к выходу перепрограммируемого запоминающего блока 8.

Далее блок 10 управления последовательно формирует адреса считывания и подает команды считывания на блок 16 памяти.

Считанная информация о мгновенных значениях измеряемого сигнала поступает через коммутатор 7 в качестве адреса нэ перепрограммируемый запоминающий блок 8. Предварительно на этапе изготовления э режиме автоматической настройки измерителя в перепрограммируемый запоминающий блок 8 записана информация, обеспечивающая линеаризацию характеристики преобразованияя детектором мощности входного сигнала.

Для считывания информации из перепрограммируемого запоминающего блока 8 также подается команда с блока 10 управления.

Считанное число через коммутатор 33 поступает на предварительно обнуленный по команде с блока 10 управления блок 35.

Блок 35 имеет в своем составе регистр памяти, что позволяет накапливать в нем результаты суммирования после считывания информации по каждому адресу,-Суммирование производится по команде с блока 10 управления. После обработки таким образом информации, считанной по последнему адресу блока 16 памяти, в сумматоре хранится величина, пропорциональная и

А=Х q

q=1 где и — количество дискретных значений, записанных в блок 16 памяти;

Uq — мгновенное значение измеряемого сигнала, записанного в блоке 8.

По окончании суммирования блок 10 управления подает команды на коммутатор 17

17041

45

55 адреса и коммутатор 33, которые соответственно соединяют выход регистра 18 пользователя с шиной адреса блока 16 памяти и выход блока 8 с входом делительного блока

34. При этом устройство подготовлено к заключительной стадии работы.

На третьем (заключительном) этапе по команде считывания с блока 10 управления происходит считывание информации иэ блока 16 памяти по адресу, предварительно занесенному оператором, обслуживающим устройство, в регистр 18 пользователя. Считанное по этому адресу число преобразуется блоком 8 и через коммутатор 33 поступает на делительный блок 34 в качестве делимого.

Результат работы делительного блока 34

В и

XUq

q— = 1 где UB — мгновенное значение напряжения по выбранному пользователем адресу поступает на множительный блок 32.

На этот же блок поступает результат преобразования средней мощности преобразователем 2 средней мощности и информации с блока 31 памяти о числе мгновенных значений входного сигнала, записанных в блоке 31 памяти.

В блоке 32 умножения по командам с блока 10 управления последовательно производится перемножение значений средUa ней мощности Рср, величины В = — и л

Xuq я=1 числа и, записанного в блок 31 памяти мгновенных значений и входного сигнала.

Таким образом, выходная величина

Рхо- (1)

П . U, q =1 соответствует мгновенному значению импульсной мощности в заданной оператором точке временной оси. По команде с блока 10 управления измеренное мгновенное значение мощности заносится в индикатор 6.

Выше рассмотрена работа измерителя в основном режиме, режиме измерения импульсной мощности входного сигнала. В предлагаемом устройстве, как указывалось, на этапе изготовления реализуется режим автоматической настроики с целью учета индивидуальных характеристик СВЧ-детектора 3. Для этого используется блок 9 записи информации в перепрограммируемый запоминающий блок 8 и коммутатор 7. На вход измерителя подается непрерывный

СВЧ-сигнал с генератора 11 через управляемый аттенюатор 12 СВЧ, а в блок 10 управ5

35 ления устанавливается специальная программа настройки измерителя.

Измеритель в этом ре, л е работает в два этапа.

Первый этап — определение опорных значений характеристики детектора. На этом этапе после пуска рограммы блок 10 управления подает на цифроаналоговый преобразователь 13 такой цифровой код, при котором управляемый аттенюатор 12

СВЧ открывается и с генератора 11 на делитель 1 мощности поступает максимально допустимый уровень мощности. Далее по команде с блока 10 управления преобразователь 15 (фиг. 2) мгновенного значения напряжения преобразует постоянное напряжение с детектора 3 в код, результат преобразования по команде блока 10 управления считывается вычислительным блоком

14 (вход 45). Также по команде с блока 10 управления преобразователь 2,"редней мощности преобразует значение мощности непрерывного сигнала, значение этой мощности Р1 (вход 46) также запоминается в оперативном запоминающем устройстве 42 блока 14 вычислений, Описанный цикл операций повторяется для различных значений мощности. устанавливаемых управляемым аттенюатором 12 СВЧ

В результате работы устройства на этом этапе для каждой опорной точки в оперативной памяти (41) вычислительного блока 14 записаны значения мощности P> ..P> и соответствующие им напряжечня с детектора 3.

Второй этап — расчет значений напряжений, вносимых в перепрограммируемый запоминающий блок 8. На этом этапе вычислительный блок 14 поочередно рассчитывает значения напряжеч и зячосимых в перепрограммируемый запоглнчающий блок 8 для опорных точек.

При этом для O ã"; з т чаг принимаемой за основную, например д 1& точ :и максимальной мощности Ря (фиг. б; значение

Ф напряжения U> принимается равным значению напряжения U-, по. чо :,, д1а данного уровня мощности Р на предыдущем этапе. Для остальных оп;рчых точек значения напряжений расс лтieаютсa по формуле

Оп

UI = — р, (2)

Рл где Ui — значение напряжения. записываемое в блок 8;

Un — значение напряжения на выходе детектора при подаче мощности Р, для опорной точки, принятой за основную;

Рл — значение мощности, подаваемой нэ детектор в основной опорно, тс, е

1704102

5

Pi — значение мощности, подаваемой на детектор в произвольной опорной точке, Далее вычислительный блок 14 используя вычисленные значения U1 . 02 ..... 0<, 1 1 1 поочередно рассчитывает все промежуточные значения напряжений, заносимые в блок 8 по формуле где U — значение напряжения, записываемое в блок 8 по адресу. соответствующему напряжению U;

Ui — значение напряжения в I é опорной точке, полученное при подаче мощности Р1;

Ui — значения напряжения, заносимые в блок 8 для 1-й опорной точки и рассчитанные по формуле (2).

Ui+» U > Оь

Рассчитанные таким образом значения напряжений U записываются по адресам, соответствующим всем возможным значениям кодов с преобразователя 15.

Блок 14 работает по алгоритму, представленному на фиг. 7. Программа, реалиэу ющая данный алгоритм, записана в постоянном запоминающем устройстве 41.

К выполнению этой программы блок 14 поступает непосредственно после подачи на него питающих напряжений.

В процессе выполнения программы выделяются управляющие команды с блока 10 управления через блок 43 программируемого параллельного интерфейса (вход 44).

Используются команды двух видов для вызова двух ветвей алгоритма. Два разряда входного кода в этих командах используются для кодирования типа команды, остальные разряды для указания либо номера точки калибровки (в первой команде) либо для указания крайней точки калибровки (во второй команде).

Выделение вида команды реализуется операциями 66 — 68 алгоритма.

По команде первого типа, используемой при калибровке детектора, реализуется ветвь алгоритма, содержащая операции 6973, по команде второго типа — ветвь, содержащая операции 74 — 86..

В результате реализации алгоритма фиг. 7 в блок 8 будут занесены числовые значения, обеспечивающие линейность сквозной характеристики передачи детектора 3, блоков 4 и 8, Блок 10 управления работает следующим образом, Для запуска устройства оператор с помощью органов управления подает команду Пуск" на второй элемент ИЛИ 63, которая поступает на счетчик 60 шага программ и второй блок 59 задержки и переводит счЬт-15

55 чик 60 шага программ иэ нулевого в первое положение. Двоичный код первого шага программы, вырабатываемой счетчиком 60 шага программ, поступает на блок 53 хранения программы, второй блок 59 задержки с задержкой формирует команду считывания. и производится считывание первого слова и рограммы.

Слова программы в блоке 53 хранения программы последовательно состоят иэ двух частей: кода временной задержки и кода команды, выдаваемой с блока 10 управления на другие блоки устройства.

Код временной задержки заносится в счетчик 52 импульсов, на счетный вход которого поступает через ключ 51 опорная частота с генератора 50 опорной частоты, Импульсы опорной частоты подсчитываются счетчиком 52 импульсов. который выдает сигнал переполнения в момент времени, когда сумма ранее введенного числа и числа импульсов, поступающих на вход счетчика

52 импульсов. превысит полную емкость счетчика. Сигнал переполнения через второй элемент ИЛИ 63 поступает на счетный вход счетчика 60 шага программы. В результате счетчик 60 шага программы формирует код адреса следующего вага программы, Далее процесс повторяется до считывания последней команды программ.

Вторая часть слов, записанных в блоке

53 хранения программ, поступает на регистр

54 команд в виде двоичного кода команды. затем дешифрируется дешифратором 55 команд. Дешифратор 55 команд непосредственно формирует команды управления на все блоки устройства в виде потенциальных уровней длительностью. соответствующей длительности вага программ, Одна из команд с дешифратора 55 команд поступает на счетный вход счетчика 65 адреса считывания и через первый блок 57 задержки на первый элемент ИЛИ 58. При этом счетчик

65 адреса считывания формирует двоичный ход адреса считывания, а на выходе первого элемента ИЛИ 58 формируется команда на считывание информации из блока 16 памяти.

Сформированные. таким образом команды считывания используются для считывания записанной по всем адресам информации.

На заключительной стадии, когда необходимо обеспечить считывание только по одному заданному пользователем адресу, используется другая команда с выхода дешифратора 55 команд, которая через первый элемент

ИЛИ 58 поступает на тот же вход считывания блока 16 памяти, Формирование адресов считывания информации блока 16 памяти проводится в строгом соответствии с числом и. т. е. с числом сделанных в блок

17 04102

16 памяти записей. 8 счетчик 64 по окончении этапа записи, как и в блок 31 памяти, заносится число и. Поскольку процесс считывания информации из блока 16 памяти и л вычисления величины А =, Г Uq состоит иэ

О =1 и повторяющихся групп операций, в блоке

10 управления предусмотрена воэможность реализации циклического повторения групп операций.

Циклическое повторение реализуется следующим образом, С дешифратора 55 команд формируется специальная команда, код которой записан в блоке 53 хранения программ в конце массива, подлежащего повторению. Эта команда поступает через элемент И 62. который открыт в случае, если состояние счетчика 64 не является нулевым, и далее на шифратор

61. Шифратор 61 формирует двоичный код адреса команды, с которой начинается повторяемый массив, и заносит этот код в счетчик 60 шага программы, обеспечивая повторение процесса, В процессе считывания одна из команд дешифратора 55 команд, поступающая на счетчик 65 адреса считывания, также поступает на счетчик 64.

Значение числа в счетчике по мере повторения циклов уменьшается от и до О. При нулевом положении счетчика 64 элемент И 62 закрывается, циклическое повторение операций прекращается, счетчик 60 шага программ переходит к следующему адресу программы. Таким образом, для обеспечения процесса измерения в блок 53 хранения программы должны быть занесены коды всех элементарных действий по управлению отдельными блоками устройства.

В результате введения блоков 7 — 9, позволяющих проводить автоматическую настройку измерителя. учитывающую индивидуальные особенности характеристики детектора, устраняется влияние нелинейного характера передаточной характеристики детектора 3 на результат измерения импульсной мощности, что и приводит к снижению погоешности измерения. Положительный эффект тем более, чем больше огибающая радиоимпульсов отличается от прямоугольной формы.

Формула изобретения

1. Автоматический измеритель импульсной мощности СВЧ-радиосигналов, содержащий последовательно соединенные делитель мощности, преобразователь средней мощности, первый вычислительный блок и индикатор, последовательно соединенные детектор и блок записи мгновенных

50 значений напряжения, а тахх.е злах управления и коммутатор, причел вход детектора соединен с вторым выходом делителя мощности, первый и второй выходы блока за;ч,;си мгновенных значений напряжения подключены соответственно к второму и третьему входам первого вычислительного блока, а первый, второй, третий и четвертый выходы блока управления соединены с управляющими входами преобразователя средней мощности, первого вычислительного блока, индикатора и блока записи мгновенных значений напряжения, вход блока управления соединен с первым выходом блока записи мгновенных значений напряжения, о т л и ч à IQ шийся тем, что, с целью повышения точности измерения, в него введены коммутатор и перепрограммируемый запоминающий блок, выход которого соединен с четвертым входом первого вычислительного блока. а также блок записи информации в перепрограммируемый запоминающий блок, первый и второй входы которого соединены соответственно с третьим выходом блока записи мгновенных значений напряжения и вторым выходом преобразователя средней мощности. а первый. второй и третий выходы блока записи информации в перепрограммируемый запоминающий блок — с вторым и третьим входами перепрограммируемого запоминающего блока и первым входом коммутатора соответственно, второй вход которого подключен к четвертому выходу блока записи мгновенных значений напряжения. четвертый выход блока записи информации в перепрограммируемый запоминающий блок соединен с вторым входом делителя мощности, причем управляющие входы коммутатора перепрограммируемого запоминающего блока и первый и второй управчяющие еходы блока записи инфорл;ации в перепрордммируемый 32пол. нающий 6чох соединены с пятым. шестыь1 и седьмым выходами блока управления.

2. Измеритель поп. 1, отл ич а ю щи йс я тем, что блок записи информации в -=„-епрограммируемый запоминающий блок содержит второй вычислительный бчок и последовательно соединенные генератор., иравляемый аттенюатор СВЧ и цифровое.o овый преобразователь, пр . ем первый. второй входы и первый, второй, третий выходы второго вычислительного блока являются соответственнс первым, вторь,M входами и первым, вторым. третьим выходами блока записи информации в перепрограммируемый запоминающий блок, четвертым выходом которого является выхоп управляемого аттенюатора СБЧ. а ьхс16

1704102

15.N ес) ам анеееи ку 5

Огп &. г.2 ды управления второго вычислительного блока и цифроаналогового преобразователя — соответственно первым и вторым упИмп. СинЮ. От dn. равляющими входами блока записи информации в перепрограммируемое запоминающее устройство

4f

>ran!4 .58 уГ

170 102

ЙФ dn 7&8

1704102 и-г

Составитель С.Хромов

Техред М.Моргентал

Корректор Л.Патай

Редактор С.Пекарь

Производственно-издательский комбинат "Патент", г, Ужгород. ул.Гагарина, 101

Заказ 61 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4/5