Генератор псевдослучайных равномерно распределенных двоичных цифр

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может использоваться при мадвлироаании случайных процессов. Целью изобретения является повышение быстродейЁтвия. Для этого в устройство, содержащее генератор 1 тактовых импульсов, двоичный счетчик 2, блок 3 памяти, регистр 4 сдвига и первый сумматор 5 по модулю два, дополнительно введены регистр 6 сдвига и трги сумматора 7, 8 и 9 по модулю два.. Использование указанной структуры позволяет повысить быстродействие генератора за счет того, что соседние по времени отсчеты выходного кода становятся независимыми, 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 06 F 7/58

ГОСУДАРСТВЕННЫЙ КОМИТЕТ .ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4489871/24 (22) 03.10.88 (46) 30.01.92. Бюл. № 4 (72) Э,B,Àðáåíèí, А,В.Китайцев и А.Н.Вин ицкий (53) 681.3 (088,8) (56) Авторское свидетельство СССР

¹ 1105889, кл. G 06 F 7/58, 1983.

Водовозов А.М., Лабичев В.Н. Генератор псевдослучайного сигнала. — Приборы и техника эксперимента, 1982, ¹ 6, с.72 — 73, рис.1. (54) ГЕН Е PATOP ПСЕВДОСЛУЧАЙНЫХ

РАВНОМЕРНО РАСПРЕДЕЛЕННЫХ ДВОИЧНЫХ ЦИФР

Изобретение относится к вычислительной технике и может быть использовано при моделировании случайных процессов.

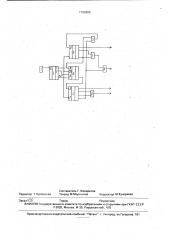

Целью изобретения является повышение быстродействия устрэйства, Блок-схема генератора изображена на чертеже.

Генератор содержит генератор 1 тактовых импульсов, двоичный счетчик 2, блок 3 памяти, регистр 4 сдвига, первый сумматор

5 по модулю два, дополнительный регистр 6 сдвига, второй 7, третий 8 и четвертый 9 сумматоры по модулюдва.

Генератор работает следующим образом. Тактовые импульсы с выхода генератора 1 тактовых импульсов поступает на, счетный вход двоичного счетчика 2. Образующийся при этом на разрядном выходе первого разряда счетчика 2 сигнал типа

"меандра" обеспечивает при положительной полуволне чтение содержимого одной из

„„SU „„1709305 А1 (57) Изобретение относится к вычислительной технике: и может использоваться при моделировании случайных процессов.

Целью изобретения является повышение быстродействия; Для этого e ycTpoAcT o, содержащее генератор 1 тактовых импульсов, двоичный счетчик 2, блок 3 памяти, регистр

4 сдвига и первый сумматор 5 по модулю два, дополнительно введены регистр 6 сдвига и три сумматора 7, 8 и 9 по модулю два.

Использование указанной структуры позволяет повысить быстродействие генератора за счет того, что соседние по времени отсчеты выходного кода становятся независимыми. 1 ил. ячеек блока 3 памяти. адрес которой определяется кодом, имеющим место на остальных и разрядах двоичного счетчика 2. По спаду импульса на выходе первого разряда счетчика 2 осуществляется сдвиг информации в регистрах 4 и 6 сдвига, причем в первый разряд регистра 4 сдвига производится запись значения 0 или 1, считанного из блока 3 памяти, в -первый разряд регистра 6 сдвига записывается значение с выхода сумматора 5 по модулю два, представляющее собой сумму по модулю два сигналов с выходов четырех разрядов регистров 4 и 6 сдвига. Одновременно сигнал с выхода четвертого разряда дополнительного регистра

6 сдвига переписывается в ту же ячейку блока 3 памяти, что обеспечивается имеющейся в данный момент отрицательной полуволной сигнала типа "меандра" с выхода первого разряда счетчика 2, воздействующего на вход управления записью — чтением блока 3

1709305 памяти. Тем самым завершается один цикл работы, длительность которого равна двум периодам импульсов. поступающих с выхода генератора 1 тактовых импульсов. С приходом очередного тактового импульса изменяется на единицу содержимое и разрядов двоичного счетчика, что приводит к изменению адреса ячейки блока 3 памяти.

От цикла к циклу код на адресных входах блока 3 последовательно нарастает, Процесс продолжается до заполнения счетчика

2, а затем повторяется. По всей сути регистр

4 сдвига, блок 3 памяти и дополнительный регистр 6 сдвига в совокупности с первым сумматором 5 по модулю два образуют генератор псевдослучайных последовательностей на регистре сдвига с линейной обратной связью, причем общая длина такого регистра равна в данном случае 2" +8 и может быть выбрана очень большой. Генерируемые двоичные цифры снимаются в первых разрядных выходов регистров 4 и 6 сдвига и с выходов третьего и четвертого сумматоров 8, 9 по модулю два, Использование сумматоров 7,8 и 9 позволяет практически исключить взаимную зависимость генерируемых двоичных цифр.

Точки подключения входов сумматоров 5 — 9 по модулю два, а также точки съема выходного сигнала определены опытным путем и обеспечивают при п>,8 достаточно большой период генерируемой псевдослучайной последовательности, независимость и равномерное распределение генерируемых двоичных кодов.

Формула изобретения

Генератор псевдослучайных равномерно распределенных двоичных цифр, содержащий генератор тактовых импульсов, двоичный счетчик, блок памяти, регистр сдвига и первый сумматор по модулю два, причем выход генератора тактовых импульсов соединен со счетным выходом двоичноt.o счетчика, первый разрядный выход которого соединен с входом синхронизации

5 регистра сдвига и входом управления чтением-записью блока памяти, остальные разрядные выходы счетчика соединены с адресным входом блока памяти, информационный выход которого соединен с инфор10 мационным входом регистра сдвига, выход старшего разряда которого соединен с первым входом первого сумматора по модулю два, отличающийся тем, что, с целью повышения быстродействия, в него введены

15 дополнительный регистр сдвига и три сумматора по модулю два, причем четвертый разрядный выход дополнительного регистра сдвига соединен с информационным входом блока памяти и с первым входом

20 второго сумматора по модулю два и со вторым входом первого сумматора по модулю два, выход которого соединен с информационным входом дополнительного регистра сдвига, вход синхронизации которого сое25 динен с первым разрядным выходом двоичного счетчика, второй разрядный выход дополнительного регистра сдвига соединени со вторым входом втОрого сумматора по модулю два, выход которого соединен с перЗО вым входом третьего сумматора по модулю два, второй вход которого соединен с четвертым разрядным выходом регистра сдвига, второй и третий разрядные выходы которого соединены соответственно с пер35 вым и вторым входами четвертого сумматора по модулю два, первый разрядный выход дополнительного регистра сдвига, выходы третьего и четвертого сумматоров по модулю два и первый разрядный выход регистра

40 сдвига являются разрядным выходом геНерэтора.

1709305.

Составитель Г. Филаретов

Редактор Т,Орловская Техред M.Ìîðãåíòàë Корректор М.Кучерявая Заказ t ьб ул6 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101