Устройство для сопряжения с микроэвм

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано как внешнее устройство для увеличения быстродействия микроэвм типа "Электроника- 60", "Электроника МС 1201" и других с аналогичным интерфейсом. Цель изобретения - повышение быстродействия за счет сокращения количества необходимых пересылок. Устройство содержит селектор адреса, блок прерывания, блок памяти микрокоманд, два арифметико-логических блока, блок хранения табличных функций, коммутаторы, приемопередатчик, регистры, элементы задержки, ИЛИ, И-НЕ, И, триггеры. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)ю G 06 F 13/00.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4137926/24 (22) 21.10.86 (46) 30.01.92. Бюл.гЬ4 (71) Минский радиотехнический институт (72) В. С. Жук, А. Г. Якубенко, А. Е. Леусенко и И. Е. Ероховец (53) 681.3(088.8) (56) Авторское свидетельство СССР

М 1182529, кл. G 06 F 13/00, 1985.

Электронная промышленность, 1983, N

9, с. 28-29. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ С

МИКРОЭВМ

Изобретение относится к вычислительной технике, в частности, может быть использовано как внешнее устройство для увеличения быстродействия микроЭВМ типа "Электроника- 60", "Электроника

МС1201" и других с аналогичным интерфейсом.

Цель изобретения — повышение быстродействия за счет сокращения количества необходимых пересылок.

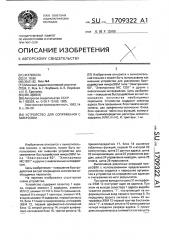

На чертеже изображена структурная схема устройства.

Устройство содержит селектор 1 адреса, первый элемент 2 задержки, элемент

ИЛИ 3, элемент И вЂ” НЕ 4, блок 5 прерывания, первый 6 и второй 7 триггеры, элемент И 8, второй элемент 9 задержки, первый регистр

10, блок 11 памяти микрокоманд, интерфейс

ЭВМ 12, первый арифметико-логический блок 13, второй регистр 14, второй арифметико-логический блок 15, третий регистр 16,,, Ы,„, 1709322 А1 (57) Изобретение относится к вычислительной технике и может быть использовано как внешнее устройство для увеличения быстродействия ми кроЭ В М типа "Электроника60", "Электроника МС 1201" и других с аналогичным интерфейсом. Цель изобретения — повышение быстродействия за счет сокращения количества необходимых пересылок. Устройство содержит селектор адреса, блок прерывания, блок памяти микрокоманд, два арифметика-логических блока, блок хранения табличных функций, коммутаторы, приемопередатчик, регистры, элементы задержки, ИЛИ, И вЂ” НЕ, И, триггеры. 1 ил. приемопередатчик 17, блок 18 хранения табличных функций, первый 19 и второй 20 коммутаторы, шина 21 данных адреса, шина

22 синхронизации, шина 23 управления вводом, шина 24 управления выводом, шина 25 4 ответа, шина 26 прерывания. Q

Выполнение различных операций мик- сС) роЭВМ с использованием предлагаемого () устройства сводится к пересылке аргументов в устройство по определенным адресам и считыванию из него результатов.

При цикле вывода на шину 21 интерфейса ЭВМ 12 поступает один из адресов. При этом на выходе селектора 1 адреса вырабатывается уровень "1", поступающий на информационный вход первого триггера 6. По переднему фронту сигнала с шины 22 интерфейса ЭВМ 12 первый триггер 6 установлен в "1", в первый регистр 10 записываются четыре младших разряда адреса. С приходом синхроимпульса снимается сигнал уста1а

1 3

3 "

"О . г

;>а

45 !

=0 новки нулевого состояния триггера 7, "1" с выхода первого триггера 6 поступает «а вход элемента И 8 и на вход разрешения приемопередатчика 17, разрешая прохождение через него информации. Поскольку в данном цикле вывода сигнал "Ввод" на шине 23 интерфейса ЭВМ 12 не вырабатывается„та второй триггер 7 остается в нулевом состоянии. Нулевое состояние триггера 7 обуславливает прохождение через приемопередатчик 17 информации с шины 21 ин-. терфейса ЭВМ 12 к блокам устройства, го сигналу "Вывод" с шины 24 интерфей;-.

ЭВМ 12, который через элемент ИЛИ 3 и элемент И 8 поступает на вход страбиравания блока 11 памяти микрокаманд, из блока

11 памяти будет прочитана микракаманда по адресу, младшие разряды которого поступают с выходов первого регистра 10, а старший разряд ("0") —;о триггера 7.

В зависимости от адреса будут выработаны сигналы ("0") на определенных выходах блока 11 памяти микрокоманд и произойдет запись (или чтение) в один или несколько блоков устройства. Сигнал с выхода элемента И 8 поступит также через второй элемент

9 задержки и через элемент И-HE 4 на шину

25 интерфейса ЭВМ 12. Второй элемент 9 задержки необходим для того, чтобы к мсменту выработки синхросигнала закончились переходные процессы, возникающие при стробировании блока 11 памяти микрокоманд. Получив синхросигнал, ЭВМ снимает сигнал "Вывод" с шины 24 интерфейса ЭВМ 12, вследствие чего прекращено чтение микрокоманды из блока 11 памяти и закончена выработка синхросигнала на выходе элемента И вЂ” HE 4. После снятия сигнала на шине 25 микроЭВМ снимает синхросигнал на шине 22, По следующему синхросигналу на шине 22 первый триггер 6 установлен в нулевое состояние, если ЭВМ в следующем цикле обмена обращается не к устройству, так как на информационный вход первого триг-ера 6 с выхода селектора 1 адреса поступает "0", При цикле ввода в микро Э ВМ из устройства прием адреса, т, е. запись в первый регистр 10 и установка в единичное состояние первого триггера 6, происходит аналогично описанному циклу вывода. После эта на шину 23 поступает из ЭВМ сигнал

"Ввод", который устанавливает в единичное состояние второй триггер 7. Сигнал -, выхо- 5 да второго триггера 7 поступает на вход режима приемопередатчика 17, и он передает информацию от блоков устройства на шину 21. Выработка синхрасигнала на элементе И вЂ” НЕ 4 и чтение микрокоманды из блока 11 памяти микрокоманд происходит, как и в цикле вывода, за исключением того, что сигнал "Ввод" с шины 23 поступает на эгемент ИЛИ 3 через первый элемент 2 задержки, задерживающий сигнал "Ввод" на время, необходимое для установки старшега разряда адреса блока 11 памяти, поступа,ощего ",. выхода второго триггера 7. После снятия сигнала "Ввод" с шины 23 и сигнала с шины 22 второй триггер 7 установлен в нулевое состояние.

Рассмотрим ра5оту устройства с описания операций, выполняемых блоком 13, Для выполнения умножения требуется заслать в устройство операнды и прочитать резульгат. Множитель передается из ЭВМ в цикле вывода, Поступающий из ЭВМ мна;-;китель через приемопередатчик 17 принимается во второй регистр 14, поскольку блоком 1". памяти микрокоманд будет выработан отрицательный импульс на выходе третьего разряда, производящий запись Во второй региста ".4, Затем а цикле вывода из ЗВАЛ через приемопередатчик 17 передается множимое. Блок 11 памяти микракаманд вырабатывает отрицательные импульсы на выходах

4. l4, 15 и 16-го разрядов, г раисхадит чтение второго регистра 14, прием операндов и кода операции в блок 13, после чего он выполняет умножение целых чисел в дополнительном коде. Во время выполнения умножения, с задержкой на время записи в блок 13 и на время выработки сигнала ответа на втором элементе 9 задержки и элемен-,à И вЂ” HE 4, на выходе "Готовность" блока 13 появится "0", который снимается после завершения выполнения умножения блоком

13.

При третьем обращении ЭВМ в цикЛе

"Ввод" происходит чтение старшего слова произведения на второй вход-выход блока

13 и передача ега в ЭВЫ через приемопередатчик 17, Чтение старшего слова произведения можно делать и па условным адресам

1011, 1010, где дополнительно происходит запись старшего разряда произведения во второе AllY 15 и ва втором случае еще и сброс а "0" третьего регистра 16, При необходимости прочитать и младшие разряды произведения делается четвертое обращение ЭВМ к устройству в цикле "Ввода". В этом случае блоком 11 памяти микрокоманд вырабатываются низкие уровни на выходах 1, 15 и 17-ro разрядов и происходит чтение младших разрядов произведения на первый вход-выход блока I3 и далее через первый коммутатор 19 и приемопередатчик 17 в ЭВМ

1709322

Чтение младшего слова произведения можно производить в цикле ввода и по условным адресам 1100, 1110, при этом дополнительно происходит запись младших разрядов произведения в блок 15, а во втором случае еще и сброс третьего регистра

16. Если требуется только значение старших 16-ти разрядов произведения, то второе считывание (последнюю пересылку) делать не надо, что сокращает обмен на одну пересылку.

В случае быстродействующей микроЭВМ третья пересылка может начаться до окончания выполнения умножения в блоке

13, но это не приведет к нарушению работы устройства, так как в этом случае на выходе Готовность" блока 13 присутствует "0" до тех пор, пока не будет закончено умножение. Прием кода в первый регистр 10 и выработка сигналов на выходе блока 11 памяти микрокоманд будет происходить аналогично, но "0" с выхода "Готовность" блока 13 запрещает выработку сигнала ответа на элементе И вЂ” НЕ 4. После завершения операции умножения в блоке 13 и появления операции "1" на выходе "Готовность" блока 13 происходит прием кода операции с двух младших разрядов входа управления блока 13, производится чтение старшего слова произведения на второй вход-выход блока 13 и передача его в ЭВМ через приемопередатчик 17, а также вырабатывается сигнал на элементе И-НЕ 4, и далее пересылка завершается стандартным образом (как цикл вывода из ЭВМ).

Умножение дробных чисел выполняется аналогично умножению целых числа, за исключением того, что множимое передается в устройство в цикле вывода по адресу 1010.

При возведении в квадрат в устройство необходимо переслать один операнд и прочитать результат. При возведении s квадрат целых чисел операнд передается из ЭВМ в цикле "Вывод". В результате блок 11 памяти микрокоманд вырабатывает нулевые сигналы на выходах 3, 4, 14, 15 и 16-ro разрядов и происходит запись операнда через приемопередатчик 17 во второй регистр 14, разрешение чтения второго регистра 14, прием возводимого в квадрат операнда в блок 13 и запуск на выполнение умножения аналогично рассмотренному умножению. Чтение результата также производится аналогично, как и после умножения.

При возведении в квадрат дробных чисел операнд пересылается в цикле вывода по условному адресу 1011.

Для выполнения деления в устройство требуется заслать старшее и младшее слова делимого, делитель, прочитать частное и

55 при необходимости еще и остаток и убедиться, что не было переполнения при делении. До выполнения операции деления выполняется пересылка кода "1" в блок 5 прерывания в цикле вывода (разрешение прерывания по переполнению). Эта пересылка может выполняться один раз в начале работы. При выполнении операции деления пересылается старшее слово делимого в устройство в цикле вывода ЭВМ, блок 11 памяти микрокоманд вырабатывает низкие уровни на выходе 16-го разряда и происходит прием через приемопередатчик 17 в блок 13 с второго входа-выхода старшего слова делимого. После этого в устройство пересылается младшее слово делимого в цикле вывода ЭВМ и происходит запись его во второй регистр 14. Затем пересылается делитель в цикле вывода ЭВМ, вырабатываются низкие уровни на выходах 4, 15 и 16-го разрядов блока 11 памяти микрокоманд, производится чтение второго регистра 14, причем в блок 13 младшего слова делимого с первого входа-выхода делителя через приемопередатчик 17 и с второго входа-выхода блока 13 кода операции с двух младших разрядов входа управления после чего блок

13 включается на выполнение операции деления. Во время выполнения деления, спустя задержку на время записи в блок 13 и выработки сигнала на втором элементе 9 задержки и элементе И вЂ” НЕ 4, на выходе

"Готовность" блока 13 появится "0", который снимается только после завершения выполнения операции деления.

При следующем обращении ЭВМ в цикле ввода будет произведено чтение частного (выполняется аналогично чтению старших разрядов произведения). Если необходимо, то при следующем обращении к устройству в цикле вывода считывается остаток от деления.

Если во время выполнения деления в блоке 13 (когда делитель меньше или равен делимому) возникает переполнение, то вырабатывается "1" на выходе переполнения блока 13, которая поступает в блок 5 прерывания, который отрабатывает типовой цикл прерывания с передачей в ЭВМ вектора адреса прерывания.

Если после выполнения умножения (квадрата) положительных дробных чисел необходимо произвести деление, то после умножения (квадрата) выполняется пересылка делителя в цикле вывода ЭВМ. В результате вырабатывается низкий уровень на выходах 15, 16 и 17-го разрядов блока 11 памяти микрокоманд. Будет произведено чтение младшего слова произведения блока

13 на его первый вход-выход и запись млад1709322 шего слова произведения в блок 13, прием делителя в блок 13 через приемопередатчик

17 с второго входа-выхода и запуск на выполнение деления, В дальнейшем все выполняется аналогично рассмотренному делению.

При вычислении табличной функции в устройство надо переслать код аргумента, являющийся адресом для блока 18. Код аргумента пересылается в цикле "Вывод"

ЭВМ через приемопередатчик 17 во второй регистр 14 (аналогично записи множителя при умножении). Во время пересылки в цикле ввода 3ВМ производится чтение одной из табличных функций. При этом блок 11 памяти микрокоманд вырабатывает сигналы на выходах 11, 12 и 13 разрядов соответственно и 4-го разряда (чтение первого регистра 14), после чего будет произведено чтение соответствующего ПЗУ блока 18 по адресу, поступающему на его вход с выходов второго регистра 14.

Для выполнения операций блоком 15 необходимо переслать код операции в третий регистр 16, операнд в блок 15 и прочитать результат из блока 15. Вначале производится пересылка в цикле вывода

ЭВМ через приемопередатчик 17 в третий регистр 16 8-разрядного кода операции (на выходах 7 и 8-го разрядов блока 11 памяти микрокоманд будут выработаны низкие уровни, поступающие на входы записи третьего регистра 16). Старшие четыре разряда задают тип выполняемой впоследствии операции, а младшие — параметр операции (на сколько разрядов производить сдвиг), С целью удобства программирования возможна отдельная запись старших четырех и младших четырех разрядов третьего регистра 16 при обращении ЭВМ в цикле вывода.

При следующей пересылке в цикле вывода ЭВМ в устройство на выходе 10-ro разряда блока 11 памяти микрокоманд будет

"0" и произойдет прием кода операции с второго регистра 14 и операнда с первого информационного входа-выхода через приемопередатчик 17 в блок 15 с одновременным выполнением операции (сдвигом). При очередной пересылке в цикле ввода в ЭВМ происходит выработка "0" на выходе 9-го разряда блока.11 памяти микрокоманд, чтение результата операции из блока 15 на первый информационный вход-выход и передача его через приемопередатчик 17 в

ЭВМ.

Нормализация числа с использованием блока 15 может происходить так. При первой пересылке нормализуемого числа в цикле вывода из ЭВМ в устройство на выходах

6 и 10-го разрядов блока 11 памяти микрокоманд будут выработаны низкие уровни и произойдет сброс в "0" третьего регистра

16, прием в блок 15 кода операции с второго входа и числа с первого входа-выхода (через приемопередатчик 17).

При второй пересылке в цикле ввода в

ЭВМ происходит выработка "0" на выходах

7, 8, 9-го разрядов блока 11 памяти микрокоманд и происходит чтение из блока 15 двоичного кода крайней левой "1" на второй вход-выход с передачей его в ЭВМ через приемопередатчик 17, и также запись этого кода левой "1" в четыре младших разряда третьего регистра 16. При третьей пересылке в цикле вывода нормализуемого числа в блок 15 принимается код операции с третьего регистра 16, число с первого входа-выхода через приемопередатчик 17 и производится сдвиг влево. При пятой пересылке в цикле ввода в ЭВМ из устройства из блока 15 через его первый вход-выход и приемопередатчик 17 и ЭВМ считывается нормализованное число, Возможно выполнение операций в блоке 15 над результатом операции в блоке 13.

Этой цели служат команды-пересылки в цикле ввода ЭВМ. Это исключает необходимость приема этого кода в ЭВМ и засылку его в блок 15. Дополнительный выигрыш в быстродействии можно получить при умножении массива чисел на некоторый коэффициент. B этом случае следует при первой пересылке в цикле вывода записать этот коэффициент во второй регистр 14 и далее производить умножение на первое число массива, как было описано (умножение).

При умножении остальных чисел массива первую пересылку,(во второй регистр 14) делать не надо, так как коэффициент попрежнему хранится во втором регистре 14.

Поэтому при умножении каждого числа массива на коэффициент нужно делать только три последних пересылки (как в описании умножения).

Формула изобретения

Устройство для сопряжения с микроЭВМ, содержащее приемопередатчик, селектор адреса, первый и второй триггеры, элемент

И, элемент ИЛИ, первый элемент задержки, первый -третий регистры, первый коммутатор, первый арифметика-логический блок, причем вход селектора адреса является входом устройства для подключения к шине данных адреса микроЭВМ, а выход соединен с информационным входом первого триггера, первый вход первого элемента Ис выходом первого триггера, выход первого коммутатора — с информационным входом регистра и с первым информационным вхо1709322

50

55 дом-выходом приемопередатчика, второй информационный вход-выход которого является входом-выходом устройства для подключения к шине данных адреса микроЭВМ, первый информационный входвыход первого арифметико-логического блока соединен с выходом второго регистра и информационным входом первого коммутатора, отл ича ю щееся тем, что, с целью повышения быстродействия, в него введены второй коммутатор, второй арифметикологический блок, блок хранения табличных функций, блок памяти микрокоманд, второй элемент задержки, блок прерывания и элемент И вЂ” КЕ, причем второй информационный вход-выход приемопередатчика соединен с информационным входом-выходом второго арифметико-логического блока, вторым информационным входом-выходом первого арифметико-логического блока, информа ц ион н ы ми входами блока и реры ваний и третьего регистра, выходами второго коммутатора и блока хранения табличных функций, адресный вход которого соединен с выходом второго регистра, выход третьего регистра — с информационным входом второго коммутатора и входом кода операций второго арифметико-логического блока, информационный вход первого регистра является входом устройства для подключения к шине данных адреса микроЭВМ, синхровходы первого регистра и первого триггера и вход сброса второго триггера образуют вход устройства для подключения к шине синхронизации микроЭВМ, первый вход запроса блока прерывания, единичный вход второго триггера и вход первого элемента задержки образуют вход устройства для подключения к шине управления вводом микроЭВМ, выход первого элемента задержки соединен с первым входом элемента ИЛИ, второй вход

5 которого является входом устройства для подключения к шине управления выводом микроЭВМ, а выход соединен с вторым входом элемента И, выход которого соединен с входом стробирования блока памяти микро10 команд и через второй элемент задержки— с первым входом элемента И-НЕ, второй вход которого соединен с выходом готовности первого арифметико-логического блока, выходы блока памяти микрокоманд соеди15 нены с синхровходами второго и третьего регистров, первого и второго арифметикологических блоков, блока хранения табличных функций, первого и второго коммутаторов и блока прерываний, второй

20 вход запроса которого соединен с выходом переполнения первого арифметико-логического блока, выход первого триггера — с разрешающим входом приемопередатчика, вход режима которого соединен с выходом

25 второго триггера, соединенным с входом старшего разряда адреса блока памяти микрокоманд, входы младших разрядов адреса которого соединены с выходом первого регистра, выход сигнала прерывания и

30 третий вход запроса блока прерывания являются выходом и входом устройства для подключения соответственно к шинам данных адреса и прерывания микроЭВМ, а стробирующий выход, объединенный с вы35 ходом элемента И-КЕ, образуют выход устройства для подключения к шине ответа микроЭ BM.

1709322

72

Составитель И. Хазова

Редактор M. Кобылянская Техред М.Моргентал Корректор Т. Малец

Заказ 427 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101