Устройство сопряжения однородной вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и технике связи в частности к устройствам сопряжения однородной вычислительной системы, и может найти применение при построении узлов коммутации на сетях передачи дискретной информации.Цель изобретения - расширение функциональных возможностей устройства за счет изменения конфигурации связи в цепи произвольной длины. Эта цель достигается тем, что устройство содержит Н+1 блоков ввода информации, Н блоков вывода информации, три элемента ИЛИ, три элемента И, два элемента И-НЕ, элемент ИЛИ-НЕ, группу элементов И-НЕ, два элемента задержки и сумматор единицы. При этом каждый блок ввода информации содержит элемент И-НЕ, элемент И и элемент НЕ, а каждый блок вывода информации содержит четыре элемента И-НЕ, два элемента И и два элемента НЕ. Отличие предложенного устройства от известного заключается во введении в него двух элементов И. группы Н элементов И- НЕ, третий элемент ИЛИ, второй элемент задержки и сумматор единицы. При этом в блоки ввода информации введен элемент НЕ, а в блоки вывода информации введены два элемента И. 1 ил.^

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G. 06 F 15/16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4774902/24 (22) 18.12.89 (46) 30.01.92. Бюл. М 4 (71) Научно-производственное объединение интегрированных микроэлектронных систем (72) Ю.Н. Максименко и В.С. Ракошиц (53) 681.325(088.8) (56) Авторское свидетельство СССР

hL 758128, кл. G 06 F 3/04, 1978.

Авторское свидетельство СССР

М 1049894, кл. G 06 F 3/04, 1982.

Авторское свидетельство СССР

N 949650, кл. G 06 F 7/00, 1980, (54) УСТРОЙСТВО СОПРЯЖЕНИЯ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ (57) Изобретение относится к вычислительной технике и технике связи в частности к устройствам сопряжения однородной вычислительной системы, и может найти применение при построении узлов коммутации на сетях передачи дискретной информации.

Изобретение относится к автоматике и вычислительной технике и предназначено для сопряжения однородных модулей в параллельных вычислительных системах.

Известно устройство для сопряжения вычислительных модулей в однородную вычислительную систему, содержащее блок управления, блок настройки и блок коммутации.

Недостатком этого устройства является низкое быстродействие вычислительных систем, построенных на основе этого устройства, поскольку участки канала обмена типа

„, БЫ,, 1709329 A l

Цель изобретения — расширение функциональных возможностей устройства за счет изменения конфигурации связи в цепи произвольной длины. Эта цель достигается тем, что устройство содержит Н+1 блоков ввода информации, Н блоков вывода информации, три элемента ИЛИ, три элемента И, два элемента И-НЕ, элемент ИЛИ-НЕ, группу элементов И-НЕ, два элемента задержки и сумматор единицы. При этом каждый блок ввода информации содержит элемент И-НЕ, элемент И и элемент НЕ, а каждый блок вывода информации содержит четыре элемента И-НЕ, два элемента И и два элемента

НЕ. Отличие предложенного устройства от известного заключается во введении в него двух элементов И, группы Н элементов ИНЕ, третий элемент ИЛИ, второй элемент задержки и сумматор единицы. При этом в блоки ввода информации введен элемент

НЕ, а в блоки вывода информации введены два элемента И, 1 ил.

"цепь" настраиваются последовательно один за другим, причем входы и выходы этих участков "цепи" указываются прямой адресацией с последующей дешифрацией адресов.

Прямая адресация частей "цепи", составляющий один канал, связана с дополнительной загрузкой настраивающего модуля, поскольку он решает эту задачу с учетом текущего состояния всех устройств сопряжения, что снижает быстродействие систем.

Известно устройство для сопряжения модулей вычислительной системы, содержа1709329 щее блок коммутации, блок настройки и блок управления.

Недостатком этого устройства являются его ограниченные функциональные возможности, проявляющиеся в неспособности организации цепи, состоящей иэ функционально однородных модулей.

Наиболее близким к предлагаемому является устройство для сопряжения однородной вычислительной системы, содержащее (Н+1) блоков ввода информации, (Н вЂ” число направления связи); Н— блоков вывода информации, два элемента

ИЛИ, два элемента И вЂ” НЕ, элемент И, элемент задержки.

Недостатком этого устройства является невозможность формирования цепи с конфигурацией, отвечающей требуемым условиям.

Цель изобретения — расширение функциональных возможностей устройства путем изменения в конфигурации связи в цепи произвольной длины.

Устройство содержит (Н+1) блоков ввода информации, (Н вЂ” число направлений связи), Н вЂ” блоков вывода информации, первый и второй элементы ИЛИ, первый и второй элементы И-НЕ, первый элемент И, первый элемент задержки, при этом каждый блок ввода информации содержит элемент

И-НЕ и элемент И, каждый блок вывода информации содержит с первого по четвертый элементы И-НЕ и первый и второй элементы

НЕ. Причем i-й (i=1, Н+1) вход контроля устройства подключен к (Н+2)-му входу элемента И-НЕ I-ro блока ввода информации, i-й вход потенциала поиска устройства подключен к (Н+3)-му входу элемента И-НЕ 1-го блока ввода информации, i-й выход квитирования поиска устройства подключен к выходу элемента и 1-го блока ввода информации, j-й выход потенциалов поиска устройства (J=1, Н) подключен к выходу третьего элемента И-НЕ )-ro блока вывода информации, j-й вход подтверждения поиска устройства подключен к j-му входу первого элемента ИЛИ и через второй элемент

НЕ j-го блока вывода информации к первому входу четвертого элемента И-НЕ j-го блока вывода информации. Выход первого элемента ИЛИ соединен с вторыми входами четвертых элементов И-HE блоков вывода информации. Выход элемента И-HE I-го блока ввода информации соединен с 1-м входом первого элемента И-Н Е и с i-ми входами элементов И-НЕ всех блоков ввода информации, кроме i-ro. Вход первого элемента задержки соединен с первым входом элемента И, а выход первого элемента задержки соединен с вторым входом первого

55 элемента И. Выход первого элемента И-НЕ

j-го блока вывода информации соединен с

J-ми входами первых элементов И-НЕ всех блоков вывода информации, кроме j-ro, и через первый элемент НЕ с первым входом второго элемента И-НЕ j-го блока вывода информации, выход которого подключен к первому входу третьего элемента И-НЕ j-го блока вывода информации. К первому входу последнего подключен выход четвертого элемента И-НЕ J-го блока вывода информации. В устройство введены второй и третий элементы И, элемент ИЛИ-НЕ, третий элемент ИЛИ, второй элемент задержки, сумматор, группа Н элементов И-НЕ. В каждый блок ввода информации введен элемент НЕ, а в каждый блок вывода информации введены первый и второй элементы И. Причем J-й информационный вход устройства соединен c j-м входом третьего элемента ИЛИ, выход которого соединен с первым входом третьего элемента И и с информационным входом сумматора, j-й вход квитирования поиска устройства соединен с j-м входом элемента ИЛИ-НЕ и с (Н+1)-м входом первого элемента И-НЕ j-го блока вывода информации, J-й вход квитирования цепи устройства соединен с j-м входом второго элемента ИЛИ, к (Н+1)-му входу которого подключен выход первого элемента И, j-й информационный выход устройства соединен с выходом первого элемента И j-го блока вывода информации, первый вход которого подключен к выходу сумматора, J-й выход квитирования цепи устройства подключен к второму входу первого элемента И

j-го блока вывода информации и к выходу второгоэлемента j-ro блока вывода информации.

Выход обобщенного квитирования устройства и второй вход третьего элемента И соединены с выходом второго элемента И, первый вход которого соединен с (Н+1)-м входом потенциалов поиска устройства.

Собственный информационный выход устройства подключен к выходу третьего элемента И. Выход второго элемента ИЛИ соединен с вторым входом второго элемента И, с входом суммирования сумматора и через второй элемент задержки с первыми входами вторых элементов и блоков вывода информации, j-й вход подтверждения поиска устройства соединен с вторым входом второго элемента И j-го блока вывода информации, выход элемента ИЛИ-НЕ подключен к третьему входу первого элемента

И и к третьим входам четвертых элементов

И-НЕ блоков вывода информации. Выход первого элемента И-НЕ соединен с первыми входами элементов И-НЕ группы, с первым входом первого элемента И и с

1709329 четвертыми входами четвертых элементов

И-HE блоков вывода информации. Выход элемента И-НЕ j-го блока ввода информации соединен с вторым входом j-го элемента И-НЕ группы и через элемент НЕ блока ввода информации с первым входом элемента И j-го блока ввода информации. Выход элемента И-НЕ (Н+1)-го блока ввода информации через элемент НЕ (Н+1)-го блока ввода информации подключен к первому входу элемента И (Н+1)-го блока ввода информации, выход которого соединен с (Н+1)-м входом первого элемента ИЛИ, J-й вход контроля устройства подключен к третьему входу j-ro элемента И-НЕ группы, выход которого соединен с j-м входом второго элемента И-НЕ. Выход последнего подключен к вторым входам элементов и блоков ввода информации. Выход третьего элемента И-НЕ J-го блока вывода информации подключен к второму входу второго элемента И-НЕ J-ro блока вывода информации, j-й выход подтверждения поиска подключен к выходу первого элемента НЕ j-ro блока вывода информации.

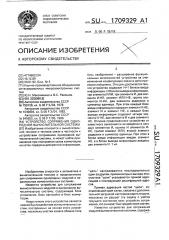

На чертеже показана функциональная схема устройства.

Устройство содержит (Н+1) блоков 1 ввода информации. Н блоков 2 вывода информации, первый, второй элементы ИЛИ 3, 4 первый элемент И 5, элемент ИЛИ-НЕ 6, второй элемент И 7, первый элемент 8 задержки, первый элемент И-НЕ 9, группу из

Н элементов И-НЕ 10, второй элемент И-НЕ

11, третий элемент И 12, третий элемент

ИЛИ 13, сумматор 14 единицы, второй элемент 15 задержки, При этом каждый блок 1 ввода информации содержит элемент И-НЕ 16, элемент

И 17, элемент НЕ 18.

Каждый блок 2 вывода информации содержит первый элемент И-НЕ 19, элемент

Н Е 20, второй элемент И-Н Е 21, третий элемент И-НЕ 22, четвертый элемент И-НЕ 23, элемент НЕ 24, первый и второй элементы

И 25, 26.

Устройство содержит шину 27 входа потенциалов поиска, шину 28 входа контроля, шину 29 входа подтверждения поиска, шину

30 входа квитирования цепи, шину 31 входа квитирования поиска и информационные входы 32, шину 33 выхода квитирования поиска, шину 34 выхода подтверждения поиска, шину 35 выхода квитирования цепи, шину 36 выхода потенциалов поиска, выходную информационную шину 37, шину 38 выхода обобщенного квитирования и собственный информационный выход 39.

Каждому устройству сопряжения соответствует один модуль однородной вычис5

i5

55 лительной системы, а связи смежных устройств через информационные шины 32, 37, шины 27, 36 потенциалов поиска, шины

31, 33 квитирования поиска, шины 29, 34 подтверждения поиска и шины 30, 35 квитирования цепи соответствуют информационным связям модулей вычислительной системы.

При этом первые Н направлений связи устройства сопряжения соответствуют смежным связям, а (Н+1)-е направление соответствует связи устройства сопряжения с собственным модулем.

Таким образом, множество устройств сопряжения, объединенных указанными шинами по структуре информационных связей вычислительной системы, образует децентрализованную систему управления, в которой решается задача формирования цепи из модулей данной однородной вычислительной системы.

Цепь представляет собой произвольную последовательность модулей, объединенных в линию или конвейер, Начало цепи устанавливается произвольно в любом модуле, а длина цепи определяется требуемым количеством объединенных модулей. Модуль может находиться в исправном состоянии или неисправном состоянии. Исправный модуль может быть свободен или занят. Задача формирования цепи решается на множест.. з исправных и свободных модулей. Неисправные и занятые модули исключаются из формируемой цепи. Отказ своего модуля фиксируется нулевым потенциалом на (Н+1)-й шине 28 контроля, кроме того, информационные связи модулей контролируются средствами аппаратного контроля (не показаны). Отказ j-ой (j=1, Н) информационной связи модуля сопровождается формированием нулевого потенциала по соответствующей j-й шине 28 контроля, что вызывает отключение соответствующего входного блока устройства сопряжения.

Рассмотрим работу устройства.

Исправный модуль, инициирующий формирование цепи, включает на (Н+1)-м входе шины 27 единичный потенциал поиска, который при наличии разрешающего единичного потенциала на (Н+1)-входе шины 28 контроля и отсутствии единичных потенциалов поиска на остальных входах шины 27 включает элемент И-НЕ 16 (Н+1)-го блока 1 ввода информации. Нулевой потенциал с выхода (Н+1)-го элемента И-НЕ 16 инвертируется элементами И-НЕ 9 и включает элементы И-НЕ 10 при условии, если соответствующие смежные направления связи находятся в исправном состоянии и по ним не поступают потенциалы поиска.

1709329

50

i последующее устройство и ответного квитирования поиска.

Единичный потенциал с выхода элемента И 5 поступает на элемент ИЛИ 4 и с его выхода через элемент 15 задержки на уг,равляющие входы j-ro элемента И 26 блоков

2 вывода информации. На информационные входы этих элементов поступают входные потенциалы подтверждения поиска шине

29. Таким образом, сформированный элементом И 5 единичный потенциал квитирования våïè обратным ходом, зафикси рованным потенциалами г:одтверждения поиска, транслируется по цепи в устройство — инициатор цепи, где включается элемент И 7, и на его выходе формируется единичньй потенциал обобщенного квитирования. Этот потенциал по шине 38 поступит в соответствующий модуль, информируя его о завершении формирования цепи изустройств, наме енных потенциалами подтверждения поиска.

Кроме того, сформированный элементом И 5 сигнал квитирования цепи через элемент ИЛИ 4 поступает на вход суммирования единицы сумматора 14,,На выходе сумматора 14 формируется единичный код, который через элемент И 25 транслируется по j-й шиче 37 в предшествующее устройство цепи, помеченное выходным потенциалом квитирования j-й цепи 35. На информационном входе 32 предшествующего устройства цепи появляется единичный код, который через элемен — ИЛИ 13

:locT rl38r HB инфор."мационный вход сумматора 14.

При наличии потенциала квитирования цепи на выходе элемента ИЛИ 4 в данном устройстве принятый код увеличиваемся сумматором 14 на единицу и транслируется

Bследующее устрой,с"тво по направлению квитирования цепи. В итоге одновременно с появлением потенциала обобщенного квитирования на шине 38 начального устройства сформированной цепи на собственном информационном выходе 39 устройства будет зафиксирован код длины сформированной цепи (конвейера). Модуль — инициатор формирования цепи, имеет возможность оценить длину сформированной цепи с требуемой. Если сформированная цепь по длине удовлетворяет необходимым требованиям, то в сформированной . цепи модулей организуется вычислительный процесстипа конвейера. в противном случае сформированная цепь разрушается путем обнуления собственного потенциала поиска на (Н+1)-й шине 27 устройства начала цепи; и модуль— инициатор имеет возможность заново повторить процесс формирования цепи.

Формула изобретения

1. Устройство сопряжения однородной вычислительной системы, содержащее Н+1 блоков ввода информации (Н вЂ” число направлений связи), Н блоков вывода информации, первый и второй элементы ИЛИ, первый и второй элементы И-НЕ, первый элемент И и первый элемент задержки, при этом каждый блок ввода информации содержит элемент И-НЕ и элемент И, каждый блок вывода информации — с первого по четвертый элементы И-HE и первый и второй элементы НЕ, причем i-й (i 1, H+1) вход контроля устройства подключен к (Н+2)-му входу элемента И-НЕ i ão блока ввода информации, i-й вход потенциала поиска устройства подключен к (Н+3)-му входу элемента И-НЕ i-ro блока ввода информации, 1-й выход квитирования поиска устройства подключен к выходу элемента И 1-го блока ввода информации,j-й выход потенциалов поиска устройства (j=1, Н) подключен к выходу третьего элемента И-НЕ j-го блока вывода информации, j-й вход подтверждения поиска устройства — к )-му входу первого элемента ИЛИ и через второй элемент HE j-го блока вывода информации к первому входу четвертого элемента И-НЕ

j-ro блока вывода информации, выход первого элемента ИЛИ соединен с вторыми входами четвертых элементов И-НЕ блоков вывода информации, выход элемента И-НЕ

l-ro блока ввода информации — с i-м входом первого элемента И-НЕ и с i-ми входами элементов И-HE всех блоков ввода информации, кроме i-ro, вход первого элемента задержки соединен с первым входом первого элемента И, а выход первого элемента задержки — с вторым входом первого элемента И, выход первого элемента И-HE J-го блока вывода информации соединен с J-ми входами пеовых элементов И-НЕ всех блоков вывода информации, кроме J-го, и через первый элемент НЕ с первым входом второго элемента И-НЕ j-го блока вывода информации, выход которого подключен к первому входу третьего элемента И-НЕ j-го блока вывода информации, к первому входу которого подключен выход четвертого элемента И-НЕ j-го блока вывода информации, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства путем изменения конфигурации связи в цепи произвольной длины, в него введены второй и третий элементы И, элемент ИЛИ-Н Е, третий элемент ИЛИ, второй элемент задержки, сумматор, группу Н элементов И-НЕ, при этом в каждый блок ввода информации введен элемент НЕ, а в каждый блок вывода информации — первый

1709329

12 и второй элементы И, причем j-й информационный вход устройства соединен с j-м входом третьего элемента ИЛИ, выход которого соединен с первым входом третьего элемента И и с информационным входом сумматора, j-й вход квитирования поиска устройства соединен с J-м входом элемента

ИЛИ-Н Е и с (Н+1)-входом первого элемента

И-НЕ j-го блока вывода информации, j-й вход квитирования цепи устройства соединен с j-м входом второго элемента ИЛИ, к (Н+1)-му входу которого подключен выход первого элемента И, J-й информационный выход устройства — с выходом первого элемента И j-го блока вывода информации, первый вход которого подключен к выходу сумматора, j-й выход квитирования цепи устройства подключен к второму входу первого элемента И и к выходу второго элемента

И j-го блока вывода информации, выход обобщенного квитирования устройства и второй входтретьего элемента И соединены с выходом второго элемента И, первый вход которого соединен с (Н+1)-м входом потенциалов поиска устройства, собственный информационный выход устройства подключен к выходу третьего элемента И, выход второго элемента ИЛИ соединен с вторым входом второго элемента И, с входом суммирования сумматора и через второй элемент задержки с первыми входами вторых элементов И блоков вывода информации,j-й вход подтверждения поиска устройства соединен с вторым входом второго элемента И j-го блока вывода информации, выходэлемента ИЛИ-НЕ подключен ктретьему входу первого элемента И и к третьим

5 входам четвертых элементов И-НЕ блоков вывода информации, выход первого элемента И-HE соединен с первыми входами элементов И-НЕ группы, с первым входом первого элемента И и с четвертыми входами

10 четвертых элементов И-НЕ блоков вывода информации, выход элемента И-НЕ j-co блока ввода информации соединен с вторым входом j-го элемента И-НЕ группы и через элемент НЕ блока ввода информации с пер15 вым входом элемента И J-го блока ввода информации, выход элемента И-HE (Н+1)-го блока ввода информации через элемент НЕ (Н+1)-го блока ввода информации подключен к первому входу элемента И (Н+1)-го

20 блока ввода информации, выход которого соединен с (Н+1)-м входом первого элемента ИЛИ, j-й вход контроля устройства подключен к третьему входу)-го элемента И-НЕ группы, выход которого соединен с j-м вхо25 дом второго элемента И-НЕ, выход которого подключен к вторым входам элементов И блоков ввода информации, выход третьего элемента И-HE j-ro блока вывода информации подключен к второму входу второго элеЗО мента И-HE j-го блока вывода информации, j-й выход подтверждения поиска подключен к выходу первого элемента НЕ j-го блока вывода информации.

1709329

28

Редактор С. Лисин

Заказ Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

27

Составитель В. Сычев

Техред М.Моргентал Корректор Т. Малец

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101