Ячейка фоточувствительного матричного запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к оптоэлектронике к разделам считывания, обработки и хранения оптической информации. Целью изобретения является повышение надежности ячейки за счет повышения пороговойчувствительности и расширение динамического диапазона сравниваемых оптических сигналов и расширение функциональных возможностей ячейки за счет обеспечения ассоциативной выборки информации. Ячейка содержит дифференциальный усилитель, состоящий из усилительных 1, 2, 8. 20, 21, 31, 32, нагрузочных 3, 4, 6, 7, 29, 30 и 36 и токостабилизирующих 5 и 22 транзисторов, фотодиоды 9, 10, подключенные к затворам усилительных транзисторов и подложке 11, транзисторы стирания 12, 13, 18, 19, затворы которых подключены к шине стирания, стоки - к источнику смещения фотодиодов, а истоки - к фотодиодам и к соответствующим затворам усилительных транзистороа, триггер-защелку с цепочкой на входе из последовательно соединенных транзисторов стирания и запоминающих конденсаторов 16,17, ключевые транзисторы 35, 37. 38, 39, 41 адресной выборки и сравнения. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (l9) (11)

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4754985/24 (22) 30.10.89 (46) 30.01,92. Бюл. М 4 (71) Институт автоматики и электрометрии

СО АН СССР (72) В,Е. Бутт, Б.Н. Панков, В.В. Савельев и П.E. Твердохлеб (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

М 868834, кл. G 11 С 13/04, 1978.

Авторское свидетельство СССР

М 1619344, кл. 6 11 С 11/42, 29,08.89. (54) ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОГО

МАТРИЧНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА (57) Изобретение относится к оптоэлектронике к разделам считывания, обработки и хранения оптической информации. Целью изобретения является повышение надежности ячейки за счет повышения пороговой

Изобретение относится к области вычислительной техники, а — î÷íåå к оптоэлектронике и может быть использовано в устройствах для считывания, логика-арифметической обработки и хранения оптической информации.

Целью изобретения является повышение надежности ячейки за счет повышения пороговой чувствительности ячейки и расширение динамического диапазона входных оптических сигналов, а также расширение функциональных возможностей ячейки эа счет обеспечения возможности ассоциативного поиска информации.

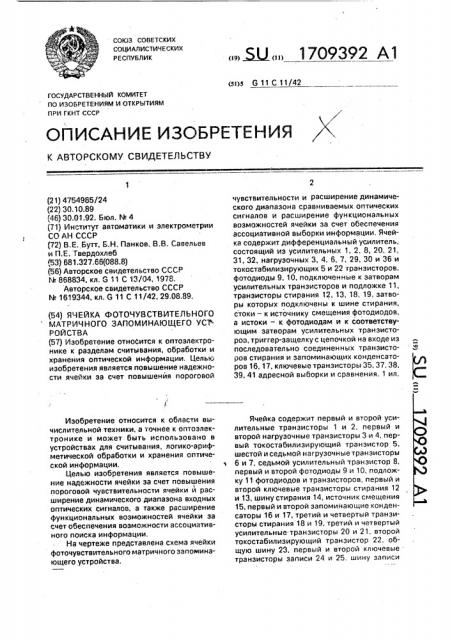

На чертеже представлена схема ячейки фоточувствительного матричного запоминающего устройства.

2 чувствительности и расширение динамического диапазона сравниваемых оптических сигналов и расширение функциональных возможностей ячейки эа счет обеспечения ассоциативной выборки информации. Ячейка содержит дифференциальный усилитель, состоящий из усилительных 1, 2, 8, 20, 21, 31, 32, нагрузочных 3, 4, 6, 7, 29, 30 и 36 и токостабилизирующих 5 и 22 транзисторов, фотодиоды 9, 10, подключенные к затворам усилительных транзисторов и подложке 11, транзисторы стирания 12, 13, 18, 19, затворы которых подключены к шине стирания, стоки — к источнику смещения фотодиодов, а истоки — к фотодиодам и к соответствующим затворам усилительных транэистороэ, триггер-защелку с цепочкой на входе из последовательно соединенных транзисторов стирания и запоминающих конденсаторов 16, 17, ключевые транзисторы 35, 37. 38, 39, 41 адресной выборки и сравнения. 1 ил.

Ячейка содержит первый и второй усилительные транзисторы 1 и 2, первый и второй нагрузочные транзисторы 3 и 4, первый токостабилизирующий транзистор 5, шестой и седьмой нагрузочные транзисторы

6 и 7, седьмой усилительный транзистор 8, первый и второй фотодиоды 9 и 10, подложку 11 фотодиодов и транзисторов, первый и второй ключевые транзисторы стирания 12 и 13, шину стирания 14, источник смещения

15, первый и второй запоминающие конденсаторы 16 и 17, третий и четвертый транзисторы стирания 18 и 19, третий и четвертый усилительные транзисторы 20 и 21, второй токостабилизирующий транзистор 22, общую шину 23, первый и второй ключевые транзисторы записи 24 и 25, шину записи

1709392

2 P.

Зг д0

26, информационные выходы 27 и 28, третий и четвертый нагрузочные транзисторы 29 и

30, пятый и шестой усиллтельные транзисторы 31 и 32, третий ключевой транзистор записи 33, инвертор 34, первый кл>очевой тра»зистор 35, пятый нагрузочный транзистор 36, второй, третий и четвертый кл>ачевые транзисторы 37, 38 и 39, шину адреса

40, пятый ключевой транзистор 41, шину результата 42, первую и вторую разрядные шины 43 и 44, >иину питания 45.

Усилительные транзисторы 1 и 2, нагрузочные тоанзистары 3 и 4, токастабилизиру>ащий транзистор 5 вместе с нагрузочным тра»зисторам 7 образу>ат дифференциальный усилитель (ДУ),режим работы которого обеспечивается активной цепью из токостабилизирующего транзистора 5, нагрузач>>ь>х транзисторов 6 и 7 и усилительного транзистора 8. Истоки усилительных транзисторов 1 и 2 соединены со стоком токостабилизиру>ощего транзистора 5, исток которого подключен к стоку нагруэочного транзистора 7, затвору усилительного транзистора 8, а затвор к стоку усилительного транзистора 8, затвору и истоку нагрузочного транзистора 6. Фотодиодь> 9 и 10 подсоедип,ны соответственно к затворам ус..; л1 ель»>,>х транзисторов 1 и 2, а другими

oj!i":ü;> .>åv>>ûèè выводами к падложкс 11.

Затворы ключевых транзисторов стирания

12 и 13 подключены к шине стирания 14, стоки к источнику смещения фотодиодов 15, а истоки соответственно к затворам усилитель»ых транзисторов 1 и 2; Между стоками усилительных транзисторов 1 и 2 вкл>очена цепочка из последовательно соединенных эапамина>ощего конденсатора 16, канала транзистора стиран;1я 18 и канала транзистора стирания 1а. Параллельно каналу транзистора стирания 19, т.е, к стоку усилительного транзистора 1 и истоку транзистора стирания. 18, подключен запоминающий конденсатор 17. "àòâîðû транзисторов стирания 18 и 19 соединены с шиной стирания 14. Сток и исток транзистора стирания 18 подключены соответственно к затвору усилительных транзисторов 20 и 21 дополнительного дифференциального усилителя, явля>ощегося составной частью триггера-защелки,.Истоки транзисторов 20 и 21 дополнительного ДУ соединены со стокам такостабилизирующего транзистора 22 э >ага усилителя, а затвор и исток TQKGGTBGNл»зиру>ащего транзистора 22 с общей шинс ., 23. Стоки усилительных транзисторов

20 . 21 соединены соответственно с истоками ключевых транзисторов записи 24 и 25, затворы которых подключены к шине записи 26, а стоки, являющиеся лнформационными выходами 27 и 28 допогнительного ДУ и ячейки (триггера-зашелки), подсоединены соответственно к нагрузочным транзисторам 29 и 30 дополнительнага дифференциального усилителя. Сток усилительного транзистора 31 и затвор усилительного транзистора 32 подключены к нагрузачному транзистору 29 (первому информационному выходу 27 ячейки), сток усилительного транзистора 32 и затвор усилительного транзистора 31 подключены к нагрузачному транзистору 30 (второму информационному выходу ячейки), Истоки усилительных транзисторов 31 и 32 соединены со стокам ключевого транзистора записи 33. исток которого подключен к общей шине 23, а, затвор к выходу инвертора 34 сигнала записл на шине записи 26. Инвертор 34 сигнала записи содержит ключевой транзистор 35 и нагрузочный транзистор 36, К информационным выходам 27 и 28 подключены затворы соответгтвенно ключевых транзисторов

37 и 38, истоки которых соединены между собой, а стоки подсоединены соответственно к первой и второй разрядным шинам 43 и 44. Затвор ключевога транзистора 39 соединен а шикай адреса 40, а сток ключевого транзистора 41 — - шиной результата 42.

Сток ключевого транзистора 39 и затвор кл:ачеваго транзистора 41 соединены с истоками ключевых транзисторов 37 и 38, Затвор и исток нагрузачнога транзистора 7, истоки усилительного транзистора 8, ключевых транзисторов 35, 39, 41 подключены к общей шине 23. Стоки >загрузачнь>х транзисторов 3, 4, б, 29, 30, 36 соедлнены с шиной питания 45.

Принцип работы ячейки состоит в следу>а ще м.

По сигналу стирания с шины стирания ,4 через открытые каналы ключевых транзисторов стирания 12 и 13 заряжа>отся да напряжения источника смещения 15 емкости фатодиодав 9 и 10. Появление на затворах усилительных транзисторов 1 и 2 напряжений, смеща ащих в обратном направленли фотодиоды, приводит каналы этих транзисторов в проводящее состояние. ДУ выходит на рабочий режим, при котором ток через усилительные транзисторы 1 и 2 задается параметрами такостабиллзирующей цепи на транзисторах 5, 6, 7, д. Стабильность тока через така=табилизируюший транзистор 5 обеспечивается за счет последовательной отрицательной обратной связи (ООС) по току. Для повышения стабильности в петлю ООС включен инвертирующий усилитель на транзисторах 8 и 6, на вход которого подается сигнал обратной связи па току с нагрузачнога транзистора 7, С вклю1709392 чением усилителя увеличивается в К раз стабильность тока в транзисторе 5, где К— коэффициент усиления по напряжению усилителя на транзисторах 8 и 6.

На выходах ДУ (стоках усилительных транзисторов 1 и 2) устанавливается при этом напряжение AUe»o начального разбаланса этого усилителя, которое через открытые каналы транзисторов стирания 18 и

19 подается на запоминающий конденсатор

16 и запоминается на его емкости, Паразитные емкости между затворами (шиной стирания) и истоками, затворами (шиной стирания) и стоками транзисторов

18 и 19 также оказываются заряженными соответственно до напряжений 0зс и 0зи транзистора 18. 8 предположении одинаковости геометрических размеров каналов транзисторов 18 и 19 емкость между истоком транзистора 18 (затвором транзистора

20) и его затвором будет в 2 раза больше емкости между стоком {затвором транзистора 21) и затвором (шиной стирания) этого транзистора, так как паразитные емкости двух транзисторов оказываются соединенными параллельно.

По окончании сигнала стирания каналы транзисторов 12. 13, 18, 19 запираются. Фотодиоды 9 и 10 оказываются обратно смещенными зарядами, запасенными их емкостями во время стирания, а на емкости запоминающето конденсатора 16 соХРаНЯЕтСЯ НаПРЯжЕНИЕ Ua x.î+Uïeðeç.1 ГДЕ

Unepea.1 — напряжение, которое возникает на конденсаторе 16 в результате перезаряда емкости этого конденсатора через пара- зитную емкость между затвором и стоком транзистора 18 по заднему фронту сигнала стирания, На запоминающем конденсаторе

17, который при стирании был зашунтирован открытым каналом транзистора 19 и поэтому был разряжен, при запирании каналов транзисторов 18 и 19 также возникает напРЯжение Unepes.2, свЯэанное с пеРеэарядом этого конденсатора через удвоенную паразитную емкость затвор-исток (сток) транзисторов 18 и 19. Если конденсатор 17 выполнить со значением емкости, равным удвоенному значению емКОСТИ КОНДЕНСатОРа 16, тО 0перез.1 0перез.2.

Напряжения на запоминающих конденсаторах 16 и 17; суммируясь с выходным нап ряжением дифференциального усилителя (за счет последовательного соединения конденсаторов 16 и 17 с выходом этого усилителя), компенсирует на входах дополнительного ДУ действие как начального разбаланса 0зых.р, так и действие паразитных емкостей транзисторов 18 и 19. . В результате на входах дополнительного

5 20 и 21, нагрузочные транзисторы 29 и 30. соединенные последовательно с ключевы10

27 и 28. На время действия сигнала записи

40 питание этого триггера отключается (канал

55 триггер.

ДУ будет сигнал, соответствующий только полезному сигналу первого каскада.

Дополнительный ДУ, включающий третий и четвертый усилительные транзисторы ми транзисторами записи 24 и 25 и токостабилиэирующим транзистором 22, образуют вместе с пятым и шестым усилительными транзисторами 31 и 32, инвертором на транзисторах 35, 36 и транзистором записи 33 выходной каскад с функциями высокочувствительного компаратора с ячейкой памяти {триггера-защелки), имеющей информационные выходы 27 и 28. Дополнительные ключевые транзисторы 37 — 41 вместе с внешними шинами ввода (вывода) двумя разрядными шинами 43, 44, адресной шиной 40 и шиной результата 42, связывающими ячейки в фоточувствительном матричном, запоминающем устройстве по столбцам и строкам, обеспечивают обращение к этой ячейке по адресу (шина 40) с выводом результата о состоянии ячейки памяти на разрядные шины 43, 44 и логическое сравнение состояния ячейки с внешним запросомм, подаваемым на разрядные шины 43 и 44, с выводом результата сравнения на шину результата 42.

При отсутствии сигнала записи на шине

26 каналы ключевых транзисторов записи

24 и ".5 заперты, а ключевой транзистор 33 открыт(выходным сигналом с выхода 34 инвертора сигнала записи), При этом конфигурация, состоящая иэ.транзисторов

29 — 32, образует статический триггер (транзистор 33 включает его питание), т.е. ячейку памяти с информационными выходами транзистора 33 запирается), зато при замкнутых каналах ключевых транзисторов 24 и 25 иэ транзисторов 20, 21, 22, 24, 25, 29, 30 образуется конфигурация дифференциального усилителя, который усиливает дифференциальный сигнал на его входах (затворах транзисторов 20 и 21). Усиленный сигнал запоминается на паразитных емкостях выходов 27 и 28. По заднему фронту сигнала записи, когда каналы транзисторов записи 24 и 25 запираются, а канал транзистора 33 открывается, происходит срабатывание триггера в соответствии со знаком напряжения, установившегося на его входах (выходах 27 и 28) перед концом сигнала записи. Таким образом, производится компарирование сигнала дифференциального усилителя с фотодиодами на входах, его нормирование по уровню и запись в

1709392

При адресном считывании состояния триггера на разрядные шины появление сигнала адреса на шине адреса 40 вызывает через открытый канал транзистора 39 и один из открь«тых каналов транзисторов 37

w/l««38 (в зависимости GT состояния триггера} соединение общей шины 23 с одной из разрядных шин 43 или 44. При логическом сравнении (ассоциативном поиске информации} транэисторь. 37, 38. образуют две схемы И, входы которых подключены к информационным выходам 27 и 28 триггера и к разрядным шинам 43 и 44. а выходы объединены в шинное ИЛИ, реализуемое по шине результата 42 транзистором 41 (в зависимости от результата сравнения шина

42 соединяется или не соединяется с общим выводом 23}.

Формула изобретения

Ячейка фоточувствительного матричного эапомина«ощего устройства. содержащая первый и второй усилительные транзисторы, стоки которых подключены к истокам и затворам соответственно первого и второго нагрузочных транзисторов, соединенных стоками с шиной питания, истоки первого и второго усилительных транзисторов саед««««:::..-«ь«со стоком первого токостабилизиру«ощего транзистора, первый и второй фотодиоды, которые подключены к затворам соответственно первого и второго усилительных транзисторов и к подложке, первый и второй ключевые. транзисторы стирания, истоки которых соединены соответственно с первым и вторым фотодиодами, стоки первого и второго кл«очевых транзисторов стирания соединеньгс источником смещения фотадиодов, а их затворы — c шиной стирания, третий и четвертый усилительные транзисторы, истоки которых соединены со стоком второго токостабилиэиру«ощего транзистора, стоки третьего и четвертого усилительных транзисторов подключены соответственно к истокам первого и второго ключевых транзисторов записи, затворы которых подключены к шине записи, стоки первого и второго ключевых транзисторов записи подключены к затворам и истокам соответственно третьего и четвертого нагрузочных транзисторов, третий транзистор стирания, исток которого подключен к затвору третьего усилительного транзистора, затвор третьего транзистора стира«:ил подключен к шине стирания, а сток — к эа вору четвертого усилительного транзисê-.:ýà и через запоминающий конденсатор — к стоку второго усилительного транзистора, пятый и шестой усилительные транзисторы, истоки которых соединены со стоком

45 ц0

55 третьего ключевого транзистора записи, эаrsop которого подключен к стоку первого ключевого транзистора, затвору и истоку пятого нагруэочного транзистора, сток пятого усилительного транзистора и затвор шестого усилительного транзистора подключены к затвору и истоку третьего нагрузочного транзистора, сток шестого усилительного транзистора и затвор пятого усилительного транзистора соединены с затвором четвертого нагрузочного транзистора, затвор первого ключевого транзистора подключен к шине записи, стоки третьего, четвертого и пятого нагрузочных транзисторов соединены с шиной питания. истоки первого ключевого транзистора и третьего транзистора записи, а также затвор и исток второго токостабилизирующеготранзистора подключены к общей шине, отличающаяся тем, что, с целью повышения надежности ячейки и расширения ее функциональных возможностей за счет обеспечения возможности ассоциативного поиска информации, в ячейку введены четвертый ключевой транзистор стирания, второй запоминающий конденсатор, седьмой усилительный транзистор, шестОй и седьмой нагрузочные транзисторы и ключевые транзисторы со второго по пятый, причем сток первого усилительного транзистора через второй запоминающий конденсатор соединен с истоком третьего ключевого транзистора стирания и затвором третьего усилительного транзистора, сток четвертого ключевого транзистора стирания подключен к стоку первого усилительного транзистора, исток и затвор

« етвертого ключевого транзистора стирания подключены соответственно к затвору третьего усилительного транзистора ик шине стирания, затВОр первогО токостдбилизирующего транзистора соединен со стоксм седьмого усилительного транзистора, с затвором и истоком шестого нагрузочного транзистора, сток которого подключен к шине питания, исток первого токостабилизирующего транзистора соединен с затвором седьмого усилительного транзистора и стоком седьмого нагрузочного транзистора, затвор и исток которого, а также исток седьмого усилительного транзистора подключены к общей шине, затворы второго и третьего ключевых транзисторов подключены соответственно к стокам пятого и шестого усилительнь«х транзисторов, являющимся информационными выходами ячейки, истоки второго и третьего ключевых транэисторов соединены со стоком четвертого и затвором пятого ключевых транзисторов. истоки которых подключены к общей шине, 1709392.77

Составитель С. Самуцевич

Редактор Н. Коляда . Техред M,Ìoðãåêòàë Корректор Т. Палий

Заказ 430 Тираж ПОдписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„-4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 стоки второго и третьего ключевых транзисторов соединены соответственно с первой и второй разрядными шинами, затвор четвертого ключевого транзистора соединен с шиной адреса, сток пятого ключевого транзистора подключен к шине результата.