Устройство для обнаружения ошибок в блоках памяти программ

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для контроля достоверности хранения информации в постоянных запоминающих устройствах в процессе их работы. Цельюизобретения является повь?шение быстродействия устройства. Устройство содержит блок памяти обращений, группу элементов И, накапливающий сумматор, блок сравнения, коммутатор, счетчик адреса, первый и второй элементы И, элементы ИЛИ с первого по четвертый, первый и второй элементы задержки, первый и второй одновибраторы, сумматор по модулю два, счетчик количества обращений. Цель изобретения достигается тем, что после каждого цикла подсчета контрольной суммы в устройстве осуществляется инверсия признака фиксации обращений в блоке памяти обращений. В результате исключаются непроизводительные циклы перезаписи блока памяти обращений для его начальной установки. 1 ил.ЁИзобретение относится к вычислительной технике, а именно к устройствам контроля постоянной памяти, и может быть использовано для контроля достоверности хранения информации а запоминающих устройствах в процессе работы.Цель изобретения - повышение быстродействия устройства.На чертеже представлена схема устройства для обнаружения ошибок блока памяти программ.Блок 1 памяти программ, изображенный на чертеже, в состав устройства не входит..'Устройство содержит блок 2 памяти обращений, группу элемантов И 3, накапливающий сумматор 4, блок 5 сравнения контрольной суммы, коммутатор 6. счетчик 1 адреса, элементы И 8 и 9, триггер 10 коли-чества обращений, триггер 11 признака первого обращения. Триггер 12 начальной установки, одновибраторы 13-14, сумматор 15 по модулю два, счетчик 16 количества обращений, элементы ИЛИ 17-20, элементы 21- 22 задержки, вход 23 режима контроля устройства, вход 24 адреса устройства, вход 25 признака обращения устройства, тактовый вход 26, вход 27 начальной установки устройства, вход 28 количества контролируемых адресов устройства, вход 29 значения контрольной суммы устройства и выход 30 ошибки устройства.Устройство работает в двух режимах: в режиме начальной установки и режиме контроля.Режим начальной установки устанавливается при появлении положительного потенциала на входе 27 устройства. По этому•Чо ю00ю ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4464819/24 (22) 21.07.88 (46) 30.01.92. Бюл. ЛЬ 4 (72) О.И. Качанко, В.А. Фараджаев и И.Л. Сигалов (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

Мг 813508, кл, 6 11 С 29/00, 1978, Авторское свидетельство СССР

М 1278982, кл. G 11 С 29/00, 1985. (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ

ОШИБОК В БЛОКАХ ПАМЯТИ ПРОГРАММ (57) Изобретение относится к вычислительной технике и может быть использовано для контроля достоверности хранения информации в постоянных запоминающих устройствах в процессе их работы. Целью

Изобретение относится к вычислительной технике. а именно к устройствам контроля постоянной памяти, и может быть использовано для контроля достоверности хранения информации в запоминающих устройствах в процессе работы.

Цель изобретения — повышение быстродействия устройства.

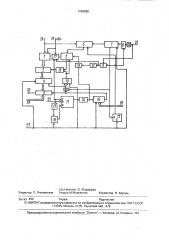

На чертеже представлена схема устройства для обнаружения ошибок блока памяти программ.

Блок 1 памяти программ, изображенный на чертеже, в состав устройства не входит.

Устройство содержит блок 2 памяти обращений, группу элем,знтов И 3, накапливающий сумматор 4, блок 5 сравнения контрольной суммы, коммутатор 6. счетчик

7 адреса, элементы И 8 и 9, триггер 10 колиая Я3.«i> 1709395 Al изобретения является повышение быстродействия устройства. Устройство содержит блок памяти обращений, группу элементов

И, накапливающий сумматор, блок сравнения, коммутатор, счетчик адреса, первый и второй элементы И, элементы ИЛИ с первого по четвертый, первый и второй элементы задержки, первый и второй одновибраторы, сумматор по модулю два, счетчик количества обращений. Цель изобретения достигается тем, что после каждого цикла подсчета контрольной суммы в устройстве осуществляется инверсия признака фиксации обращений в блоке памяти обращений. В результате исключаются непроизводительные циклы перезаписи блока памяти обращечий для его начальной устаHOBKM. 1 Nfl, чества обращений, триггер 11 признака первого обращения, триггер 12 начальйой установки, одновибраторы 13 — 14, сумматор 15 по модулю два, счетчик 16 количества обращений, элементы ИЛИ 17-20, элементы 2122 задержки, вход 23 режима контроля устройства, вход 24 адреса устрсйства, вход

25 признака обращения устройства, тактовый вход 26, вход 27 начальной установки устройства, вход 28 количества контролируемых адресов устройства, вход 29 значения контрольной суммы устройства и выход 30 ошибки устройства.

Устройство работает в двух режимах: в режиме начальной установки и режиме контроля, Режим начальной установки устанавливается при появлении положительного потенциала на входе 27 устройства. По этому

1709395

".èãèàëó устанавливается в "О" счетчик 7, сумматор 4 и триггер 10, a r "1" — триггер 12.

3тат же сигнал, пройдя через элемент ИГ!И

18, устанавливает в "0" триггер 1 1, Положительный потенциал с единичнога выхода тр Irropa 12 разрешает работу элмлента И 8 и 9 и переключает информационный выход счетчика 7 iia выход ком lyra ropa 6. Первый тактовHII 1!Мпульс, праЙдя feрез элемент И и эл81 ент ИЛИ 17, поступает иа вход обОЭ.1. ЕHIt, ß гла„J 2 .. )МЯ ° и, На аДаеСНЫИ вход Korcifporo чере";, ком>лутатар 6 пас-3уna8T;-,ynGBoo eI- .a«eIIve c,eI I;Iza 7, Выхoд элемента И 9 пройдя ч!"-.реэ элемент 21 задержки и элемент 34ЛИ! 19, поступает на

B>1од записи блока 2 памяти, На иифарма.!Ho!In; вход блока.2 памяти r!ocr>f)aoт нулeBGA потенциал с ед;.!и!лчнога выхода триггера 10. Таким Образом, первым такToBым импульсам по нулевому адресу заnAcIlBaeтсЯ 0 . Первый тактовый импульс, про!лдя Iepea злемен r 22 заде жки и элемент И О, пр!1бавляет к значению счетчика 7 ед!>ницу. описанный цикл рабаты устройства позтаряется да переполнения счетчи а 7, Импульс переполнения счетчика 7 ус анa Brfl>IBBGT в "0" триггер 1I 2, нуле,-эЙ потенциал на един!!Чнам выходе o"I".I)oro перекл!очает коммутаrop 6 и указывает На Окончание режима начально1л установки устройства и готовность ус- риАства для рабаты B режиме ко 1гроля. Сигнал переполнения счетчика 7, пройдя через элемент И.ПИ 20, пе )GBopит триггер 10 в един! чиое с )стояние и обнуляет сум1!атар 4, В

peNNlv ;е контроля На вх )F, 23 уст„)аис) ва ioДается ОДииичиый потенциал, На вход 24

ПОДО!" гся адрес. а HB вхОД 25 признак бра;ц! ниЯ П !)!л пос гуплении с!л!.нала иа входы 24 и 25 устройства на выходе блока

" появляется значение кода, записа!!Наго па соответствующему адресу, а на выходе блока 2 памяти появляется нулевой сигнал. Так ка«триггер 10 находится в единичном СОстаянии, та иа выхоД8 сумматора 15 па f" .Одул!О два присуTc f ву8т едини 4ныи по" тенциал, KoTop6IA разрешает прохажден!ге через группу элементов И 3 кода с Гзь1хада блока 1 .амати. На сумматарг. 4 происходит сложение содержимого счи7аниой ячейки пам.г! и с предыдущим содержа!!ием сумматора. При этой выход сумматора 15:ПО ма дулю два поступает иа тактовый вход риггера 11, который устанавливается в "1", Г э переходу из "0" в "1" триггера 11! одновизратОр 14 формирует положительный и.лпу.".ьс, который прибавляет ":-1!" к счетчику

16 и через элемент ИЛ! 19 поступает Н

ВхоД эаписи блока 2 памЯти. В блоке 2 памяти и> адресу считывания записывается

10 .!

30 >5

45 единичное значение с триггера 10. Если пролсходит обращение к ячейке памяти, к которой уже об ращались, то содержимое соответствующего адреса блока 2 памяти равно единице. Следовательно, на выходе сумматора 15 присутствует нулевой потенциал и содержимое данного адреса повторно не накапливается в сумматоре 4, Кроме того, в счетчике 16 Не учитыва1атся многократные обращения к Одним и тем -«e адресам, счетчик 16 считает только первое обращение по каждому иэ адресов, После

Toro, как было обращение по всегл <ОНТро; 11руемым адресам, счетчик 16 переполняется, разрешает сравнение накопленной суммы в сумматоре 4 с эталонной суммой с входа 29 устройства и устанавливает триггер 10 и су1. :матар в нулевое состояние.

Если садер>ки!лое сумматора совпало с кодам на входе 29, то на выходе 30 имеется нулевой потенциал; если содержимое сумIaTopa не совпало со значением кода на входе 29, то иа выходе 30 устройства появляется сигнал, указывающий на неверную работу блока памяти.

После перекл!Очения триггера 10 в нулевое состояние работа устройства происходит 70чнО так . же, KBK описано, с тай разницей, что все ячейки блока 2 памяти установлены в единицу. Па каждому (первому) обращению из блока 2 памяти считывается единичный сигнал, который, кладываясь со значением триггера 10. дает.

На выходе единичный потенциал, который

Осуществляет те же действия, которые описаны, с той разницей, что в блок 2 записывается иаль, Если к ячейке блока 2 памяти производится повторное обращение, та на вь!Ходе сумматора 15 имеется нулевой потенциал, который запрещает суммирование иа сумматоре 4, В дальнейшем работа устройства повторяется.

Таким образом, значительна повышается быстродействие устройства, поскольку

iGT необходимости в многократной перезаписи блока 2 памяти после каждого цикла каитаоля, Формула изобретения

Устройсгво для обнаружения ошибок в блоках памятл программ, содержащее первый элемент ИЛИ, первый и второй элементы И, коммутатор, информационные входы первой группы которого явля!отся информационными входами устройства. выходы коммутатора подключены к адресным входам блока памяти обращений, а информационные входы второй группы коммутатора соединены с выходами группы счетчика адреса, группу элементов И, первые входы ко"709395 торых являются информационными входами устройства, а выходы подключены к информационным входам накапливающего сумматора, выходы которого подключены к информационным входам первой группы 5 блока сравнения, информационные входы второй группы и выход которого являются соответственно входами значения контрольной суммы и выходом ошибки устройства, первый триггер, информационный вход 10 которого является входом режима контроля устройства, а выход соединен с входам первого одковибратора, выход которого подключен к счетному входу счетчика количества обращений, второй однавибра- 15 тар, о т л и ч а ю щ е е с я тем, то, с целью повышения быстродействия, в него введены второй, третий и четвертый элементы

ИЛИ,первый и второй элементы задержки, второй и третий триггеры, сумматор па ма- 20 дулю два, причем первый вход первого элемента ИЛИ является входом обращения устройства, выход первого элемента ИЛИ соединен с входом выборки блока памяти обращений, выход которого подключен к 25 первому входу сумматора па модулю два, второй вход которого соединен с информа. ционным входом блока памяти обращений и с выходом второго триггера, R-вход которого подключен к S-входу третьего тригге- 30 ра, входам начальной установки счетчика адреса, счетчика количества обращений и накапливающего сумматора, первому входу второго элемента ИЛИ и является входом начальной установки устройства, выход 35 сумматора по модулю два соединен с вторым входом элемента ИЛИ, вторыми входами элементов И группы, синхровходом первого триггера и входом второго одновибратора„выход которого подключен к второму входу второго элемента ИЛИ, выход которого соединен с входом сброса первого

-,риггера, информационные входы счетчика количества обращений являются входами количества обращений устройства, а выход переполнения счетчика количества обращений подключен к управляющему входу блока сравнения и первому входу четвертого элемента ИЛИ, выход которого соединен со счетным входом nepaoro триггера и входом обнуления накапливающего сумматора, вход записи блока памяти обращений подключен к выходу третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого одновибрзтора и первого элемента задержки, вход которого подключен к третьему входу первого элемента ИЛИ и выходу второго элемента И, первый вход которого является тактовым входом устройства и соединен с входом второго элемента задержки, выход которого подключен к первому входу первого элемента И, второй вход которого соединек с вторым входом второго злементз И, управляющим входом коммутатора и выходом третьего триггера, R-вход которого подключен к второму входу четвертого элемента ИЛИ и выходу счетчика адреса, счетный вход которого соединен с выходом первого элемента И.

Составитель В. Фараджев

Редактор Л. Пчолинская Текред M.Moðãåíòàë Корректор Н. Король

За,аз 430 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-.издательский комбинат Патент", r. Ужгород, ул.Гагарина, 101