Цифроаналоговый преобразователь с автоматической коррекцией нелинейности

Иллюстрации

Показать всеРеферат

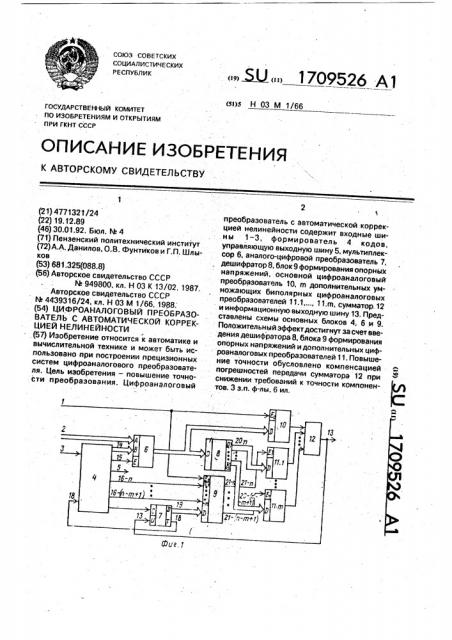

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении прецизионных систем цифроаналогового преобразователя. Цель изобретения - повышение точности преобразования. Цифроаналоговыйпреобразователь с автоматической коррекцией нелинейности содержит входные шины 1-3, формирователь 4 кодов, управляющую выходную шину 5, мультиплексор 6, аналого-цифровой преобразователь 7, дешифратор 8, блок 9 формирования опорных напряжений, основной цифроаналоговый преобразователь 10, m дополнительных умножающих биполярных мифроаналоговыхпреобразователей 11.111.т, сумматор. 12И информационную выходную шину 13. Представлены схемы основных блоков 4, 6 и 9. Положительный эффект достигнут за счет введения дешифратора 8, блока 9 формирования опорных напряжений и дополнительных цифроаналоговых преобразователей 11. Повышение точности обусловлено компенсацией погрешностей передачи сумматора 12 при снижении требований к точности компонентов. 3 з.п. ф-лы, 6 ил.21-'n-mi^l]ЮJ213

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

s Н 03 М 1/66

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ЛО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTO PC КОМУ С В ИД ЕТЕЛ ЬСТВУ (21) 4771321/24 (22) 19.12,89 (46) 30.01.92. Бюл. М 4 (71) .Пензенский политехнический институт (72) А.А. Данилов, О.В. Фунтиков и Г,П. ШлыКОВ (53) 681.325(088.8) (56) Авторское свидетельство СССР

М 949800, кл, Н 03 К 13/02, 1987, Авторское свидетельство СССР

М 4439316/24, кл. Н 03 М 1/66, 1988. (54) ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ С АВТОМАТИЧЕСКОЙ КОРРЕКЦИЕЙ НЕЛИНЕЙНОСТИ . (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении прецизионных систем цифроаналогового преобразователя. Цель изобретения — повышение точности преобразования. Цифроаналоговый

„„Я2„, 1709526 А1 преобразователь с автоматической коррекцией нелинейности содержит входные шины 1 — 3, формирователь 4 кодов, управляющую выходную шину 5, мультиплексор 6, аналого-цифровой преобразователь 7, дешифратор 8, блок 9формирования опорных напряжений, основной цифроаналоговый преобразователь 10, m дополнительных умножающих биполярных цифроаналоговых преобразователей 11.1...„ 11.m, сумматор.12 и информационную выходную шину 13. Пред-ставлены схемы основных блоков 4, б и 9.

Положительный эффектдостигнут за счет введения дешифратора8, блока 9 формирования опорных напряжений и дополнительных циф: роаналоговых преобразователей 11, Повышение точности обусловлено компенсациейпогрешностей передачи сумматора 12 при снижении требований к точности компонентов. 3 з,п. ф-лы. 6 ил, 1709526

30.ности к изобретению является ЦАП с авто- 40 матической коррекцией нелинейности,. содержащий первый и второй ЦАП, сумма50 ного напряжения, второй ЦАП, аналоговый сумматор, аналого-цифровой преобразователь амплитуды импульса, ОЗУ, формирова- 55

Изобретение относится к электроизмерительной технике и может быть использовано при построении прецизионных цифроаналоговых преобразователей (ЦАП), а также в различного рода контрольно-измерительной аппаратуре, системах управления и передачи информации.

Известен цифроаналоговый преобразователь с автоматической коррекцией нелинейности, содержащий источник опорного напряжения, первый к второй ЦАП, анало. говый сумматор, компаратор, переключатель, первый и второй регистры, триггер, блок управления, вычислитель поправок, цифровой сумматор и датчик преобразуемого кода.

Недостатком этого преобразователя яв. ляется наличие методической погрешности при определении кодов поправок к выходному напряжению ЦАП. При этом указанная погрешность может достигать нескольких единиц младшего разряда первого ЦАП.

Кроме того, если функция преобразования первого ЦАП имеет разрывы, превышающие единицу младшего разряда, эти погре111ности не могут быть скомпенсированы.

Известен также цифроаналоговый преобразователь, содержащий первый и второй ЦАП, сумматор, усилитель переменного тока, первый и второй компараторы, первую и вторую аналоговые меры, генератор тактовых импульсов, регистр, оперативное запоминающее устройство (ОЗУ), реверсивный счетчик, первый и второй элементы И и элемент ИЛИ вЂ” НЕ.

Недостатком указанного преобразователя является значительное время, необходимое для определения кодов поправок, Наиболее близким по технической сущтор, аналого-цифровой преобразователь, амплитуды импульса;-ОЗУ, первый и второй регистры, формирователь кодов, блок синхронизации, регистр сдвига, сумматор, умножитель и накапливающий сумматор.

Функциональная схема ЦАП содержит первый и второй регистры, мультиплексор, блок в:ычисления поправок, первый ЦАП, выполненный нэ резиеторном двоичном кодоуправлявмом делителе и источнике опортель кодов, блок синхронизации, входную шину првобразуемого кода, шину занесения входного кода, шину управления режимом работы преобразователя, шину

5 10

25 готовности к приему входного кода и выходну1о шину.

Первый ЦАП является основным, Второй ЦАП предназначен для компенсации погрешностей, вносимых первым ЦАП.

Так как первый ЦАП выполнен на резисторном двоичном кодоуправляемом делителе (КУД), его погрешность ЛО(Л) описывается следующим выражением:

i — 1

Л0(Ь)- Ео2 и (2 ei — g 2 а ) AKeni, 1 =1 где Ео — выходное напряжение источника опорного напряжения; aI — разрядная цифра кода, а1<(0;1 ); ЛКад1 — погрешность элементарного делителя i-ro разряда КУД.

Учитывая. что Л диф 1 = 2 " Ь Кад, справедливо

I 1 I 1I 1

AU(h) =Ео (, al —,>, а1)ЬДиф, 1=1 2 1=1 21 где Лдиф1 = К(21 1) — (К(21 — 1) 4- К(1) )локальная дифференциальная нелинейность 1-го разряда КУД;

К(.) — реальные коэффициенты деления, соответствующие числовым значениям управляющего кода 2, 21 — 1, 1.

В последнем выражении заменим локальную дифференциальную нелинейность 1-ro разряда КУД на локальную дифференциальную нелинейность i-ro разряда ЦАП;

21 — 1 1 121 — 1

Au(t ) = (а1 — а1 ) Лдиф1, — г, 1=1 г где Лдиф1=Ео Ьдиф1 =U(2 ") — f U(2 -1)

+ 0(1) ) — локальная дифференциальная нелинейность i-го разряда ЦАП;

О(,) — реальные значения выходного напряжения первого ЦАП, соответствующие числовым значениям управляющего кода 21.1, 21 1 - 1 и 1.

Цифроаналоговый преобразователь работает в двух режимах: "Преобразование входного кода" и "Определение дифференциальных нелинейностей".

В режиме "Преобразование входного кода" управляющий код преобразуется первым ЦАП, выходной сигнал которого суммируется C сигналом поправки, формируемым вторым ЦАП. При этом код сигнала поправки вычисляется в каждом такте цифроаналогового преобразования при помощи блока вычисления поправок на основе функциональной зависимости, В режиме "Определение дифференциальных нелинейностей" при помощи энало- го-цифрового преобразователя амплитуды импульса определяются коды локальных дифференциальных нелинейностей стар1709526 ших разрядов первого ЦАП, которые зано- жающих биполярных цифроаналоговых сятся в ОЗУ и используются при вычислении преобразователей и блок формирования кодов поправок в режиме "Преобразование опорных напряжений, соответствующие выходы которого. соединены с входами опор5 ного напряжения m дополнительных

UAi(h) К1(1+ д K>)U(h)+ Кр(1+ д К )и„(Ь), умножающих биполярных цифроаналогогде UAt(h) — выходное напряжение аналого- вых преобразователей, выходы которых, кроме первого, подключены к соответствуюU(h) и Un (h) — выходное напряжение щим входам сумматора, информационные первого и второго ЦАП соответственно; 10 входы m дополнительных умножающих биК1 и Kz — коэффициенты передачи ана- полярных цифроаналоговых преобразовалогового сумматора по первому и второму телей подключены к соответствующим входам соответственно; выходам соответствующей группы выходов дК 1 и д К2 — погрешности коэффициен- дешифратора, входы которого подключены тов передачи по первому и второму входам 15 к соответствующим выходам мультиплексоаналогового сумматора соответственно. ра, вторые информационные входы котороК м роме того, го являются входной шиной

U(h) " 1+ " h,U(„) преобразуемого кода, выходы второй групК2 пы выходов формирователя кодов соединеТогда погрешность выходного сигнала 20 Hû с соответствующими входами цифроаналогового преобразователя можно синхронизации блока формирования опорзаписать следующим образом: ных напряжений, информационные входы

НОАС(п) = K2 К2 Un(h) которого подключены к соответствующим

Поэтому недостатком известного циф- информационным выходам аналого-цифророаналогового преобразователя является 25 вого преобразователя, а вход опорного навозникновение погрешности при введении пряжения объединен с входом опорного сигнала поправки, вызванной погрешно- напряжения основного умножающего цифстью коэффициента передачи аналогового роаналогового преобразователя и является сумматора по второму входу. входной шиной опорного напряжения.

Целью изобретения является повыше- 30 На фиг. 1 показана структурная схема ние точности преобразования входного ко- предлагаемого цифроаналогового преобрада зователя (ЦАП) с автоматической коррекПоставленная цель достигается тем, что цией нелинейности. в преобразователь, содержащий мульти- ЦАП с автоматической коррекцией неплексор, первые информационные входы 35 линейности (фиг. 1) содержит шину 1 входкоторого соединены с соответствующими ного аналогового сигнала, входную шину 2 выходами первой группы выходов формиро- преобразуемого кода, шину 3 управления вателя кодов, первый выход которого соеди- режимом работы преобразователя, форминен с управляющим входом рователь 4 кодов, выходную шину 5 управмультиплексора, выходы которого соедине- 40 ления, мультиплексор 6, аналого-цифровой ны с соответствующими информационными блок 7, дешифратор 8, блок 9 формирования входами основного умножающего цифроа- опорных напряжений, основной умножаюналогового преобразователя, выход которо- щий цифроаналоговый преобразователь 10, ro соединен с первым входом сумматора, дополнительные умножающие биполярные второй вход которого подключен к выходу 45 ЦАП 11, входовый сумматор 12, выходную первого дополнительного умножающего би- шину 13 преобразователя. поля рного цифроаналогового преобразова- Вторая группа информационных входов теля, выход сумматора, являющийся мультиплексора соединена с входной шивыходной информационной шиной, соеди- ной 2 преобразуемого кода, первый вход нен с информационным входом аналого- 50 формирователя кодов соединен с входной цифрового преобразователя, вход шиной 3 управления режимом работы ïðåсинхронизации которого подключен по вто- образователя, а третий выход — с выходной рому выходу формирователя кодов, а выход шиной 5 управления, первый вход основнототовности результата соединен с первым го умножающего ЦАП 10 соединен с входвходом формирователя кодов, второй вход 55 ной шиной 1 аналогового сигнала. выход которого является входной шиной управле- сумматора 12 соединен с выходной шиной ния режимом, а третий выход является вы-, 13 преобразователя и с вторым входом анаходной шиной управления, введены лого-цифрового блока 7, первый вход котодешифратор, (m — 1} дополнительных умно- рого соединен с пятым выходом, а второй выход — с вторым входом форглирояателя 4

1709526 кодов, группа первых информационных выходов которого соединена с первой группой информационных входов мультиплексора, групапа информационных выходов которого соединена с группой информационных. входов основного умножающего ЦАП 10, выход которого соединен с:первым входом сумматора 12, первый вход блока 9 формирования опорных напряжений соединен с входной шиной 1 аналогового сигнала, группа вторых информационных входов — с группой четвертых информаЦионных -выходов формирователя 4 кодов, группа третьих информационных входов — с группой первых информационных выходов аналого-цифрового блока 7 соответственно, соответствующие выходы группы информационных выходов блока 9 формирования опорных напряжений соединены с первыми входами соответствующих дополнительных умножающих биполярных. ЦАП 11, выходы которых соединены с соответствующими входами сумматора 12, а группы вторых информационных входов — с соответствующими группами информационных выходов дешифратора 8, группа информационных входов которыхсоединена с группой информационных выходов мультиплексора 6, третий вход которого соединен с вторым выходом формирователя 4 кодов. .На фиг. 2 представлена функциональ. ная схема блока формирования опорных напряжений, который содержит а регистров

22 и умножающих биполярных цифроаналоговых преобразователей 23. .На фиг, 3 представлена функциональная схема аналого-цифрового блока 7, содержащего усилитель 24 переменного сигнала, первую 25 и вторую 26 аналоговые меры, первый 27-1 и второй 27-2 компараторы, одновибратор 28, первый 29- 1 и вто. рой 29-2 двухвходовые элементы И, трехвходовый элемент ИЛИ 30, реверсивный счетчик 31.

На фиг, 4 представлена функциональная схема формирователя 4 кодов, содержащего. первый 32-1 и второй 32-.2 одн©вибраторы, двухвходовый элемент

ИЛИ 33, генератор 34, RS-триггер 35. Отриггер 37, регистр 36, m-входовый элемент

ИЛИ 39, реверсивный счетчик 40; (m+2) двухвходовых элемента И 38 — 1, 39-2 и 41-1, ..., 41-m.

На фиг. Б представлена функциональная схема дешифратора 8, содержащего m инверторов 42, Как и для прототипа, погрешность функции преобразования основного умножающего ЦАП 10 определяется следующим выражением:

1 i 121 1 (а } Еа { а! — а а! } аадиф1,(lj, 1=1 i=1 2 где Ее} — напряжение входного сигнала на шине 1;

Л диф — дифференциальная нелинейность 1-го разряда ЦАП.

Сумма в круглых скобках представляет собой числовое значение i-1 младших раз10 рядов управляющего кода (а{-1, ..., a1 ), Графики составляющих зависимости (1) имеют вид, представленный.на фиг. 6.

Из анализа этих зависимостей сделан вывод, что каждый "скачок" определяется

15 дифференциальной нелинейностью только одного разряда, причем "скачок" от i-ro разряда проявляется при смене разрядных цифр управляющего кода с (а < { = 1; а{- i =О) на (ai

20, "разрядов; номера которых больше i.

Запишем i-e слагаемое суммы выражения (1) в виде

OU(h, Едим 1=Е,(— О,-аи a } 6уиф; .

)<

Нетрудно показать, что эта зависимость легко форМируется при помощи двухполярного умножающего ЦАП, у которого опорное напряжение равно Е< 2 а управляюЬдиф{

30 щий код определяется следующими соотно.шениями:

Ь|=аь

Ь{<{=а1, 8 этом случае выходное напряжение

ЦАП можно записать в виде

1 2}

ОцАп(Ь)=Ео Ьдиф (— — g bi )

2!

1 2}

40 0цдп= Ео Лдйф { (— ai —, 5, а{, } (3)

2 i -=1 2!

Сравнение правой части выражений (2) и (3) показывает их полную идентичность, Таким образом, используя описанные двухь1 полярные умножающие ЦАП, можно скомпенсировать нелинейность функции преобразования основного ЦАП 10, Предлагаемый ц{гфроаналоговый пре20 образователь с автоматической коррекцией нелинейности работает в двух режимах:

"Преобразование входного код (и "Определение дифференциальных нелинейностей".

В режиме "Преобразование входного

25 кода" сигналом на шине 15, поступающим с выхода формирователя 4 кодов на управляющий вход мультиплексора 6, выходы по-следнего соединяются с шиной 2 данных преобразуемого кода. В результате управ30 ляющий код с шины 2 поступает на информационные входы основного ЦАП 10 и

1709526

10 п 1 -1 ZJ1 (Ц И1;)(а;-):а,, )ЬуисР

4=!

Очевидно, чтопри в полнениира ва и равенстК =-KI K1) 35 последний член выражения (5) компенсируется с заданной точностью.

Число m компенсируемых старших разрядов определяется дифференциальными нелинейностями младших разрядов ЦАП. В 40 большинстве случаев достаточно выбирать я=6 — 8, При поступлении единичного импульса по шине 3 управления режимом работы преобразователь переводится в режим "Опреде- 45 ление дифференциальных нелинейностей".

При этом единичным сигналом на шине 15 с выхода формирователя 4 кодов выходы мультиплексора 6 соединяются с шиной 14. Одновременно в регистр 36 сдвига заносится 50 кодовая комбинация 00„.01, Присутствие хотя бы одной единицы на выходах регистра

36 сдвига переводит последний сигналом с выхода элемента ИЛИ 39 в режим сдвига информации. Кроме того, единичным сигна- 55 лом на шине 15 запускается генератор 34 импульсов. В результате на выходах 14 счетчика 40 формируется периодически повторяющаяся последовательность смежных кодов дешифратора 8. При этом на выходной шине

13 преобразователя формируется сигнал

U(h) Ео К K(h) + f K>Unr(h), (4)

I =n — m+1 гле K(h) — реальная функция преобразова5 ния основного ЦАП 10;

1 — 1

K(h } =a! — +ЛК(Ь };

2Р

„) литл, Ео

UnI(h) Выходные напряжения дополни, тельных ЦАП 11;

К и К) — коэффициенты передачи аналогового сумматора по каждому из входов.

На аналоговые входы ЦАП 11 с выходов

21 блока 9 формирования опорных напряжений поступают напряжения, пропорциональные дифференциальной нелинейности каждого l-ro разряда, т.е. К1)Ео Лдиф), а на 20 соответствующие информационные входы

ЦАП 11 с выходов 20 дешифратора 8 поступают кодовые комбинации 1 a), a)-1; ... а1) . В результате выходной сигнал преобразователя на шине 13 с учетом (3), (4) можно пред- 25 ставить в виде

u(l)=(Yi КЬ) ):К ЛУ1(К (-а - »а

)=.- 41+1 2 . 4 или, @ ) .„— z "- (, - г

°;, г. °,,Р,, -;Г " 30

h о (an-m+1 = 1; а)-I = 0 )

h-1 ю(а) o =0; a)

При этом на выходной шине 13 преобразователя формируется переменный сигнал прямоугольной формы, амплитуда которого несет информацию о дифференциальной нелинейности (n-m+1)-го разряда.

Амплитуду переменного. сигнала можно представить.в виде

Unc = UAI(h) — ОА)((! — 1) = ЕоК (K(h)—

-к(м))+ g K<(U r(h) — и >(ь-1)). ! =n — m+!

Из (1) следует, что при смене смежных кодов h u h — 1 и

KI (UnI(h) — UnI(h 1) J = 0.

I =n — m+2

Поэтому

Uhc Ео К (—.„+ Ьяиф) ) + К) (Uql (h ) Оп) (h — 1 )):

I !ри помощи аналого-цифрового блока 7 амплитуда Оос переменного сигнала сравнивается с выходными сигналами аналоговых мер 25 и 26, номинальные значения выходных сигналов которых равны соответ-. ственно:

U! = Ку(Ео — — Л):

2"

02 = Ку(Ео — + Л), 1

2п где Л вЂ” допускаемое отклонение реальной единицы младшего разряда от номинальной.

В зависимости от результата сравнения компараторы 27 — 1 и 27 — 2 вырабатывают сигналы, по которым импульсами с выхода одновибратора 28 код 19 счетчика 31 увеличивается или уменьшается на единицу и им-. пульсом на шине 16 — (n-в+1) заносится в регистр 22-m. Этот код при помощи дополнительного двухполярного умножающего

ЦАП 23 — m преобразуется в аналоговый сигНаЛ ЕоК1())-m+1), КОтОрЫй яВЛяЕтСя ВХОДНЫМ сигналом двухполярного умножающего

ЦАП 11 — m, компенсирующим дифференциальную нелинейность (n-m+1)-го разряда основного ЦАП 10. Следящий режим работы аналого-цифрового блока 7, ЦАП 23 — m и 11—

m будет продолжаться до тех пор, пока не будет выполнено неравенство

U1 < KyUnc < 02, (6) .где Ky — коэффициент усиления усилителя 24 переменного сигнала. При этом обеспечивается выполнение условия

Ео К Лдиф(п-в+1) =-K(n-m+1) (Un(n m+1)(h)

Un(n-m+1)(h — 1) ) или с учетом-(4) и (5)

K =-KIK1I, 12 что позволяет компенсировать дифферен- соединены с соответствующими информациальную нелинейность(п-а+1)-го разряда. ционными входами основного умножающеПри выполнении неравенства 6 анало- ro цифроаналогового преобразователя, го-цифровойблоквырабатываетимпульсна выход которого соединен с первым входом шине 18, по которому в регистре 36 сдвига 5 сумматора, второй вход которого подключен производится сдвиг информации. На выхо- к выходу первого дополнительного умножаюдах регистра 36 сдвига устанавливается ко- щего биполярного цифроаналогового преобдовая.комбинация 00...010, Дальнейшие разователя, выход сумматора, являющийся

m-1.тактов работы преобразователя в этом выходной информационной шиной, соединен режиме аналогичны первомутакту., 10 с информационным входом аналого-цифраПо окончании m-го такта с приходом вага преобразователя, вхадсинхронизации единичного импульса по шине 18 в регистр которого подключен к втаромувыходуформи36 сдвига на выходах последнего устанавли- рователя кодов, а выход готовности результавается кодовая комбинация 0...0. В резуль- та соединен с первым входом тате на выходе элемента ИЛИ 39 15 формирователя кодов, второй входкатарого установится нулевой сигнал, переводящий является входной шиной управления режирегистр 36 сдвига в режим занесения w- мом, а третий выход — выходной шиной упформации, Одновременно выходным сигна- равления, отличающийся тем, что, с лом одновибратара 32-2 RS-триггер 35 . целью повышения точности преобразавапереводится в нулевое состояние, а выход- 20 ния, в него введены дешифратор, т-1 доной сигнал RS-триггера 35поступает на вы- полнительных умножающих биполярных хадную шину 5 управления. При этом цифроаналоговых преобразователей и блок преобразователь переводится в режим формирования опорных напряжений, соотреобразование входного кода".

Таким б ветствующие выходы которого саедине динены с м образом, па сравнению с 25 входами опорного напряжения соответствупрототипом в предлагаемом. устрой-: ащих m дополнительных умножающих бипо-. стве достигается повышение точности лярных цифроаналоговых преобразователей, цифроаналогового преобразования за счет выходы которых, кроме первого, подключены компенсации погрешностей коэффициен- к соответствующим с третьего по (m+1)-й вхатов передачи аналогового сумматора при 3О дам сумматора, информационные входы m снижении требований к очности компонен- дополнительных умножающих биполярных цифроаналоговых преобразователей подОсновной ЦАП 10 (фиг, 2) выполнен на ключены к соответствующей группе аыхомикросхеме 572ПА2, дополнительные. ЦАП дов дешифратора входы (фиг. ) и Ц П 3 (фиг. 3) блока 9 форми- 35 подключены к соответствующим выходам рования опорных напряжений выполнены мультиплексора; вторые информационные на К572ПА1Г, формирователь 4 кодов, ана- входы которого являются входной шиной лого-цифровой блок 7, дешифратор 8, блок преобразуемого кода, выходы второй груп9 формирования опорных напряжений (фиг, пы выходов формирователя кодов соедине2) выполнены на микросхемах К544УД1, 40 ны с соответствующими входами

КЬ21САЗ и микросхемах серии К561. синхронизации блока формирования опор.! Применяя К-разрядные даполнитель- ных напряжений, информационные входы ные ЦАП 11 и 24, обеспечивается повыше- которого подключены к. соответствующим ние линейности цифроаналогового информационным выходам аналого-цифр— к-1 аго-цич ропресбразования в 2 раз при соблюдении И5 ваго преобразователя, а вход опорного напринципа суперпозиции в основном ЦАП пряжения объединен с входом опорного

10. Если принцип суперпозиции в основном напряжения основного умножающего цифЦАП нарушается, предельно достижимая роаналоговога преобразователя и является линейность преобразования ограничена по- входной шиной опорного напряжения. грешностями несуперпозиционного харак-. 50 2. Преобразователь па и. 1, о т л и ч а ютера. и составляет 0,001 .

Ф шийся тем, что блок формирования споо р мул а изобретения ных напряжений выполнвн в виде m регист- я опор1. Цифроаналоговый преобразователь с рав и m умножают их биполярных автоматической коррекцией нелинейности, цифроаналоговых преобразователей, выхссадержащиймультиплексор. первыеинфор- 55 ды которых являются соответствующими мационные входи которого соединены с со- выходами блока, а информационные входыответствующими выходами первой группы подключены к соответствующим выходам выходов формирователя кодов, первый вы- соответствующего регистра, входы синхроход которого соединен с управляющим вха- низации которых являются соответствуюдом мультиплексора, выходи которого щими входами синхронизации блока, 1709526 информационные входы первого регистра объединены с соответствующими информационными входами остальных m-1 регистров и являются соответствующими информационными входами блока, вход 5 опорного напряжения первого умножающего биполярного цифроаналогового преобразователя объединен с, ВХОДами опорного напряжения остальных m — 1 умножающих биполярных цифроаналоговых преобраэо- 10 вателей и является входом опорного напряжения.

3, Преобразователь по и. 1, о т л и ч а юшийся тем, что аналого-цифровой преобразователь выполнен В виде усилителя пе- 15 ременного сигнала, первой и второй аналоговых мер, первого и второго компараторов, первого, второго и третьего элементов И, реверсивного счетчика импульсов и одновибратора, вход которого является вхо-. 20 . дом синхронизации аналого-цифрового преобразователя, а выход соединен с пер-. выми входами первого и второго элементов

И и с неинвертирующим входом третьего элемента И, выход которого является выхо- 25 дом готовности результата аналого-цифрового преобразователя, а первый и второй инвертирующие входы объединены с вторыми Входами соответственнО первого и Второго элементов И и подключены к.выходам 30 соответственно первого и второго компараторов, первые входы которых соединены с выходами соответственно первой и второй аналоговых мер, а вторые входы подключены к выходу усилителя переменного сигна- 35 ла, ВМОд кОторого . является информационным входом аналого-цифрового преобразователя, выходы первого и второго элементов И соединены соответственно с входом суммирования и вычитания 40 реверсивного счетчика и импульсов, выходы которого яВляются информационными Выходами аналого-цифрового преобразователя. ., 45

4. Преобразователь по.и. 1, о т л и ч а юшийся тем, что формирователь кодов выполнен в виде первого и второгоодновибраторов, RS- и О-триггеров, первого и . второго элементов ИЛИ, генератора импульсов, регистра сдвига, m+2 элементов И и реверсивного счетчика импульсов, выходы которого являются первой группой выходов формирователя кодов, а информационные входы объединены с соответствующими входами первого элемента ИЛИ, с первыми входами соответствующих первых m элементов И и подключены к соответствующим выходам регистра сдвига, вход управления которого объединен с входом первого одновибратора и подключен к выходу первого элемента ИЛИ, а вход синхронизации объе. динен с S-входом О-триггера и подключен к выходу второго элемента ИЛИ, первый вход которого является первым Входом формиро- . вателя кодов, а второй вход объединеЪ с

S-входом RS-триггера, й-вход которого подключен к выходу первого одновибратора, инверсный выход является третьим выходом формирователя кодов, а прямой выход — первым выходом формирователя кодов и соединен с входом стробирования генератора импульсов, выход которого подключен к первым входам (а+1)-го и (m+2)ro элементов И и к входу синхронизации D-триггера, инверсный выход которого соединен со своим О-входом и вторым входом (я+1)-ro элемента И, а прямой выход — с вторым входом

-(е+2)-го элемента И, выход которого является вторым въ1ходом формирователя кодов и соединен с входом разрешения записи информации реверсивного счетчика импульсов, вычитающий вход которого объединен с втооыми входами первых m элементов И и подключен к выходу (. в+1)-ro элемента И, вход второго одновибратора является вторым входом формирователя кодов, а выход соединен с вторым входом второго элемента ИЛИ, вход последовательного ввода информации регистра сдвига объединен с входами, кроме первого, параллельного ввода информации регистра сдвига и подключен к шине логического нуля, первый вход параллельного ввода информации регистра сдвига подключен к шине логической единицы, выходы m первых элементбв И являются второй группой выходов формирователя кодов.

q;rggggg

-ml1)

r) 1709526

Составитель A.Äàíèëoâ

Редактор М.Бандура . Техред М.Моргентал Корректор H.Ревская

Заказ И4 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101