Устройство для передачи сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, может быть использовано для синхронизации вычислительных систем и позволяет сократить число передающих линий. Цель изобретения - расширение функциональных возможностей за счет обеспечения передачи кодированных тактовых сигналов. Это достигается за счет введения модулятора 9. детектора 17 и регистра 3 сдвига. 3 з,п. ф-лы. 10 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (54)5 Н 03 М 5/12

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛ6СТВУ (21) 4777347/24 (22) 02.01,90 (46) 30.01.92. Бюл. М 4 (72) П.О.Егорьев и Б.В.Кушелев. (53) 681.3(088.8) (56) Вопросы радиоэлектроники Серия ЭВТ, вып. 9, 1979, с. 105-110.

Авторское свидетельство СССР

Q 1385295, кл. Н 03 M 5/12, 1986. (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ СИГНАflGB

Изобретение относится к вычислительной технике и может быть использовано для синхронизации вычислительных систем.

Цель изобретения — расширение функциональных возможностей .за счет обеспечения передачи кодированных тактовых сигналов.

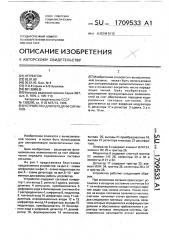

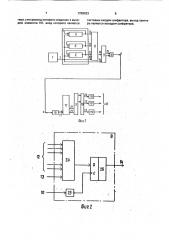

На фиг.1. представлена блок-схема предлагаемого устройства; на фиг.2 — схема шифратора; на фиг.3- схема модулятора; на фиг.4 — схема детектора; на фиг.5-10 — временные диаграммы работы устройства.

Устройство содержит тактовый генератор 1, его выход 2, регистр 3 сдвига, распределитель 4 импульсов, преобразователь 5 цифрового кода в биполярный, счетчики 6 и

7 распределителя 4, шифратор 8, модулятор

9, тактовый вход 10 шифратора, вход 11 модулятора, информационные входы 12 и 13 шифратора, выход 14 шифратора, выходы 15 модулятора, преобразователь 16 биполяр- ного кода в цифровой, детектор 17, дешифратор 18, формирователи 19 импульсов, (и) 5U(и 1 709533 A l (57) Изобретение относится к вычислительной технике, может быть использовано для синхронизации вычислительных систем и позволяет сократить число передающих линий, Цель изобретения расширение функциональных возможностей за счет обеспечения передачи кодированных тактовых сигналов. Это достигается за счет введения модулятора

9, детектора 17 и регистра 3 сдвига. 3 з,п, ф-лы, 10 ил.

1 выходы 20, выходы 21 преобразователя 16, выходы 22 детектора и выходы 23 дешифратора.

Шифратор 8 содержит элемент ИЛИ 24, элемент НЕ 25 и триггер 26.

Модулятор 9 содержит счетный триггер

27, элемент НЕ 28, селекторы 29 и 30 и элементы И 31 и 32.

Детектор 17 содержит триггер 33,- эле- С мент ИЛИ 34, триггер 35, селекторы 36 и 37 Q и триггер 38, (л

Устройство работает следующим обра- (Д зом. 6д

При включении питания происходит установка в исходное состояние счетчиков 6 и

7, на информационных входах которых заранее задан код начала отсчета, После того, как на входах счетчиков появляется частота, счетчики начинают отсчет времени периодов следования тактовых импульсов, величина которых определяется коэффициентом деления и обусловлена требованиями к характеру тактовых импульсов системы. Одновременно начинается отсчет времени

1709533

35 поступает на вход преобразователя 5, в ка-.40 честве которого используется обычный импульсный трансформатор, с выхода

50 цикла кодирования информации на счетчике 7 цикла кодирования. При появлении нэ выходе 12 переполнения счетчиков 6 сигналов, обозначающих конец периодов следования тактовых импульсов, выходные сигналы поступают на входы сброса в ноль счетчиков 6 и информационные входы шифратора 8. Работа счетчика 7 происходит аналогично. Выход 13 счетчика 7 поступает на вход установки в ноль счетчика и синхровход шифратора 8. Одновременно на синхровход 10 шифратора 8 поступает опорная частота от генератора 1. Фазовые соотношения между счетчиками 6 и 7 задаются при начальной установке по питанию, а в дальнейшем подтверждаются через обратную связь с выхода счетчиков на устэйовочные входы. Так кэк на входы шифратора 8 поступает комплект. периодических последовательностей импульсов с фиксированными фазовыми соотношениями, кратными периоду тактовой частоты и периодический сигнал цикла кодирования, так же с кратным периодом, то в шифраторе 8 возможно провести преобразование периодов следования сформированных счетчиками 6 тактовых сигналов в цифровой код с разрядностью, определяемой периодом следования выходных импульсов, счетчика 7 цикла кодирования.

Сформированная в шифраторе 8 непре-. рывная последовательность цифровых кодограмм, содержащая в каждой кодограмме признак отсчета разрядов, определяемый счетчиком 7, поступает на вход 14 модулятора 9, где преобразуется к виду, пригодному для формирования структуры импульсов какого-либо стандартного кода интерфейсного типа, Сигнал с выхода 15 модулятора 9 которого сигнал поступает на вход преобразователя 16.

На выходах 21 преобразователя 16, подключенных к входам детектора 17, сформирован сигнал, соответствующий структуре принятого в системе интерфейсного кода. который после детектирования подается на входы регистра 3, с выхода которого на входы дешифратора 18, на выходах 23 появляется цифровая кодограммэ тактовых сигналов, сформированных счетчиками 6, Дешифратор 18 совместно с регистром

3 сдвига при получении на вход цифровой кодогрэммы от детектора 17 для правильной расшифровки фазовых соотношений сигналов производит привязку начала своей работы к признаку начала цикла кодирования, сформированного счетчиком 7 синх5

15 ронно, во всех каналах резервирования системы, что позволяет на выходах всвх дешифраторов абонентов получить необходимый набор тактовых сигналов с периодами и цифровыми соотношениями, заданными счетчикамИ

6, С выходов 23 дешифратора 18 тактовые сигналы поступают на вход формирователей 19, где при необходимости может производиться корректировка и деформиравание каждого отдельного такта, поступающего в дальнейшем на выходы 20.

Работа шифратора происходит следующим образом.

При поступлении на вход дешифратора

18 сигналов счетчиков 6 и 7 на выходе элемента ИЛИ 24 появляется суммарный сигнал, в котором учтены соотношения сигналов, а также имеют место случайные помехи, определяемые соотношением задержек реальных счетчиков.

Импульсный сигнал с выхода элемента

ИЛИ 24 поступает на информационный вход триггера, на синхронизирующий вход которого подается инверсная частота с выхода генератора 1.

При этом нэ выходе триггера 26 формируется сигнал, содержащий в себе информацию о фазовых соотношениях сигналов, но не содержащий случайных помех.

Работа модулятора 9 происходит следующим образом.

На информационный вход 11 триггера

27 подается опорная частота с выхода, генератора 1. При этом на выходе триггера 27 формируются два такта частоты с периодом вдвое большим, чем входной. Эти такты поступают на вторые входы селекторов 29 и 30, Нэ управляющие входы подается суммарный сигнал с выхода шифратора, причем нэ первый селектор подаются прямые, а на второй — инверсные сигналы. Разводка сигналов по входам селекторов 29 и 30 выполнена таким образом, что на выходах 15 элементов формировались две идентичные последовательности кодовых сигналов, пригодных для формирования предварительных кодограмм одного из стандартных интерфейсных кодов, в данном случве для биполярного. фазоманипулированного с возвращением к нулю.

На элементах И 31 и 32, подключаемых к выходам селекторов 29 и 30. происходит окончательная модуляция сигналов опорной частоты, являющейся в данном случае несущественным.

Работа детектора 17 происходит следующим образом. На вход детектора подается информация с выхода 21 преобразователя

16, точно повторяющая информацию с выхода модулятора 9. При этом нэ выходе эле. 1709533 мента ИЛИ 34 из кодограмм вы еля опорная частота 1, а с помо ью т д ется выходом детектора, выходы регистра сдвига щ риггеров соединены с входами дешифратора, 33 и 35 и селекторов 36 и 37 выделяется 2. Устройство по п.1, о т л и ч а сигнал; содержащий инфо ма ию о ф и информацию о фа- с я тем, что модулятор содержит счетный эовых соотношениях сигнало налов, сформи- 5 триггер, два селектора, элемент НЕ и в рованных счетчиками 6 и 7. Т игге 38 ент и два и и . риггер 38 элемента И, причем счетный вход счетного а соединен с первым входом первопреднаэначен для защиты последующей схе- триггера мента, первым входом второго элемы от помех, вызванных случайным соотно- го элеме И шением задержек элементов схемы, выходы, мента И и я т игге а38иэл мента и является информационным р р и элемента WIN 34 являются 10 входом модулятора и я выходами 22 детектора. лятора, прямой выход счетного

Н а. триггера соединен с первыми информациа информационный вхо д регистра 3 - онными входами первого и второго селектоподается кодовая последовательность им- ров ов, вторые информационные входы пульсов с выхода 22 детектора 17, а на син- которых с хровход подается частота с выхо а 22 1 рых соединены с инве сным выхо м выхода 5 счетного триггера, вход элемента НЕ соедиэлемента ИЛИ34. При этом число аз я ов р р д нен с первым управляющим входом первого регистра 3 выбирается таким образом, что . селектора с втор за инте вал в м вторым управляющим входом р ремени, определяемый счетчи- второго селектора и являет я ком 7 цикла коди ования ктора и является синхровходом стояние все аз я ы. Вы д р сменяютceOe со- модулятора, выход элемента НЕ р р д . деление тактовых 20 первым управляющим входом второго сесоединен с сигналов,эквивалентныхсигналамнавыхо-. лекто а и вт де счетчик в 6 7 то ом 18 о и, производится ешиф ад фра- первого селектора, выходы первого и второтором, разрядность которого также ro элементов И

on е еля р д яется исходя из числа исходных первым и о нтов являются соответственно тактовых сигналов. Сигналы с выхода 23 25 3. У вым и вторым выходами мод лято а. стройство по п.1, о т л и ч а ю е ду р ° дешифратора поступают на вход о ми ощеевателей 19 ф р р с я тем, что детектор содержит три триггера, вателей 9, в качестве которых могут ис- элемент ИЛИ и ва л пользоваться на и, б и два селектора, причем вход

133 АГЗ пр мер, однови ато ы или аналогичные. р р установки в единицу первого триггера.соединен с первым входом элемента ИЛИ, перФ

30 вым информационным входом первого

1. Уст ормула изобретения селектора и является первым входом детекстройство для передачи сигналов, тора, вхо сб о

Од с рОса первого триггера соеди" е тактовый генератор, рас- нен с вторым входом элемента ИЛИ и фр р, является вторым входом детектора, выхо прео разователь цифрового кода в бипо- 35 первого триггера соединен с информацион кода в цифровой, дешифрато и г и, дешифратор и группу которого соединен с выходом элемента, с синхровходом третьего триггера и ормирователей импульсов, причем выхо- ИЛИ ды дешифратора соединены с входами фор- является пе вым вых мирователей импульсов г ппы вых яется первым выходом детектора, пряв группы, выходы 40 мой выход второго триггера соединен с втокоторых являются выходами ст ойства о т л и ч а ю щ е е с я .тем, что, с ель у р ства, рым информационным входом первого целью селектора, инверсный выход второго триггерасширения функциональных возможно- ра соединен с первы чет обеспечения пере-. входом второго селектора, первый управлядачи кодированных тактовых. сигналов, в 45. ющий вход кото ого

A вход о оро о соединен с вторым уподулятор,детектор и регистр, равляющим входом второго селекто а сдвига, причем выхо тактовог r д го генератора вторым информационным входом вто ого соединен с синх овхо ом м р д одулятора и селектора и инверсным выходом первого рого входом распределителя импульсов, выходы селектора, выход второго селектора сое икоторого соединены с вхо ами ши д фратора. 50 нен с информационным входом третьего ход второго селектора соедивыход которого соединен с инфо ма и ф рм цион- триггера, первым и вторым управляющими ным входом модулято а, выхо ы к

\ соединены с входами и еоб а в р, д которого входами первого селектора, выход третьего р р зо ателя уф- триггера является вторым выходом детекрового кода в биполярный, выход которого тора. соединен с входом преобразователя бипо- 55 4. Устройство по п.1 ство по п.,отл ича ющеесое инены с в д в цифровои, выходы которого с я тем, что шифратор сооде

R ходамидетектора, первый вы- ИЛИ, триггер и элемент НЕ, причем вхо ы держит элемент ход которого, соединен с инфо н информационным элемента ИЛИ являются информационными л мент, причем входы входом первого разряда регистра сдвига, входами шифратора, выход элемента ИЛИ синхровход которого соединен с вторым соединен с информационным входом триг1709533 гера, синхровход которого соединен с выходом элемента НЕ, вход которого является тактовым входом шифратора, выход триггера является выходом шифратора.

1709533

1709533

4их щгиро5ыимя щысеобик 14 T4<

gf8 1 Мю8 4< 3

Тцк

Ал. М урж иум

О ®Ь

P gcrrn д:С

rro dywarnepa Ц я Дфоп ф

o t А

Фих. дУ. ци д ge7cry з . отсеяв тяп

1709533

1709533

fxePez (г(}

Регпе Фслюорса

Air. Уетмл ар г

А . ЭОМчДэ аагариа /

Ъ В

dwAAate e 7ч. к

В

Ъ Яс бибцммт ТАКТ .ъ . 6 вкБмбамня 74478

1709533

goal

gg)l

1709533

5I

W х

Составитель Н. Торопова

Техред М, Моргентал Корректор M. Шароши

Редактор Т. Горячева

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 437 Тираж Подписное

8НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушскэя наб„4/5