Устройство для измерения девиации частоты линейно-частотно- модулированного колебания

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано для измерения девиации и скорости изменения частоты. Устройство для измерения девиации частоты линейно-частотно-модулированного колебания содержит управляемый генератор 1, фазовый детектор 2, 3, фильтр 4 нижних частот, усилитель 5 постоянного тока, генератор 6 пилообразного напряжения, эталонный генератор 7, формирователь 8 импульсов, блок 9 нормирования , блок 10 индикации, кварцевый генератор 11. Введение формирователя 12 сигналов установки режимов измерения позволяет расширить функциональные возможности устройства за счет измерения скорости изменения линейночастотно-модулированного колебания. 3 з.п. 6-лы, 6 ил.

COIO3 СОВЕТСКИХ

Хй

РЕСПУБЛИК

А1

0% 111) Щ)э С 01 Р, 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ н автаосюим саидатеъстем

ГОСУДАРСТВЕККЬ9 КОМИТЕТ

f0 ИЭОЬРЕТЕКИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (2!) 4760438/21 (22) 20.11.89 (46) 07.02,92. Бюл. Р 5 (72) А.Л. Сицко, В.II. Лапшин, В,F,. Кучинский и A.È, Хохлов (53) 621.317(088.8) (56) Авторское свидетельство СССР

Р 652500, кл, О 01 Р 23/00, 1979, Авторское свидетельство СССР

Р 1190281, кл, О 01 Р 23/00, 1985. (54) УСТРОЙСТВО,пЛЯ ИЗИЕРЕНИ»» ДЕВИАЦ1Ш ЧАСТОТЫ ЛИНЕЙНО-ЧАСТОТНО-ИОПУЛИ

РОВАННОГО I ОЛЕВАНИЯ (57) Изобретение может быть использовано pJIS» измерения девиации и скорости изменения частоты. Устройство для измерения девиации частоты линейно-частотно-модулированного колебания содержит управляемый генератор 1, фазовый детектор 2, клн ч 3, фильтр 4 нижних частот, усилитель 5 постоянного тока, генератор 6 пилообразного напряжения, эталонньп» генератор 7, формирователь 8 импульсов, блок 9 нор. мирования, блок 10 индикации, кварцевьп» генератор 11. Введение формирователя 12 сигналов установки режимов измерения позволяет расширить функциональные возможности устройства за счет измерения скорости изменения линейночастотно-модулированного колебания.

3 з.п. h-лы, 6 ил.. 1711087

Изобретение относится к области радиоизмерений и предназначено для использования в радиолокационных станциях для измерения девиации и скорос5 ти изменения частоты.

Цель изобретения — расширение Функциональных возможностей устройства.

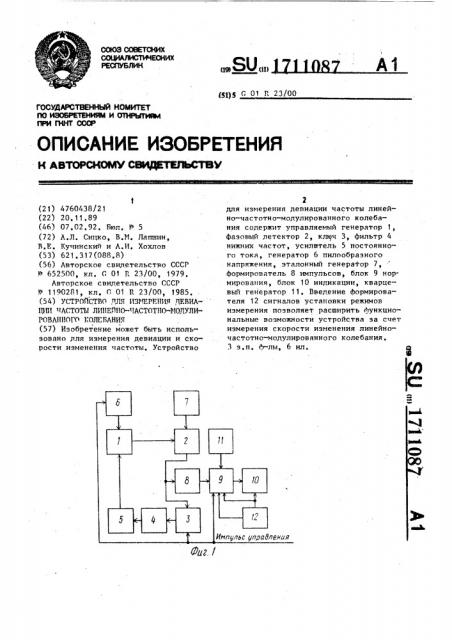

На фиг. 1 изображена функциональная,схема устройства; на Фиг. 2—

Функциональная схема блока нормирования; на Фиг. 3 - Функциональная схема блока управления; на фиг, 4-6— эпюры сигналов в контрольных точках.

Устройство содержит управляемый генератор 1, фазовый детектор 2, ключ 3, Фильтр 4 нижних частот, усилитель

5 постоянного тока, генератор 6 пилообразного напряжения, эталонный генератор 7, формирователь 8 импульсов, 20 блок 9 нормирования, блок 10 индикации, кварцевый генератор 11, формирователь 12 сигналов установки режимов измерения.

Блок 9 нормирования содержит блок

13 управления, реверсивный счетчик 14, блок 15 установки коэФфициента деления, делитель 16 счетчиковый с переменным коэффициентом деления, второй 17 и третий 18 элементы задержки, двоичный счетчик 19, логический сумматор 20, накопитель 21, коммутатор 22, блок 23 элементов НЕ, : двоичный счетчик 24 с предварительной записью информации, первый эле35 мент 25 задержки, двоично-десятичный счетчик 26, блок 27 памяти.

Блок 13 управления содержит первьп элемент ЗИ 28, первый элемент

2И 29, первьп элемент 2ИЛИ 30, первый триггер 31, второй элемент 2ИЛИ

32, второй 33 и третий 34 элементы

2И, первьпt элемент HE 35, первый формирователь 36, третий элемент 2ИЛИ

37, второй триггер 38, четвертьп 39 45 и пятый 40 элементы 2И, второй формирователь 41, четвертьп элемент 2ИЛИ

42, второй элемент НЕ 43, третий формирователь 44, четвертый формирователь 45, второй элемент ЗИв46, шестой элемент 2И 47, третий 48 и четвертый

49 триггеры, элемент 50 задержки, пятый элемент 2ИЛИ 51, третий элемент ЗИ 52, счетчик 53 с предварительной записью информации, блок 54

55 элементов НЕ, коммутатор 55, третий элемент НЕ 56, формирователь 57 кодов.

Устройство работает следующим образом.

Ло приходя импульса управления ключ 3 открыт. Если напряжения с выходов управляемого генератора 1 и эталонного генератора 7 не равны по частоте и Фазе, то на выходе фазового детектора 2 появляется напряжение рассогласования, которое через ключ

3, фильтр 4 нижних частот, усилитель

5 постоянного тока поступает на управляемьп генератор 1, удерживая разности частот и фаз между сигналами управляемого и эталонного генераторов равными нулю. Таким образом, в отсутствие модуляции сигнал на выходе фазового детектора 2 отсутствует.

В момент прихода импульса управления (Фиг.4a) ключом 3 разрывается цепь Аазовой автоподстройки частоты, запускается генератор 6 пилообразного напряжения (фиг.4о), частота сигнала на выходе управляемого генератора 1 увеличивается по линейному закону (фиг.45), и с выхода фазового детектора 2 сигнал разностной частоты (Фиг. 42) подается на формирователь 8 импульсов, вырабатывающий импульсы в моменты перехода напряжения низкочасt1 тстной синусоиды через уровень 0 (*иг. 4ф . Сформированная пачка импульсов подается на блок 9 нормирования.

В режиме измерения девиации частоты на втором выходе формирователя

12 .сигналов установки режимов измерения напряжение соответствует уровню логического нуля, которое подается в блок 10 индикации, блок 13 управления и на управляющие входы блока

15 установки коэффициента деления и коммутатора 22, Б начале работы на первом выходе формирователя 12 сигналов установки режимов измерения формируется короткий положительный импульс (Аиг.50), которьп через четвертьп элемент 2ИЛИ 42, второй триггер 38 переводит в единичное состояние (Фиг.50), разрешая прохождение импульсов через шестой элемент 2И 47.

Четвертый формирователь 45 по фронту импульса управления формирует импульс (фиг,533, который через шестой элемент 2И 47 третий триггер 48 переводит в единичное состояние (фиг,5 ), разрешая прохожпение импульса управления через второй элемент ЗИ 46, импульса сброса через пятый элемент

2И 40, и по четвертому выходу блока

13 управления как импульс установки в

1711087

"0" поступает на реверсивный счетчик

14, счетчиковый делитель 16 с переменным коэффициентом деления, двоичный счетчик 19, двоичный счетчик 24 с

5 предварительной записью инАормации, двоично-десятичньп счетчик 26, накопитель 21.

Имггульс управления (фиг.5$) через второй элемент 3И 46 и второй элемент 2ИЛИ 32 подается на второй 33 и третий 34 элементы 2И, Через второй элемент 2И 33 проходит пачка импульсов кварцевои частоты, количество которых пропорционально длительности импульса управления, и подсчитывается на двоичном счетчике 19. САормированный код числа с двоичного счетчика 19 через коммутатор 22, открытьл по второму и-Разрядному входу, блок 23 эле- 20 ментов НЕ подается параллельно обратным кодом на вход предварительной записи двоичного счетчика 24 с предварительной записью инАормации, В течение этого же импульса управления пач- 25

1 ка импульсов с выхода Аормирователя

8 импульсов через третий элемент 2И

34 поступает по входу вычитания на реверсивный счетчик 14. По окончании импульса управления на реверсивном счетчике 14 Аормируйтся обратный код числа, пропорционального набегу разности Ааз между управляемым генератором 1 и эталонным генератором 7 за время импульса управления, По спаду импульса управления через второй элемент HF. 43 третий

Аормирователь 44 Аормирует импульс сброса (Аиг.5g), который через пятый элемент 2И 40 и третий элемент 2ИЛИ

37 переводит второй 38 и третий 48 триггеры в нулевое состояние (фиг.56, $), запрещающее прохождение импульсов управления через второй элемент

ЗИ 46, Напряжением с инверсного вы- 45 хода второго триггера 38 разрешается прохождение импульсов кварцевого генератора 11 через четвертый эле- мент 2И 39 на входы счетчикового делителя 16 с переменным коэффициен50 том деления и двоичного счетчика 24 с предварительной записью инАормации.

Импульс переполнения с выхода двоичного счетчика 24 с предварительной записью информации через элемент 25 задержки на половину периода кварце55 вой частоты подается обратно как импульс записи предварительной информации. Таким образом, в двоичном счетчике 24 с предварительной записью инАормации счет ведется от числа, пропорционального длительности импульса управления t< и записанного в обратном коде, до переполнения и так до окончания цикла измерения., воично-десятичный счетчик 26 производит подсчет импульсов переполнения.

Через счетчиковый делитель 16 с коэфАициентом деления К импульсы кварцевой частоты поступают на суммирующий вход реверсивного счетчика

14. Импульс переполнения с реверсивного счетчика 14 (Аиг. 56) через четвертый элемент 2ИЛИ 42 переводит второй триггер 38 в единичное состояние, закрьгвая прохождение импульсов кварцевой частоты и разрешая прохождение очередного импульса управления. Так как время до переполнения .реверсивно-го счетчика 14 пропорционально АазоBoMv набегу d CP сигнала, то число импульсов переполнения двоичного счетчика 24 за это же время равно

К ° ЕЧ что с масштабным коэффициен и том К соответствует величине девиации частоты. КоэААициент К выбирается из условия согласования полученного значения с разрядами блока 10 индикации и повышения точности измерения, По Аронту переключения второго триггера 38 в единичное состояние второй

Аормирователь 41 Аормирует импульс, по которому информация, накопленная в двоично-десятичном счетчике 26, записывается в блок 27 памяти, соединенный с блоком 10 индикации.

В режиме измерения скорости изменения частоты из импульса управления вырезается строб, управляемый по задержке и длительности, в течение которого измеряется скорость изменения частоты сигнала. В этом режиме на втором выходе Аормирователя 12 сигналов установки режимов измерения напряжения соответствует уровню логической единицы., Аналогично, как и в предыдущем pe å, короткий импульс с первого выхода Аормирователя 12 сигналов установки режимов измерения (Аиг.6Д) переводит второй триггер 38 в единичное состояние (фиг.65), разрешая прохождение импульса через шестой элемент 2И 47, По Аронту импульса управления (Аиг.66) четвертый формирователь

45 формирует импульс (Аиг.62), кото

1711087 рый через шестой элемент 2И 47 третий триггер 48 переводит к единичное состояние (Лиг,6 ), четвертый триггер

4R - в нулевое состояние и через пятый элемент 2ИЛИ 51 записывает инфор5 мацию с первого п-разрядного выхода формирователя 57 кодов через открытый по первому входу коммутатор 55 и блок

54 элементов HF, в счетчик 53 с предварительной записью информации, Триггер 48 разрешает прохождение импульсов через пятью элемент 2И 40 и третий элемент ЗИ 52. Через третий элемент

ЗИ 52 начинают поступать импульсы кварцевой частоты (фиг. Е4 на счетный вход счетчика 53 с предварительной записью информации. Импульсом переполнения с выхода счетчика 53 (Лиг.6 ) .четвертый триггер 49 по счетному входу переводится в единичное состояние (фиг.6И), переключая коммутатор 55 на прием информации по второму входу.

Этим же импульсом переполнения через элемент 50 задержки на половину периода кварцевой частоты записывается информация с второго а-разрядного выхода формирователя 57 кодов .через коммутатор 55 и блок 54 элементов HF. в счетчик 53 с предварительной запи- 30 сью ин*ормации.

Второй импульс переполнения с выхода счетчика 53 (фиг,6)) переводит четвертый триггер 49 в нулевое состо35 яние (фиг.бц}. Таким образом, на выходе четвертого триггера 49 формируется строб, фронт которого задержан от фронта импульса управления на время, пропорциональное набранному коду по первому выходу формирователя 57 кодов, и длительность которого пропорциональна коду по второму выходу.

Сформированньп строб с выхода четвертого триггера 49 подается на первьп элемент ЗИ 28 и через первый элемент-ПЕ 35 на первый элемент 2И

29, Первый после фронта строба четвертого триггера 49 импульс с выхода формирователя 8 импульсов (фиг.6К)

50 через первый элемент ЗИ 28 переводит первьп триггер 31 в единичное состояние и первым после спада строба через первый элемент 2И 29 и первый элемент 2ИЛИ 30 в нулевое состояние (фиг,6А). Т.е. на выходе первого .55 триггера 31 формируется строб, жестко привязанный к импульсам формирователя 8 импульсов, По спаду строба с выхода первого триггера 31 первый формирователь 36 формирует импульс, который через третий элемент 2ИЛИ 37, второй триггер

38 (фиг. 65) и третий триггер 48 (фиг.6$) переводит в нулевое состояние,.закрывая прохождение импульсов через шестой элемент 2И 47, второй элемент ЗИ 46 и третий элемент ЗИ 52, Через второй элемент 2ИЛИ 32 строб с выхода первого триггера 31 подается на второй 33 и третий 34 элементы

2И, дальнейшая работа устройства аналогична работе в режиме измерения девиации за исключением того, что в двоичный счетчик 24 с предварительной записью информации записывается в обратном коде число, пропорциональное квадрату времени длительности строба измерения. Для этого инфор( мация, накапливаемая в двоичном счетчике 19, параллельнь|м кодом подается на первый вход сумматора 20,-причем первый разряд с выхода двоичного счетчика 19 подается на вход второго разряда сумматора 20, выход а-го разряда - на вход и+1-го разряда. На первый разряд первого входа сумматора

20 подается напряжение постоянного уровня логической единицы. Так как такт записи в накопитель 21 опережает такт"счета двоичным счетчиком 19 на половину периода кварцевой частоты за счет включения элемента 18 задержки в цепь двоичного счетчика l9 в сумматоре 20 складывается увеличенное на две единицы значение числа двоичного счетчика 19 с предыдущим результатом суммы, что соответствует получению квадрата числа двоичного счетчика 19. С выхода накопителя 21 через открытый по первому входу коммутатор 22, блок 23 элементов НЕ информация, пропорциональная квадрату времени длительности строба измерения, в обратном коде подается на дво ичный счетчик 24 с предварительной записью информации.

Для согласования полученного значения с разрядами блока индикации в режиме измерения скорости изменения частоты пропорционально изменяется коэффициент деления К счетчикового делителя 16 с переменным коэффициентом деления.

9 171 i087

Формула изобретения

1. Устройство для измерения девиации частоты линейно-частотно-модули5 романного колебания, содержащее последовательно соединенные управляемый генератор, фазовый детектор, ключ, фильтр нижних частот, усилитель постоянного тока, выход которого соеди- 1ð нен с первым входом управляемого генератора„ второй вход которого соединен с выходом генератора пилообразного напряжения, эталонный генератор, вы.-.ход которого соединен с вторым входом 1 фазового детектора, последовательно соединенные формирователь импульсов, вход которого соединен с выходом фазового детектора, блок нормирования и блок индикации, выход кварцевого генератора соединен с вторым входом блока нормирования, второй вход ключа, вход генератора пилообразного напряжения, третий вход блока нормирования соединены с шиной импульса 25 управления, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных .возможностей путем обеспечения измерения скорости изменения линейно-частотно-модулированного колебания, в него введены формирователь сигналов установки режимов измерения, первый выход которого соединен с четвертым входом блока нормирования, а второй выход с пятым входом блока нормирования и вторым входом блока индикации.

2, Устройство по и. 1, о т л и— ч а ю щ е е с я тем, что Ьормирователь сигналов содержит формирователь 4О импульса, вход которого соединен с выходом переключателя, первый и второй входы которого соепинены соответственно с потенциалами логического нуля и епиницы R ВыхОд является пер 4 вым выходом формирователя сигналов, вторым выходом которого является вход формирователя импульса..

3, Устройство Ilo II 1, 0 T JI H ч а ю щ е е с я тем, что блок нормирования содержит блок управления, реверсивный счетчик; двоичный счетчик, блок элементов НЕ, двоичный счетчик с предварительной записью информации, элемент задержки, двоично-десятичный счетчик, блок памяти, выход которого является выходом блока нормирования, а информационные входы соединены с соответствующими выходами двоично-десятичного счетчика, первый выход блока управления соединен с входом вычитания реверсивного счет тика, четвертый выход блока управления соединен с входами установки в "0" реверсивного счетчика, двоичного счетчика, двоичного счетчика с предварительной записью информации, двоично-десятичного счетчика, пятый выход блока управления соединен с первым входом PJloza памяти, третий выход блока управления соединен с первым входом двоичного счетчика с предварительной записью информации, первый, второй и третий входы блока управления являются соот" ветственно первым, вторым и третьим входами блока нормирования, и-разрядный параллельный выход блока элементов HE соединен с и-разрядным параллельным входом,двоичного счетчика с предварительной записью информации, выход которого соединен с входом двоично-десятичного счетчика, выход первого элемента задержки соединен с вторым входом двоичного счетчика с предварительной записью информации, введены соединенные последовательно блок установки коэффициента деления и счетчиковый делитель с переменным коэффициентом деления, соединенные последовательно логический сумматор, накопитель и коммутатор, второй и третий элементы задержки, причем четвертый вход блока нормирования соединен с шестым входом блока управления, пятый вход блока нормирования соединен с пятым входом блока управления и управляющими входами блока установки коэффициента деления и коммутатора, вход второго элемента задержки соединен с выходом счетчикового делителя с переменным коэффициентом деления и суммирующим входом реверсивного счетчика, выход второго элемента задержки соединен с вторым входом счетчикового делителя с переменным коэффициентом деления, вход третьего элемента задержки соединен с вторым выходом блока управления и входом тактирования накопителя, а выход — со счетным входом двоичного счетчика, первый вход счетчикового делителя с переменным коэффициентом деления соединен с третьим входом блока управления, первый (о+1)-разрядный параллельный вход логического сумматора соединен с и-разрядным па1711087

12 раллельным выходом двоичного счетчика и вторым и-разрядным параллельным входом коммутатора, причем первый разряд двоичного счетчика соединен с вторым разрядом входа логического сумматора, второй — с третьим и-й— с (и+1)-ым, а первый — с шиной нап-ряжения логической единицы, второй -разрядный параллельный вход сумматора соединен с и-разрядным параллельым выходом накопителя, и-разрядный араллельный выход коммутатора соедиен с и-разрядным параллельным входом лока элемента HF,,íõîäû установки

"О" накопителя и счетчикового делиеля с переменным коэффициентом делеия соединены с четвертым выходом блока управления, вход первого элемента задержки соединен с выходом двоичного счетчика с предварительной записью информации.

4, Устройство по и. 1, о т л и— ч а ю щ е е с я тем, что в блок упавления, содержащий первьп -четвертый 25 элементы 2И, первый и второй формирователи, элемент HF., дополнительно введены первый-третий элементы ЗИ, первых и второй элементы 2И, первый-пятый элементы 2ИЛИ, третий и четвертый фор-щО мирователи, второй и третий элементы

HF. первый-четвертый триггеры, элемент задержки, счетчик с предварительной записью информации, блок элементов

НЕ, коммутатор, формирователь кодов, причем первьп вход блока управления соединен с третьим входом первого элемента ЗИ, первым входом первого элемента 2И и вторым входом третьего элемента 2И, второй вход блока управления соединен с первым входом второго элемента 2И, первым входом четвертого элемента ?И и вторым входом третьтретьего элемента ЗИ, третий вход бло» ка управления соединен с входом второго элемента HF., первым входом второго элемента ЗИ и входом четвертого формирователя, четвертый вход блока управления соединен с вторым входом четвертого элемента 2ИЛИ, пятый вход блока управления соединен с первым входом первого элемента ЗИ, с входом третьего элемента HE и третьими входом третьего элемента ЗИ, шестой вход блока чправления соединен с первым

55 входом четвертого элемента 2ИЛИ, выход первого элемента ЗИ соединен с входом установки в "1" первого триг« гера выход первого элемента 2И соеФ динен с первым входом первого элемента 2ИЛИ, выход первого элемента 2ИЛИ

tl 1I соединен с входом установки в О первого триггера, выход первого триггера соединен с первым входом второго элемента 2ИЛИ и входом первого формирователя, выход второго элемента 2ИЛИ соединен с вторым входом второго элемента 2И и первым входом третьего элемента 2И, выход второго элемента 2И является вторым выходом блока управления, выход третьего элемента 2И является первым выходом блока управления, выход первого элемента HE соединен с вторым входом первого элемента

2И, выход первого формирователя соединен с первым входом третьего элемента 2ИЛИ, выход третьего элемента

2ИЛР соединен с входами установки в

"0" второго и третьего триггеров, выход второг триггера соединен с входом второго формирователя и первым входом шестого элемента 2И, инверсный выход второго триггера соединен с вторым входом четвертого элемента

2И, выход четвертого элемента 2И является третьим выходом блока управления, выход второго Аормировате. ы является пятым выходом блока управления, выход пятого элемента 2И соединен с вторым входом первого элемента 2ИЛИ и вторым входом третьего элемента 2ИЛИ, вьг од четвертого элемента 21ШИ соединен с входом установки в "0" второго триггера, выход второго элемента НЕ соединен с входом третьего *ормирователя, выход третьего формирователя соединен с первьпч входом пятого элемента 2И, выход второго элемента ЗИ соединен с вторым входом второго элемента

2ИЛИ, выход четвертого формирователя соединен с вторым входом шестого ет те элемента 2И, входом установки в О четвертого триггера и первым входом пятого элемента 2ИЛИ, выход шестого элемен та 2И соединен с входом устанонки в " 1 " третьего триггер а и является четвертым выходом блока управления, выход третьего триггера с оедин ен с вторым входом пятого элемента 2И, третьим входом второго элеме нт а ЗИ и пе рвым входом третьего элемента ЗИ выход четвертого триг гер а соединен с вторым входом первого элемента ЗИ, входом первого элемента

НЕ и с управляюцим входом к оммутатора, выход пятого элемента 2ИЛИ сое13

1711087

10

9 ) Фиг.2 динен с входом разрешения записи, предварительной ш формации счетчика с предварительной записью информации, выход счетчика соединен со счетным входом четвертого триггера и входом элемента задержки, выход элемента задержки соединен с вторым входом пятого элемента 2ИЛИ, выход третьего элемента ЗИ соединен со счетным входом счетчика с предварительной записью информации, выход третьего элемента НЕ соединен с вторым входом второго элемента ЗИ, первый и второй и-разрядные выходы формирователя кодов соединены соответственно с первым и вторым и-разрядными входами коммутатора, и-разрядный выход коммутатора через блок элементов НЕ соединен с и-разрядным входом счетчика с предварительной записью информации.

1711087

1711087

Юиацис/ частОты цикл измерения

Фиг. 5 (, I

1 >

I цикл измерения I фиг 6

Редактор В. Данко

Заказ 337 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

6 г1

Режим измерения скорости изменения частоты

Составитель Е, Соловьев екред М.Моргентал КорректорЛ. Пилипенко