Измеритель девиации частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может использоваться для определения параметров частотно-модулированного сигнала. Целью изобретения является повышение точности изменения. Измеритель девиации 4ac-t тоты содержит вход 1, формирователь 3, элемент 4 совпадения, счетчик 5, блок 6 сравнения кодов, регистр 11, блок 12 деления, блок 13 индикации, блок 16 сравнения кодов, блок 17 управления и генератор 18 опорной частоты . Введение линии 2 задержки, триггеров 7 и -8, ключа 9, счетчика 10, ключа 14 и сердечника 15 позволяет повысить точность измерения пикового значения девиации частоты при несимметричной модуляции, а также определять значение частоты модуляции. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (S>)S " 01 Р, 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTGPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4777083/21 (2 ) 02.01.90 (46) 07.02.9?. Бюл. Г - 5 (71) Омский политехнический институт (72) И.И. Вешкурцев и Ю.И. Сысоев (53) 621. 317 (088. 8) (56) Авторское свидетельство СССР

1337796, кл. 0 01 R 23/00, 1987.

Авторское свидетельство СССР

Р 575578, т:л. С 01 Р, 23/00, 1977, (54) И31П,РИТЕЛЬ 71ЕВИАЦИИ пАСТОТЫ (57) Изобретение относится к измерительной технике и может использоваться для определения параметров частотно-модулированного сигнала. Целью

„„SU„„1711088 А 1 изобретения является повьппение точности изменения. Измеритель девиации частоты содержит вход 1, формирователь

3, элемент 4 совпадения, счетчик 5, блок 6 сравнения кодов, регистр 11, блок 12 деления, блок 13 индикации, блок 16 сравнения кодов. блок 17 управления и генератор 18 опорной частоты.Введение линии 2 задержки, триггеров 7 и 8, ключа 9, счетчика 10, ключа 14 и сердечника 15 позволяет повысить точность измерения пикового значения девиации частоты при несимметричной модуляции, а также определять значение частоты модуляции. 2 ил.

17 11000

Наиболее близким техническим решением к изобретению является измеритель девиации частоты, содержащий включенные последовательно вход из- 25 мерителя, формирователь, элемент совпадения, счетчик, первый блок срав.нения кодов, а также включенные последовательно второй блок сравнения кодов, регистр, вычислительное устройство и блок индикации, второй вход которого попключен к третьему выходу ,блока управления, у которого первый r1 1t выход присоеринен к входу Сброс сче1чика, второй выход — к третьему входу вычислительного устройства, первый вход — к выходу формирователя, и генератор опорной частоты, выход которого присоединен к свободному входу элемента совпадения и к 10 второму входу блока управления, тогда как первый и второй входы второго блока сравнения кодов подключены соответственно к первому входу и выходу, регистра. Работа этого устройства заключается в том, что в течение измерительного цикла оно выделяет Н „ и

N импульсов, пропорциональных

1 ма к соответственно девиации круговой частоты вверх" и девиации круговой час- 50 тоты "вниз", которые могут быть вычислены по формулам вира (1)

Щ в б о)>+4 )о (м

t Pe ЬЯв - девиациЯ кРУговой частоты

"вверх";

ЬОя — девиация круговой частоты

"вниз";

Изобретение относится к измерительной технике и может быть использовано при измерении девиации частоты.

Известны измерители девиации час5 тотьма, преобразующие входной частотномодулированный сигнал в последовательность прямоугольных импульсов, дли-: тельность которых пропорциональна закону модуляции. Е примеру, известно устройство, которое содержит формирователь, два вентиля, два счетчика, блок вычитания, селектор, накапливающий сумматор, вычислительный блок, блок индикации и блок управления. При 15 г роведении измерений устройство определяет среднее значение девиации час1 оты, что обусловливает его высокую точность при любом отклонении закона модуляции от заданного закона. 20

Ыв — круговая частота в отсутствии модуляции;

Π— верхняя составляющая спектв ра сигнала с частотной модуляцией;

5, — нижняя составляющая спектра н сигнала с частотной модуляцией.

В известном измерителе число импульсов и экстремальные составляющие спектра сигнала связаны соотношениями рО. / и И (2, 0 мин -,,ó f ìàêñ Т . б) 1(- ая 6 on я гре 7 — период частоты опорного геоя нератора.

Производимые преобразования в вычислительном устройстве ие позвопяют выделить значения Üß и h(i)tt, à результат выдается в вире пик а ь + (Н (3)

Используя известное соотношение 660

= 2 > 6 f, выражение (3) может быть в"писано как

ЬС, + h <

< n„< — — . (4) Недостатком измерителя является следующее, При условии ЬОв Ф ЬЮн, т,е. несимметричной модуляции, возникает погрешность в вычислении реального пикового значения девиации частоты. Например, пусть параметры частотно-модулированнoFo колебания имеют следующие значения: Ь |Н

100 Гц, Ь 1 g = 1000 Гц. Тогда по формуле (4) Ь Г << = 550 Гц, что не соответствует реальному пиковому значению, равному 1000 Гц, а погрешность измерения при этом составит. 55Õ.

11ель изобретения — повышение точности измерения девиации частоты.

Указанная цель достигается тем, что в измеритель девиации частоты, содержащий включенные последовательно вход устройства, Йормирователь, элемент совпадения, счетчик и первый блок сравнения кодов, а также включенные последовательно второй блок сравнения кодов, регистр, вычислительное устройство и блок индикации, вто рой вход которого подключен к третьему выходу блока управления, у которого первый выход присоединен к входу

"Сброс" счетчика, второй выход — к

1711088

I модулированное колебание 0 (фиг, 2), например, вида второму входу вычислительного устройства, а первьп вход - к выходу формирователя, и генератор опорной частоты, выход которого присоединен к свободному входу элемента совпадения и к второму входу блока управления, тогда как первый и второй входы второго блока сравнения кодов подключены, соответственно, к первому входу и вы-10 ходу регистра, введены линия задержки и две идентичные цепи из последовательно включенных триггера, ключа и счетчика импульсов, выход которого подключен к первому входу регистра, третий вход которого одновременно приприсоединен к шине "Сброс" счетчика первой цепи и к первому выходу блока управления. Выход счетчика второй цепи подключен к второму входу вычислительного устройства и к второму .входу первого блока сравнения кодов, выход которого подключен к счетному входу триггера каждой цепи, Р-вход триггера первой из которых присоеди- 25 нен к первому выходу блока управления, à S-вход и Р-вход триггера второй цепи подключены, соответственнок второму и четвертому выходам блока управления, второй выход которого присоединен к входу Сброс" счетчика второй цепи, н которой свободный вход ключа присоединен к выходу элемента совпадения, а выход ключа —— к свободному входу ключа первой це35 пи. Между двумя входами Формирователя попключена линия задержки, Использование новых блоков позволяет осуществить преобразование частота-Ьазовьп". сдвиг-интервал времени и провести измерения максимальных значений Фазовых сдвигов вместо измерения минимальных и максимальных значений частоты при преобразовании частота-.интервал времени. На- 45 личие максимальных фазовых сдвигов значительно повьппает точность измерения пикового значения девиации частоты даже при условии ЬЯц Ф ЬЯн .

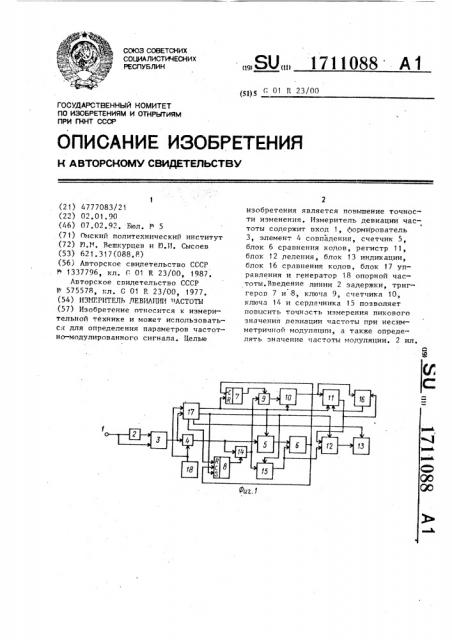

На Фиг. 1 пРедставлена структур ная схема измерителя девиации частоты; на Фиг. 2 — временные диаграммы, поясняющие работу измерителя.

Измеритель девиации частоты содержит включенные последовательно вход 1, линию 2 задержки, формирователь 3, элемент 4 совпадения, счетчик 5 импульсов, первьп1 блок 6 сравнения кодов, выход которого подключен к счетному входу триггеров 7 и 8, кроме того, линия 2 задержки включена между первым и вторым входами формирователя 3, Триггер 7, ключ 9 и счетчик 10 образуют первую цепь, выход которой подключен к последовательному соединению регистра 11, блока 12 деления и блока 13 индикации. Выход второй цели, образованной триггером

8, ключом 14 и счетчиком 15, присоединен к второму входу первого блока

6 сравнения кодой и второму входу блока 12 деления ° К второму входу ключа 9 присоединен выход ключа 14, у которого второй вход подключен к выходу элемента 4 совпадения. К первому входу регистра 11 подключен выход блока 16 сравнения кодов, первый и второй входы которого присоединены .соответственно, к второму входу и выходу регистра 11. Выход формирователя 3 подключен к первому входу блока 17 управления, второй вход которого подключен к второму входу элемента 4 совпадения и выходу генератора 18 опорной частоты. Первый выход блока 17 управления подключен к

Р-входу триггера 7, входам сброса счетчиков 5 и 10, регистра 11, второй выход — к S-входу триггера 8, входаМ сброса счетчика 15 и блока 12 деления, третий вьгход — к второму входу блока 13 индикации, а четвертый выход — к Р-входу триггера 8.

С целью еткого изложения последующего материала обозначим низкий потенциал — логическим нулем ("Лог.0"),а высокий потенциал — логической единицей (Лог. 1").

Измеритель работает следующим образом.

Момент начала измерения фиксирует" ся импульсом с первого и второго выходов блока 17 управления (фиг,22>

g). Этот импульс является установочным для счетчиков 5, 10, 15, регистра 11, триггера 7, блока 12 деления, на инФормационных выходах которых присутствует "Лог. 0". При этом выходной сигнал триггера 8, блоков 6 и 16 сравнения кодов равен "Лог. 1".

В этот же момент времени и блоке 12 деления формируются постоянные коэфг A фициенты -2 и и ь, где ь — постоянл ная времени линии 2 задержки.

Поступающее на вход 1 частотно Ы

U =П sin t + sinQt, (5) ех о где И вЂ” амплитуда несущего колео бания;

5 (j} = f 2п — круговая частота несущей о о частотно-модулированного колебания;

ЬЫ = АГ 2 и — девиация круговой частоо ты частотно-модулированного колебания;

Ч7 = f 2 Ф- круговая частота модуляМ ции частотно-модулированного колебания, с помощью 1линии 2 задержки задержиЬ

Л вается во времени на интервал

Следовательно, на выходе линии 2 задержки сигнал имеет вид

U =U sin Я (t- (, )+ — sin(t-ь) gg, (б) и Ь(} . и 1 20 е о о Q.

На выходе формирователя 3 с учетом л компенсации им фазового сдвига 030 ь при поступлении двух сигналов (5) и (6) появляется импульс 6 (Ьиг.2).

Этот импульс поступает в блок 17 управления и открывает элемент 4. ерез элемент 4 и ключ 14 импульсы генератора 18 подсчитываются счетчикями 5 и 15 (*иг.2ж,g). После окончания импульса о (фиг.2) элемент 4 закрывается и работа счетчиков прекращается.

В этот момент времени на первом и четвертом выходах блока управления

Формируется импульс 8 (Фиг.2д), кото35 рый устанавливает счетчик 5 в исходное состояние, а выходной потенциал триггера 8 в "Лог. О". Ключ 14 закрывается. Таким образом, в течение одного периода исследуемого колебания в счетчике 15 оказывается записанным число импульсов И,5, пропорциональное мгновенному значению фазового сдвига двух сигналов (5) и (6), а именно

Б Чм (0с - 2н Ьf (7)

Во второй период колебаний исследуемых сигналон Формирователь 3 вы50 рабатынает импульс 4 (Ьиг. 2), длительность которого пропорциональна новому мгновенному фазовому сдвигу

Этот импульс поступает в блок, 17 управления и открывает элемент 4, Теперь работает только счетчик 5, 55 так как в препыдущем периоде "Лог.О" с выхода триггера 8 закрыл ключ 14.

Такое состояние сохраняется до тех и д =Яма Жиги, = ® = (i - <> To

2и Т сg Т (8} где Т вЂ” период несущей частоты часО тотно-модулированного колебания.

Если последующие значения мгновенных Фазовых сдвигов оказываются меньше предыдущих, то выходной сигнал блока 6 сравнения не воздействует на триггера 7 и 8, и выходной сигнал блока 16 сравнения не переходит из состояния "Лог. О" в "Лог. 1". Тем самым, за время измерения, определяемое импульсами (Аиг. 2), фиксируются максимальное значение 0 5 и максимальное значение П <, равные (7) пор, пока на счетный нход триггера 8 не поступит переход тактового сигнала из "Лог. О" н "Лог. 1" с выхода первого блока 6 сравнения кодов (фиг. 2g). Как только счетчиком 5 будет заЬиксировано число импульсов, равное предыдущему результату измерения, Фронт импульса. при переходе из "Лог.О" в "Лог. i" с блока 6 переволит триггера 7 и 8 в состояние

"Лог. 1". Ключ 14 открывается и последующие импульсы доэаписываются в счетчик 15, т.е. N<< увеличивается (Ьиг,2 }. Ключ 9 также открывается и эти же импульсы записываются н счетчик 10 (Фиг. 2 }.

После окончания импульса о (фиг. 2) элемент 4 закрывается, и работа счетчикон 5, 15, 10 прекращается. Блок управления выдает сигнал g (Жыг.2ф), который переписывает цифровой коп в регистр 11 (фиг.2А) из счетчика 10 по разрешающему состоянию "Лог. 1" с выхода блока 16, а также устанавливает счетчики 5 и 10 в исходное состояние и выходной сигнал триггеров 7 и 8 н состояние "Лог, О". Выход блока 16 сравнения, Фиксирующий результат сравнения — больше или равно, переходит н состояние "Лог. О", так как цифровой код на первом входе оказался меньше, чем циЬровой код на втором входе блока 16 сравнения.

Количество импульсов, заЬиксиронанное н регистре 11, пропорционально разности между последующим и предыдущим мгновенным Ьазовым сдвигом, а именно

1О

1 11088

Il ото

4fqgg (9) 10 (10)

25 и (8). По окончании времени измерения эти значения поступают в блок 12 деления, который обеспечивает определение пикового значения девиации частоты по входным результатам М< и

Е в соответствии с формулой где 11отн N« NI(После вычисления результат регистрируется в блоке 13 индикации и не меня-ет своего значения до появления нового результата вычисления по формуле 15

- (9).

Предложенный измеритель отличается от известного еще и тем, что позволяет расширить его функциональные возможности. Данным измерителем можно 20 определить частоту модуляции из соотношения

Причем постоянный коэЬфициент Т может быть установлен в блоке 12 дел пения так же, как 2 и и

Блок 12 деления может быть выполнен на интегральных схемах серий 30

К155, К133, К556, К589, либо в виде микро-ЭВИ, построенной на базе микропроцессорного комплекта К588, Формирователь 3 может быть построен с использованием известных принци- 35 пов преобразования, как, например, это сделано в отчете о ПИР.

В качестве линии 2 задержки может быть использована линия задержки на приборах с зарядовой связью (ПЗС), 40 дискретная линия задержки (ДЛЗ),кварцевая и др.

Остальные функциональные узлы измерителя могут быть выполнены на интегральных схемах серий К155 К133. 45

Использование преобразования частота — базовый сдвиг — интервал времени позволяет значительно повысить точность измерения пикового значения девиации частоты при неравенстве Я Ф 50

- АО, 1! р и м е р. Пусть сохраняются условия Ь Г я = 100 Гц, A f = 1000 Гц.

Тогда измеритель, в соответствии с

Формулой (9), выдает значение hfdf = 55

1000 Гц, т,е. максимальное значениедевиации .частоты. При этом погрешность измерения пикового значения певиации частоты составит 07,. Следовательно, предлагаемый измеритель существенно повышает точность измерения пикового значения девиации частоты.

Формула изобретения

Измеритель девиации частоты, содержащий последовательно соединенные формирователь, первый вход которого явлется входом устройства, элемент совпадения, первый счетчик и первый блок сравнения кодов, последовательно соединенные второй блок сравнения кодов, регистр, блок деления и блок индикации, а также блок управления и генератор опорной частоты, выход которого подключен к второму входу элемента совпадения, причем первый и второй входы блока управления подключены, соответственно, к первому и второму входам элемента совпадения, а первый, второй и третий выходы блока управления соединены соответственно с входами сброса первого счетчика, блока деления и вторым входом блока индикации, первый и второй входы второго блока сравнения кодов подключены соответственно к второму входу и выходу регистра, отличающийся тем, что, с целью повышения точности измерения, в него дополнительно введены линия задержки, последовательно включенные первый триггер, первый ключ и второй счетчик, выход которого соединен с вторым входом регистра, а также последовательно включенные второй триггер, второй ключ и третий счетчик, выход которого объединен с вторыми входами первого блока сравнения кодов и блока деления, причем входы сброса регистра, первого и второго счетчиков объединены с R-входом первого триггера, счетный вход которого подключен к выходу первого блока сравнения кодов и счетному входу второго триггера, второй выход блока управления объединен с входом сброса третьего счетчика и S-входом второго триггера, Р-вход которого подключен к четвертому выходу блока управления, второй вход второго ключа соединен с входом первого счетчика, а выход— с вторым входом первого ключа, вход и выход линии задержки подключены соответственно к первому и второму входам формирователя.

1711083

Составитель И. Вешкурцев

Техред М.Моргентал . Корректор Л.Пилипенко

Редактор В.,Панко

Заказ 337 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101